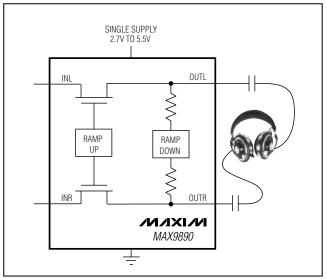

#### **General Description**

The MAX9890 provides click-and-pop suppression for devices such as CODECs with integrated headphone amplifiers that lack a clickless/popless startup/power-up or shutdown/power-down. The device controls the ramping of the DC bias voltage on the output-coupling capacitors and the application of the audio signal to ensure that no audible transients are present at the headphones. The MAX9890A features a 200ms startup time for use with up to 100 $\mu$ F coupling capacitors. The MAX9890B features a 330ms startup time for use with greater than 100 $\mu$ F coupling capacitors.

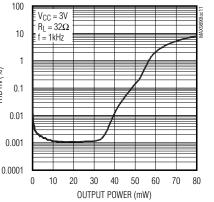

The MAX9890 consumes 14µA of supply current and 0.001µA in shutdown, while contributing less than 0.003% THD+N into a 32 $\Omega$  load. ESD (Human Body Model) protection circuitry on the outputs protect the MAX9890 and devices further up the signal chain from ESD strikes up to ±8kV.

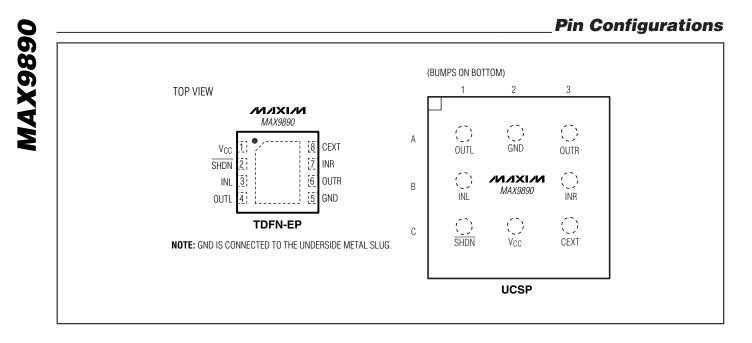

The MAX9890 is available in a miniature (1.5mm  $\times$  1.5mm  $\times$  0.6mm) 9-bump chip-scale package (UCSP<sup>TM</sup>), as well as an 8-pin TDFN package (3mm  $\times$  3mm  $\times$  0.8mm), and is specified for operation over the -40°C to +85°C extended temperature range.

| High-End Notebook Audio | PDAs        |

|-------------------------|-------------|

| Portable DVD Players    | Cell Phones |

| Portable MP3 Players    |             |

#### Simplified Block Diagram

**Applications**

UCSP is a trademark of Maxim Integrated Products, Inc.

####

\_Features

- ♦ 36dB Click-Pop Suppression

- ♦ 2.7V to 5.5V Single-Supply Operation

- Clickless/Popless Startup/Power-Up and Shutdown/Power-Down

- 0.001µA Low-Power Shutdown Mode

- ♦ THD+N < 0.003% Into 32Ω

- ±8kV ESD Protected Outputs (Human Body Model)

- Requires Only One 0.1µF Capacitor to Complete the Circuit

- Low 14µA Supply Current

- Tiny Packaging

9-Bump UCSP (1.5mm x 1.5mm x 0.6mm)

8-Pin TDFN (3mm x 3mm x 0.8mm)

| PART          | TEMP RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |

|---------------|----------------|-----------------|-------------|

| MAX9890AEBL-T | -40°C to +85°C | 9 UCSP-9        | ADV         |

| MAX9890AETA   | -40°C to +85°C | 8 TDFN-EP**     | AHA         |

| MAX9890BEBL-T | -40°C to +85°C | 9 UCSP-9        | ADW         |

| MAX9890BETA   | -40°C to +85°C | 8 TDFN-EP**     | AHB         |

\*\*EP = Exposed pad.

#### **Selector Guide**

| PART          | PIN-PACKAGE | SWITCH TURN-ON<br>TIME (ms) |

|---------------|-------------|-----------------------------|

| MAX9890AEBL-T | 9 UCSP-9    | 200                         |

| MAX9890AETA   | 8 TDFN-EP   | 200                         |

| MAX9890BEBL-T | 9 UCSP-9    | 330                         |

| MAX9890BETA   | 8 TDFN-EP   | 330                         |

Typical Application Circuit and Pin Configurations appear at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **MAX9890**

#### **ABSOLUTE MAXIMUM RATINGS**

(All Voltages are Referenced to GND)

| (                                          |                                  |

|--------------------------------------------|----------------------------------|

| V <sub>CC</sub>                            | +6V                              |

| CEXT, SHDN, OUT                            | 0.3V to +6V                      |

| IN                                         | 0.3V to (V <sub>CC</sub> + 0.3V) |

| Continuous Current (IN_, OUT_)             | ±150mÅ                           |

| Continuous Current (All Other Pins)        |                                  |

| Continuous Power Dissipation ( $T_A = +70$ | )°C)                             |

| 8-Pin TDFN (derate 24.4mW/°C above         | +70°C)1951mW                     |

| 9-Bump UCSP (derate 4.7mW/°C abov          | /e +70°C)379mW                   |

|                                            |                                  |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Storage Temperature Range         | 65°C to +150°C |

| Junction Temperature              | +150°C         |

| Lead Temperature (soldering, 10s) | +300°C         |

| Bump Temperature (soldering)      |                |

| Reflow                            | +235°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3V, \overline{SHDN} = V_{CC}, GND = 0, C_{CEXT} = 0.1 \mu F, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 1)

| PARAMETER                                        | SYMBOL          | CONDITIONS                                                                                            |                                 | MIN | ТҮР   | MAX | UNITS |

|--------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------|---------------------------------|-----|-------|-----|-------|

| Supply Voltage Range                             | V <sub>CC</sub> | Inferred from R <sub>ON</sub> test                                                                    |                                 | 2.7 |       | 5.5 | V     |

| Supply Current                                   | Icc             | (Note 2)                                                                                              |                                 |     | 14    | 22  | μA    |

| Shutdown Supply Current                          | ISHDN           | $\overline{SHDN} = GND$                                                                               |                                 |     | 0.001 | 1   | μΑ    |

| Input Voltage Range                              |                 | Inferred from RON tes                                                                                 | t                               | 0   |       | Vcc | V     |

| On-Resistance                                    | Ron             | Over input voltage                                                                                    | $V_{CC} = 5.5V$                 |     | 0.4   | 1   | Ω     |

|                                                  | TON             | range                                                                                                 | $V_{CC} = 2.7 V$                |     | 0.7   | 1.5 | 22    |

| On-Resistance Flatness                           | RFLAT(ON)       | Over input voltage rar                                                                                | nge                             |     | 2     |     | mΩ    |

| Output Discharge Resistance                      | ROUT(DIS)       |                                                                                                       |                                 |     | 220   |     | kΩ    |

| Input Off-Leakage Current                        |                 | $\overline{SHDN} = GND$                                                                               |                                 |     | 0.001 | 1   | μA    |

| V <sub>CC</sub> Power-Down Threshold<br>(Note 3) | Vuvlo           | V <sub>CC</sub> falling                                                                               |                                 |     | 2.5   |     | V     |

| Click-Pop Reduction                              |                 |                                                                                                       |                                 |     | 36    |     | dB    |

| ESD Protection                                   |                 | OUT_, Human Body Model                                                                                |                                 |     | ±8    |     | kV    |

| DYNAMIC                                          |                 |                                                                                                       |                                 |     |       |     |       |

|                                                  |                 | MAX9890A                                                                                              |                                 |     | 200   |     |       |

| Turn-On Time (Note 4)                            | ton             | MAX9890B                                                                                              |                                 | 33  |       |     | ms    |

| Turn-Off Time                                    | tOFF            | (Note 5)                                                                                              |                                 |     | 120   |     | ns    |

| Bandwidth                                        |                 |                                                                                                       |                                 |     | >100  |     | kHz   |

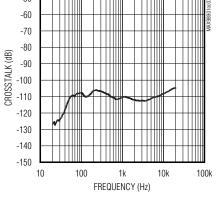

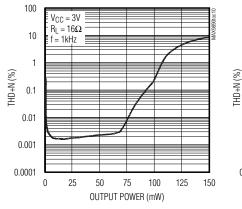

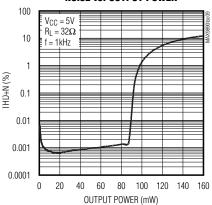

| Total Harmonic Distortion Plus<br>Noise          | THD+N           | $R_L = 32\Omega$ , 30mW, f = 1kHz                                                                     |                                 |     | 0.003 |     | %     |

| Off-Isolation, IN_ to OUT_                       |                 | $f = 20 \text{kHz}, \overline{\text{SHDN}} = \text{GND}, \text{R}_{\text{L}} = 32 \Omega$             |                                 |     | -108  |     | dB    |

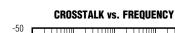

| Crosstalk (Switches ON)                          |                 | f = 20 kHz                                                                                            |                                 |     | -100  |     | dB    |

|                                                  |                 | $V_{\text{RIPPLE}} = 0.5V_{\text{P-P}}$ at 2<br>1 $V_{\text{P-P}}$ , $R_{\text{L}} = 32\Omega$        | 20Hz, f <sub>IN</sub> = 3kHz at |     | -100  |     |       |

| Power-Supply Rejection Ratio<br>(Note 6)         | PSRR            | $V_{\text{RIPPLE}} = 0.5V_{\text{P-P}} \text{ at}^{-1}$<br>$1V_{\text{P-P}}, R_{\text{L}} = 32\Omega$ | 1kHz, f <sub>IN</sub> = 3kHz at |     | -100  |     | dB    |

|                                                  |                 | $V_{RIPPLE} = 0.5V_{P-P}$ at 2 at $1V_{P-P}$ , $R_L = 32\Omega$                                       | 20kHz, f <sub>IN</sub> = 3kHz   |     | -84   |     |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3V, \overline{SHDN} = V_{CC}, GND = 0, C_{CEXT} = 0.1 \mu F, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 1)

| PARAMETER                | SYMBOL | CONDITIONS                     | MIN | TYP | MAX | UNITS |

|--------------------------|--------|--------------------------------|-----|-----|-----|-------|

| LOGIC INPUT (SHDN)       |        |                                |     |     |     |       |

| Logic-Input High Voltage | VIH    | $V_{CC} = 2.7V$ to 5.5V        | 2.0 |     |     | V     |

| Logic-Input Low Voltage  | VIL    | V <sub>CC</sub> = 2.7V to 5.5V |     |     | 0.8 | V     |

| Logic-Input Current      | IIN    |                                |     |     | ±1  | μA    |

Note 1: All devices are 100% tested at  $T_A = +25^{\circ}$ C. All temperature limits are guaranteed by design.

**Note 2:** Supply current is measured when switch is on (i.e.,  $\overline{SHDN} = V_{CC}$ , t > t<sub>ON</sub>).

Note 3: Supply voltage level where the device enters its power-down cycle.

Note 4: Turn-on time is measured from the time  $V_{CC} = 3V$  and  $\overline{SHDN} > V_{IH}$  until the  $R_{ON}$  specification is met.

Note 5: Switch turn-off time is measured from the time SHDN < VIL or V<sub>CC</sub> < V<sub>UVLO</sub> until the off-isolation specification is met.

Note 6: See the Power-Supply Rejection Ratio section for test method.

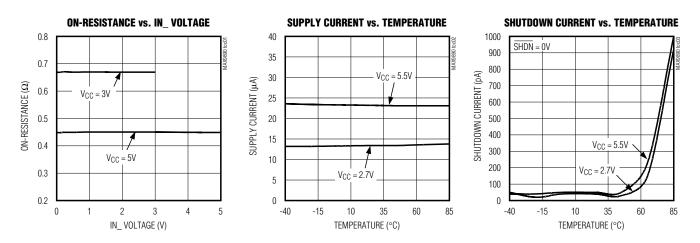

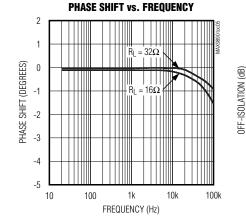

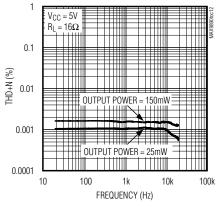

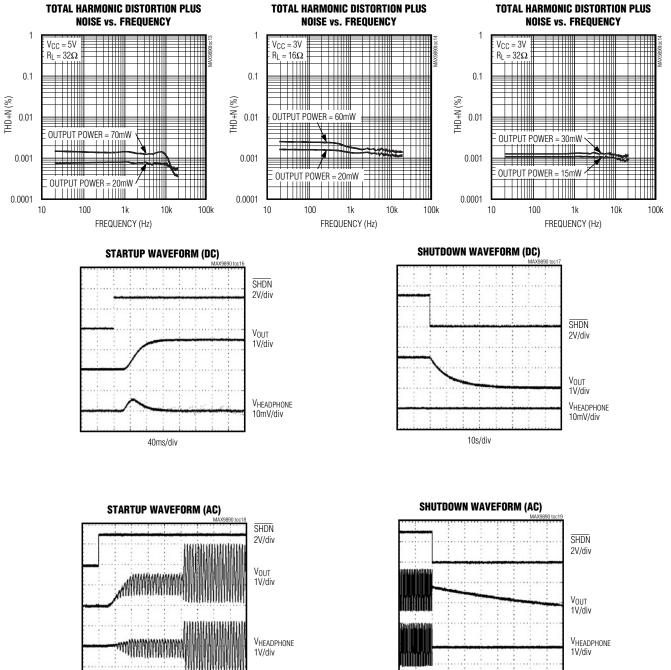

#### **Typical Operating Characteristics**

(V<sub>CC</sub> = 3V, C<sub>CEXT</sub> =  $0.1\mu$ F, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 3V, C<sub>CEXT</sub> =  $0.1\mu$ F, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

**ON-LOSS vs. FREQUENCY** 1.0 0.8 0.6 0.4 (db) SSO1-NO 0.2 0 -0.2 -0.4 -0.6 -0.8

-1.0

10

100

= 320

= 16Ω R

10k

100k

1k

FREQUENCY (Hz)

TOTAL HARMONIC DISTORTION PLUS **NOISE vs. OUTPUT POWER**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY**

/N/IXI/N

0686XAM

1s/div

#### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 3V, C<sub>CEXT</sub> =  $0.1\mu$ F, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

40ms/div

| Pin Description | _ Pin | Description |

|-----------------|-------|-------------|

|-----------------|-------|-------------|

| PIN/E | BUMP | NAME            | FUNCTION                                                                                                                                                 |  |

|-------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TDFN  | UCSP | NAME            | FUNCTION                                                                                                                                                 |  |

| 1     | C2   | V <sub>CC</sub> | Power Supply. V <sub>CC</sub> accepts 2.7V to 5.5V input supply. Bypass V <sub>CC</sub> to GND with a $1\mu$ F capacitor.                                |  |

| 2     | C1   | SHDN            | Active-Low Shutdown. Connect $\overline{SHDN}$ to GND to enter a 0.1µA shutdown mode. Connect $\overline{SHDN}$ to V <sub>CC</sub> for normal operation. |  |

| 3     | B1   | INL             | Left-Channel Audio Input. Connect to output of headphone amplifier.                                                                                      |  |

| 4     | A1   | OUTL            | Left-Channel Audio Output. AC couple to headphone.                                                                                                       |  |

| 5     | A2   | GND             | Ground                                                                                                                                                   |  |

| 6     | A3   | OUTR            | Right-Channel Audio Output. AC couple to headphone.                                                                                                      |  |

| 7     | B3   | INR             | Right-Channel Audio Input. Connect to output of headphone amplifier.                                                                                     |  |

| 8     | C3   | CEXT            | External Capacitor. Connect a 0.1µF capacitor from CEXT to GND.                                                                                          |  |

#### **Detailed Description**

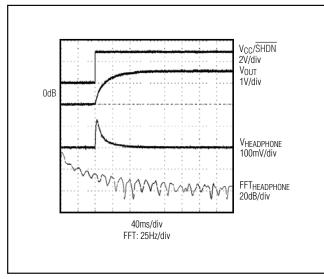

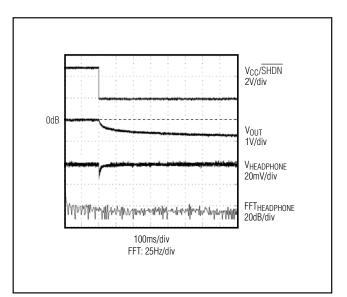

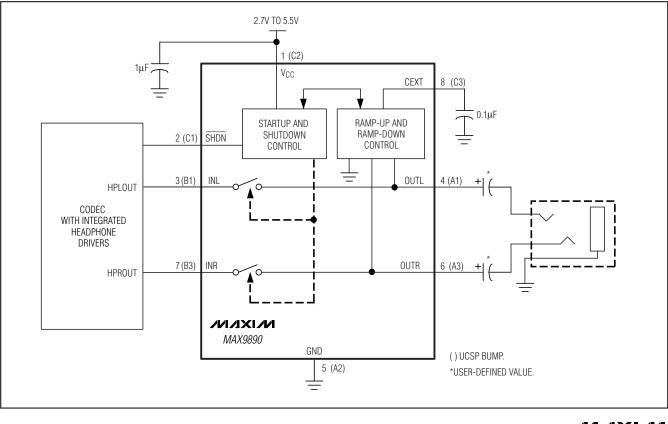

The MAX9890 provides click-and-pop suppression for single-supply devices such as CODECs and other headphone amplifiers that do not have click-and-pop suppression. Single-supply audio amplifier outputs have a DC bias voltage, V<sub>CC</sub> / 2, and require large output-coupling capacitors to block the DC voltage from the speaker. During startup or shutdown, the DC bias voltage is quickly raised or lowered (Figure 1), resulting in an audible transient through the headphone load. The MAX9890 prevents the audible transient by slowly ramping the DC bias in an S-shaped waveform (Figure 2), suppressing the large transient at the output of the coupling capacitor. The S-shaped waveform shapes the frequency spectrum, minimizing the amount of audible components present at the output.

Internal switches couple the inputs to the outputs after the coupling capacitors have fully charged to the input common-mode bias voltage. When power is removed or the device is put into shutdown, the internal switches in the MAX9890 immediately disconnect the output and slowly discharge the coupling capacitors through 220k $\Omega$  resistors.

The MAX9890 has an undervoltage lockout (UVLO) that prevents device operation when V<sub>CC</sub> is below the power-down threshold (2.5V, typ). The MAX9890 features  $\pm$ 8kV ESD (Human Body Model) protection on the audio outputs.

old and SHDN = high for the part to start up. Once the supply voltage is above the power-down threshold and SHDN is high, the device charges the coupling capacitors to the input DC bias voltage using CEXT to control the ramp. After the DC bias ramp, the internal switches close, coupling the audio input to the output. The MAX9890 provides click-pop suppression even if the output blocking capacitors are already partially or fully charged.

The MAX9890A features a 200ms switch turn-on time, enabling the use of up to 100 $\mu$ F coupling capacitors at the output for applications requiring only a limited low-frequency response and a rapid turn-on time. The MAX9890B features a 330ms switch turn-on time, enabling the use of >100 $\mu$ F coupling capacitors at the output for extended low-frequency response applications. For optional click-pop suppression, mute the audio signal until after the turn-on time has elapsed.

The internal switches stay closed as long as  $V_{CC}$  is above the power-down threshold voltage and SHDN is high. Figures 1 and 2 show typical startup/power-up sequences with and without click-pop suppression.

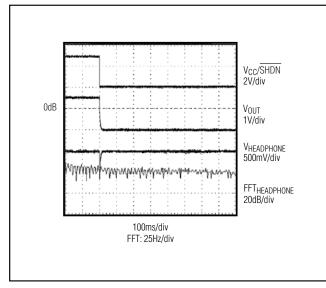

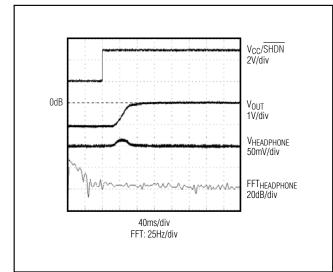

#### Shutdown

If the supply voltage falls below the UVLO threshold or if SHDN is driven low, the device enters low-power shutdown mode. In low-power shutdown mode, quiescent current reduces to  $0.001\mu$ A. The switches are immediately turned off and  $220k\Omega$  resistors slowly bleed the charge off the coupling capacitors. Figures 3 and 4 show typical shutdown/power-down sequences with and without click-pop suppression. For optimal click-pop performance, mute the audio signal before shutting down the MAX9890.

Figure 1. Startup/Power-Up Sequence Without Click-Pop Suppression

Figure 3. Shutdown/Power-Down Sequence Without Click-Pop Suppression

#### Switches

The MAX9890's internal switches connect the input to the output after the coupling capacitors are fully charged. The MAX9890A holds the switches open for 200ms and is ideal for coupling capacitors less than 100 $\mu$ F. The MAX9890B has a longer turn-on time of 330ms and is

####

Figure 4. Shutdown/Power-Down Sequence With Click-Pop Suppression

ideal with larger coupling capacitors less than 220µF. The internal switches have a low on-resistance (R<sub>ON</sub> = 0.5 $\Omega$ ) and on-resistance flatness (R<sub>FLAT(ON</sub>) = 2m $\Omega$ ) minimizing total harmonic distortion plus noise (THD+N). The relationship below shows the contribution to THD+N through the switch, due to on-resistance and on-resistance flat-

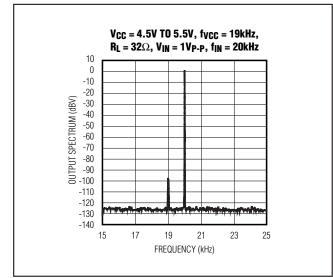

Figure 5. FFT for PSRR

ness (on-resistance flatness is defined as the difference between the maximum and minimum values of on-resistance measured over the specific analog-signal range).

$$THD_{MAXIMUM} = \frac{R_{FLAT(ON)}}{4R_{LOAD}} \times 100\%$$

#### **Power-Supply Rejection Ratio (PSRR)**

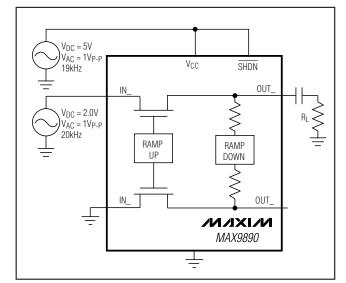

PSRR is the measurement of AC power-supply ripple or noise that couples to the output. Variations in supply voltage corrupt the audio signal, due to changes in the R<sub>ON</sub> value by supply modulation. The FFT shown in Figure 5 was taken with a 19kHz 1V<sub>P-P</sub> sine wave onto the 5V DC supply voltage, and a 20kHz 1V<sub>P-P</sub> sine wave applied at IN\_ with a 32 $\Omega$  load is shown in Figure 6. The MAX9890 maintains a -100dB (typ) PSRR across the supply voltage range eliminating any corruption of the audio signal from supply variations. Therefore, with a zero audio signal, the R<sub>ON</sub> variation due to supply voltage ripple does not contribute to any output signal modulation.

#### Low-Frequency Response

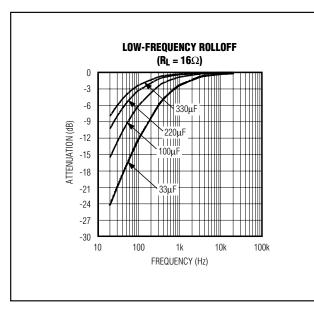

In addition to the cost and size disadvantages of the output-coupling capacitors, these capacitors limit the amplifier's low-frequency response and can distort the audio signal.

Figure 6. PSRR Test Circuit

The impedance of a headphone or speaker load and the output-coupling capacitor form a highpass filter with the -3dB point set by:

$$f_{-3dB} = \frac{1}{2\pi R_L C_{OUT}}$$

where R<sub>L</sub> is the headphone impedance and C<sub>OUT</sub> is the output-coupling capacitor value. The highpass filter is required by conventional single-ended, single powersupply headphone drivers to block the midrail DC bias component of the audio signal from the headphones. The drawback to the filter is that it can attenuate lowfrequency signals. Larger values of C<sub>OUT</sub> reduce this effect but result in physically larger, more expensive capacitors. Figure 7 shows the relationship between the size of C<sub>OUT</sub> and the resulting low-frequency attenuation. Note that the -3dB point for a 16 $\Omega$  headphone with a 100µF blocking capacitor is 100Hz, well within the normal audio band, resulting in low-frequency attenuation of the reproduced signal.

The MAX9890A and MAX9890B have different turn-on times to accommodate different size output-coupling capacitors (see Table 1). Using a capacitor smaller than the specified maximum allowed does not degrade click-pop suppression. Therefore, capacitors less than 100µF can be used with the A or B version devices.

Figure 7. Low-Frequency Attenuation for Common DC-Blocking Capacitor Values

#### **External Capacitor (CCEXT)**

The external click-pop suppression capacitor at CEXT serves a dual purpose. On power-up, CCEXT is charged by an internal current source and is used to slowly ramp up the external coupling capacitors. When the device is powered down, CCEXT powers the internal circuitry used to drain the external coupling capacitors. A  $0.1\mu$ F capacitor between CEXT and GND provides clickless/popless operation with coupling capacitors for both the MAX9890A and MAX9890B, even with the rapid removal of supply voltage.

#### Applications Information

#### Layout

Good layout improves performance by decreasing the amount of stray capacitance and noise. To decrease stray capacitance, minimize PC board trace lengths and resistor leads, and place external components as close to the device as possible.

#### **Power Supply and Bypassing**

The excellent PSRR of the MAX9890 allows it to operate from noisy power supplies. In most applications, a  $0.1\mu$ F capacitor from V<sub>CC</sub> to GND is sufficient. This bypass capacitor should be placed close to V<sub>CC</sub>.

#### Table 1. Coupling Capacitor

| CAPACITOR<br>SIZE (µF) | MAX9890A<br>TURN-ON TIME<br>(200ms) | MAX9890B<br>TURN-ON TIME<br>(300ms) |

|------------------------|-------------------------------------|-------------------------------------|

| 33                     | $\checkmark$                        | $\checkmark$                        |

| 47                     |                                     | $\checkmark$                        |

| 100                    | $\checkmark$                        | $\checkmark$                        |

| 150                    | *                                   | $\checkmark$                        |

| 220                    | *                                   | $\checkmark$                        |

| 330                    |                                     | *                                   |

| 470                    | —                                   | *                                   |

\*May experience some degradation of click-pop suppression.

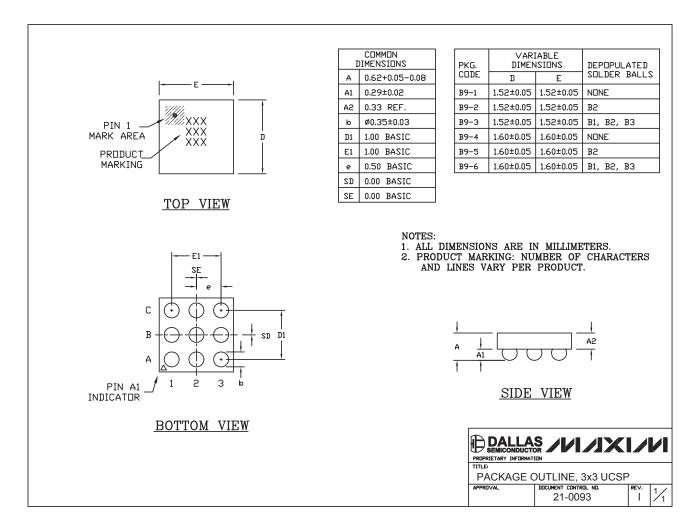

#### **UCSP** Applications Information

For the latest application details on UCSP construction, dimensions, tape-carrier information, printed circuit board techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to the Application Note, "UCSP—A Wafer-Level Chip-Scale Package" available on Maxim's website at www.maximic.com/ucsp.

#### \_Chip Information

TRANSISTOR COUNT: 1001 PROCESS: BICMOS

#### **Typical Application Circuit**

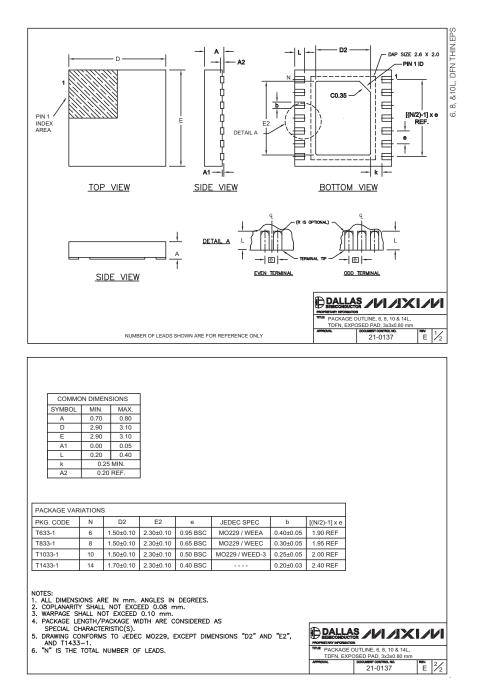

#### \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

#### \_Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

#### 12

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.