# 20A, 27V Intelli-Phase Solution (Single IC with Integrated HS/LS FETs and Driver)

#### DESCRIPTION

The MP86981 is a monolithic Half Bridge with built in internal power MOSFETs and gate drivers. It achieves 20A continuous output current over a wide input supply range.

Integration of the Driver and MOSFETs results in high efficiency due to optimal dead time control and parasitic inductance reduction.

The MP86981 is a Monolithic IC approach to drive up to 20A per phase. This very small 5x5 QFN can be used from 100KHz to 1MHz operation.

This device is designed to work with tri state output controller.

The MP86981 is ideal for notebook applications where efficiency and small size are a premium.

#### **FEATURES**

- Wide 4.5V to 21V Operating Input Range

- 20A Output Current

- Simple Logic Interface(5.0V)

- Synchronous Gate Driver Delivers up to 95% Efficiency

- Operation from 100KHz to 1MHz

- Accepts 3-state PWM Input

- Thermal Shutdown

- Used for multi phase operation

- Available in a 5mm x 5mm QFN Package

#### **APPLICATIONS**

- Power modules

- Notebook, Core Voltage

- Graphic Card Core Regulators

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

The information in this datasheet about the product and its associated technologies are proprietary and intellectual property of Monolithic Power Systems and are protected by copyright and pending patent applications.

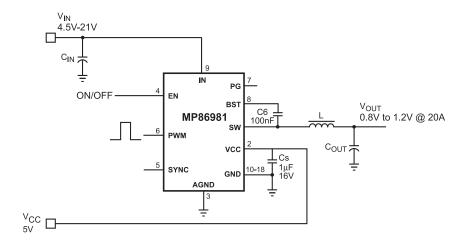

#### TYPICAL APPLICATION

#### ORDERING INFORMATION

| Part Number* | Package | Top Marking | Temperature    |

|--------------|---------|-------------|----------------|

| MP86981DU    | 5x5 QFN | MP86981DU   | –40°C to +85°C |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP86981DU–Z); For RoHS compliant packaging, add suffix –LF (e.g. MP86981DU–LF–Z)

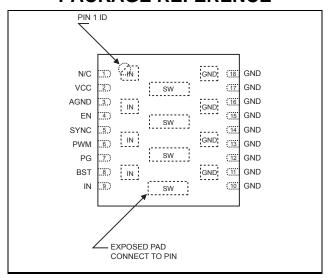

# **PACKAGE REFERENCE**

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>IN</sub>             | 27V                |

|--------------------------------------------|--------------------|

| $V_{SW}$ 0.3V to $V_{IN}$ + (              |                    |

| $V_{BS}$ $V_{SW}$ .                        | + 6V               |

| All Other Pins–0.3V to                     |                    |

| Continuous Power Dissipation $(T_A = +25)$ | °C) <sup>(2)</sup> |

| 3                                          | 3.5W               |

| Junction Temperature15                     |                    |

| Lead Temperature26                         | 30°C               |

| Storage Temperature65°C to +15             |                    |

| Recommended Operating Conditions           | (3)                |

| Supply Voltage V <sub>IN</sub> 4.5V to     |                    |

| Operating Temperature40°C to +8            | 35°C               |

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|------------------------|-------------------------|-------------------------|------|

| 5x5 QFN                | 36                      | 8                       | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on approximately 4" square of 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 12V$ ,  $T_A = +25$ °C, unless otherwise noted.

| Parameters                                    | Symbol                | Condition                             | Min | Тур | Max | Units |

|-----------------------------------------------|-----------------------|---------------------------------------|-----|-----|-----|-------|

| I <sub>CC</sub> Standby                       | I <sub>CC_Stdby</sub> | V <sub>CC</sub> =5V, PWM=EN=LO        |     | 230 | 300 | uA    |

| I <sub>IN</sub> (Shutdown)                    | I <sub>IN (Off)</sub> | V <sub>CC</sub> = 0V                  |     |     | 5   | uA    |

| I <sub>IN</sub> Standby                       | I <sub>IN Stdby</sub> | V <sub>CC</sub> =5V, PWM=EN=LO        | 40  | 70  | 100 | uA    |

| Rise Time (5)                                 |                       | I <sub>OUT</sub> = 20A                |     | 5   | 8   | ns    |

| Fall Time <sup>(5)</sup>                      |                       | I <sub>OUT</sub> = 20A                |     | 3   | 6   | ns    |

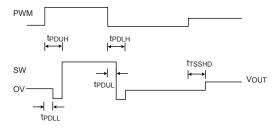

| PWM to SW Delay Rising                        | T <sub>dh</sub>       | PWM to SW                             |     | 20  |     | ns    |

| PWM to SW Delay Falling                       | T <sub>dl</sub>       | PWM to SW                             |     | 38  |     | ns    |

| Minimum On-Time                               |                       |                                       |     | 40  |     | ns    |

| Dead-Time Rising <sup>(5)</sup>               |                       |                                       |     | 5   | 8   | ns    |

| Dead-Time Falling <sup>(5)</sup>              |                       |                                       |     | 5   | 8   | ns    |

| Under Voltage Lockout Threshold Rising        |                       |                                       |     | 3.7 | 4.2 | V     |

| Under Voltage Lockout Threshold<br>Hysteresis |                       |                                       |     | 470 |     | mV    |

| Thermal Shutdown Rising                       |                       |                                       |     | 160 |     | °C    |

| SYNC Pull-Up Current                          | I <sub>SYNC</sub>     | SYNC=0V                               |     | -14 |     | μA    |

| SYNC Logic High Voltage                       |                       |                                       | 2   |     |     | V     |

| SYNC Logic Low Voltage                        |                       |                                       |     |     | 0.4 | V     |

| EN Input Low Voltage                          |                       |                                       |     |     | 0.4 | V     |

| En Input High Voltage                         |                       |                                       | 2   |     |     | V     |

| Power Good Rds(on)                            |                       | EN=0V                                 |     | 20  |     | Ω     |

| PWM Input                                     |                       |                                       |     |     |     |       |

| Input Current                                 | loune                 | V <sub>PWM</sub> =5V                  |     | 90  |     | μA    |

|                                               | I <sub>PWM</sub>      | V <sub>PWM</sub> =0V                  |     | -90 |     | μA    |

| PWM Tri-State Rising Threshold                |                       | V <sub>CC</sub> =5V                   |     | 1.7 |     | V     |

| PWM Tri-State Falling Threshold               |                       | V <sub>CC</sub> =5V                   |     | 3.5 |     | V     |

| Tri-State Shutdown Holdoff Time               | t <sub>TSSHD</sub>    | V <sub>CC</sub> =5V, Temperature=25°C |     | 80  |     | ns    |

| UG/LG Three-State Propagation Delay           | t <sub>PTS</sub>      |                                       |     | 20  |     | ns    |

| USW Turn-Off Propagation Delay                | t <sub>PDUL</sub>     | V <sub>CC</sub> =5V                   |     | 35  |     | ns    |

| LSW Turn-Off Propagation Delay                |                       | V <sub>CC</sub> =5V                   |     | 16  |     | ns    |

| USW Turn-On Propagation Delay                 | t <sub>PDLL</sub>     | V <sub>CC</sub> =5V                   |     | 26  |     | ns    |

| LSW Turn-On Propagation Delay                 | t <sub>PDLH</sub>     | V <sub>CC</sub> =5V                   |     | 48  |     | ns    |

| Diode Emulation Delay                         | t <sub>DE delay</sub> |                                       |     | 85  |     | ns    |

#### Notes:

5) Guaranteed by design.

Figure 1—Timing Diagram

# **PIN FUNCTIONS**

| Pin #                | Name | Description                                                                                                                                                                                      |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | NC   | Not Connected.                                                                                                                                                                                   |

| 2                    | VCC  | BG Driver Bias Supply. Decouple with a 1µF ceramic capacitor.                                                                                                                                    |

| 3                    | AGND | Signal Ground.                                                                                                                                                                                   |

| 4                    | EN   | On/Off Control. A LOW places SW into high impedance state.                                                                                                                                       |

| 5                    | SYNC | An open enables Lower Synchronous Switch. Pull down low puts Low Switch into Diode Emulation mode.                                                                                               |

| 6                    | PWM  | Pulse Width Modulation Control. Accepts three state input. Force PWM to midstate or open to place SW into high impedance state.                                                                  |

| 7                    | PG   | Power Good. Open drain output is low impedance to ground until internal supplies are good.                                                                                                       |

| 8                    | BST  | Bootstrap. This capacitor is needed to drive the power switch's gate above the supply voltage. It is connected between SW and BST pins to form a floating supply across the power switch driver. |

| 9<br>Exposed Pad     | IN   | Supply Voltage. $C_{\text{IN}}$ is needed to prevent large voltage spikes from appearing at the input.                                                                                           |

| 10–18<br>Exposed Pad | GND  | Power Ground.                                                                                                                                                                                    |

| Exposed Pad          | SW   | Switch Output. These pins are fused together.                                                                                                                                                    |

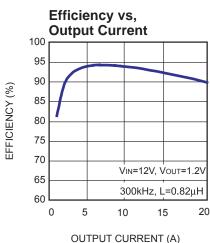

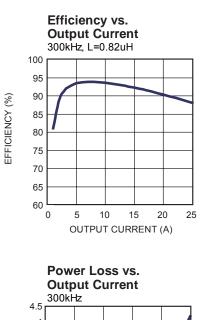

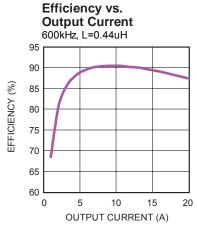

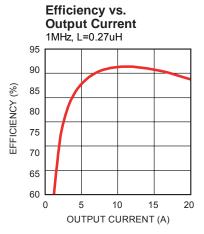

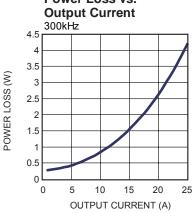

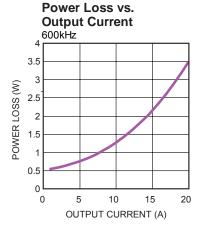

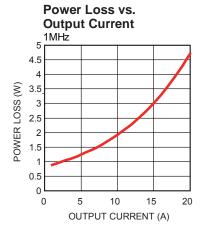

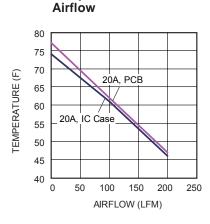

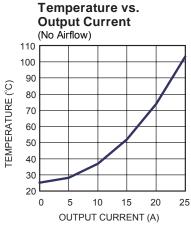

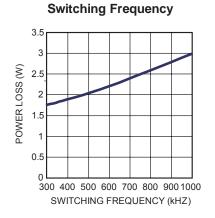

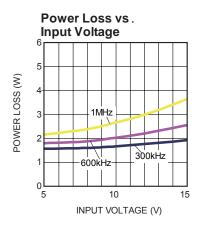

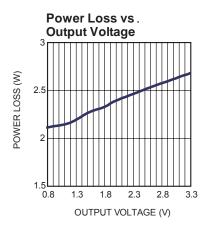

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 12V$ ,  $V_{CC} = 5V$ ,  $V_{OUT} = 1.2V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

Temperature vs.

Power Loss vs.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN} = 12V$ ,  $V_{CC} = 5V$ ,  $V_{OUT} = 1.2V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

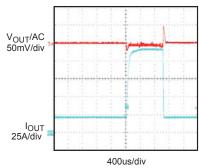

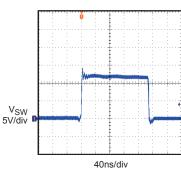

# **SOA Waveform**

## **Output Waveform**

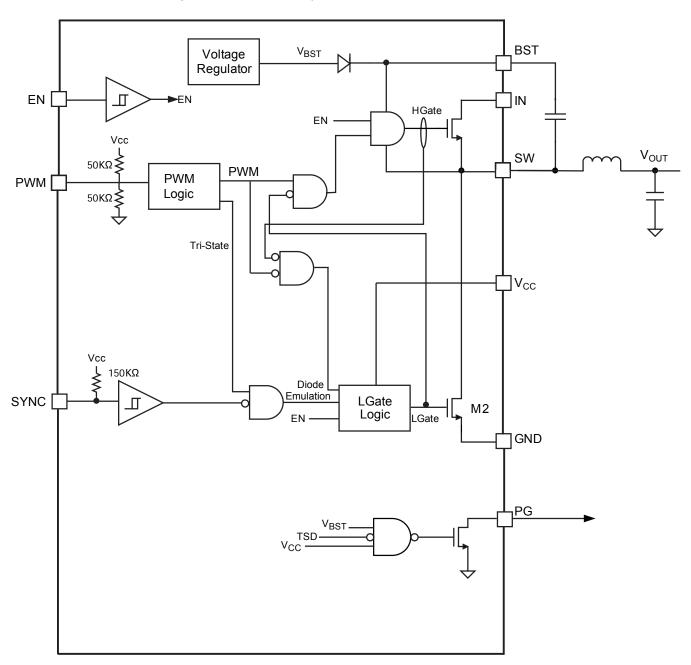

## **OPERATION**

The MP86981 is a 20A Half Bridge driver ideally suited for Multi-Phase Buck regulators.

When the EN transitions from Low to High, the internal voltage regulators are enabled. Once both the  $V_{\text{CC}}$  and  $V_{\text{BST}}$  signals are sufficiently

high and Thermal Shutdown is not tripped, the operation begins.

To allow M2, the lower DMOS, to enter Diode Emulation, the SYNC pin is driven Low.

Figure 2—Functional Block Diagram

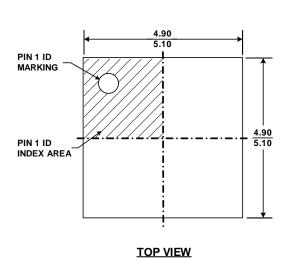

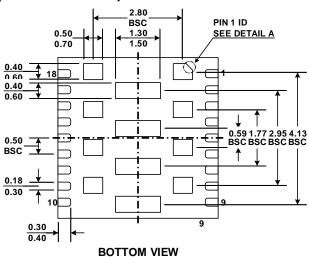

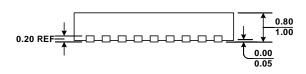

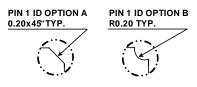

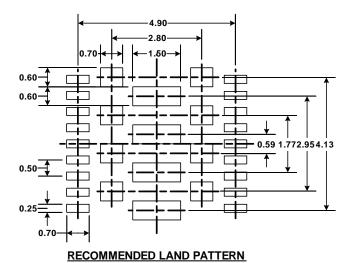

# **PACKAGE INFORMATION**

## FCTQFN18L (EXPOSED PAD)

**SIDE VIEW**

DETAIL A

#### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) JEDEC REFERENCE IS MO-229, VARIATION VJJD.

- 5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.