Middle Power Class-D Speaker Amplifier

## 25W+25W

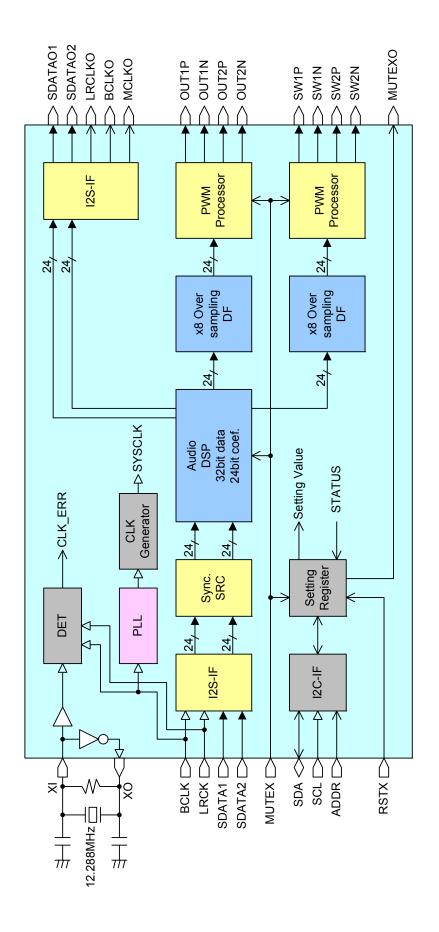

# Full Digital Speaker Amplifier with built-in DSP

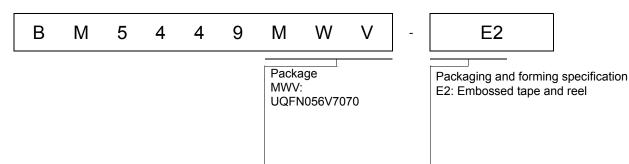

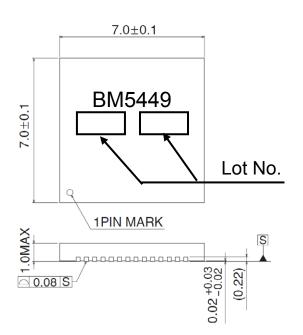

BM5449MWV

## General Description

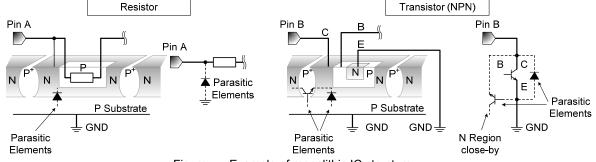

BM5449MWV is a Full Digital Speaker Amplifier with built-in DSP (Digital Sound Processor) designed for Flat-panel TVs in particular for space-saving and low-power consumption, delivers an output power of 25W+25W. This IC employs state-of-the-art Bipolar, CMOS, and DMOS (BCD) process technology that eliminates turn-on resistance in the output power stage and internal loss due to line resistances up to an ultimate level. With this technology, the IC can achieve high efficiency of 90% (10W+10W output with  $8\Omega$  load). In addition, the IC is packaged in a compact reverse heat radiation type power package to achieve low power consumption and low heat generation and eliminates necessity of external heat-sink up to a total output power of 40W. This product satisfies both needs for drastic downsizing, low-profile structures and many function, high quality playback of sound system.

#### Features

- With wide range of power supply voltage. (V<sub>CC</sub>=10 to 26V)

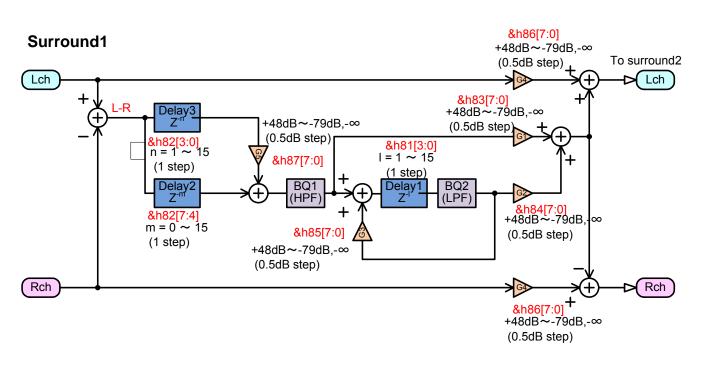

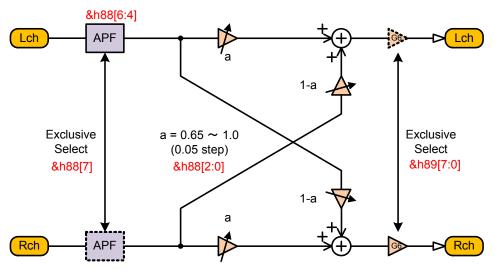

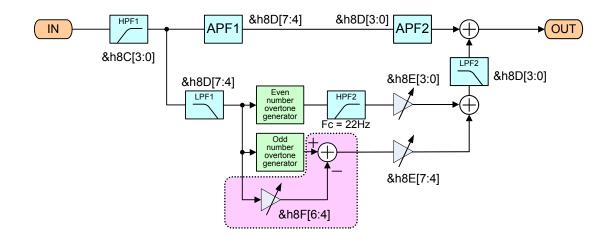

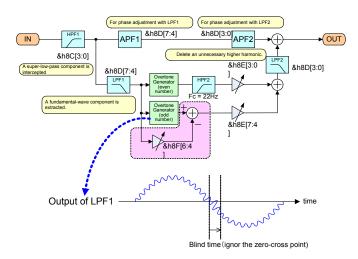

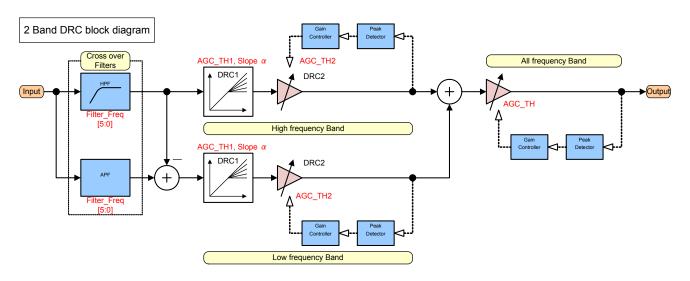

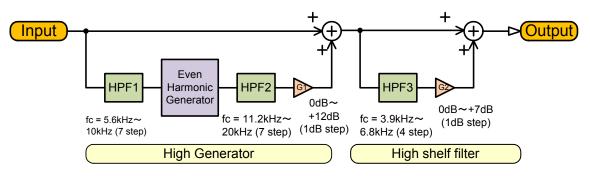

- This IC includes the DSP (digital sound processor) for Audio signal processing for Flat TVs. Synchronous SRC, Surround, 8 Band EQ, 1 Band EQ (for Sub), Volume, 2 Band DRC, Delay RAM for phase revised Close Over Filter, 512 Taps FIR Filter, P<sup>2</sup>Volume, P<sup>2</sup>Base+, Higher Sound Complement (High Generator), Soft Clipper, Hard Clipper

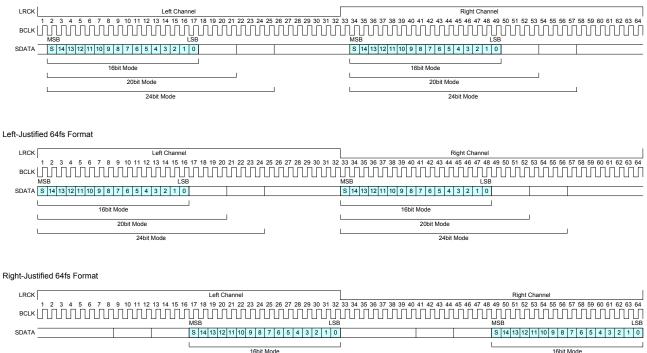

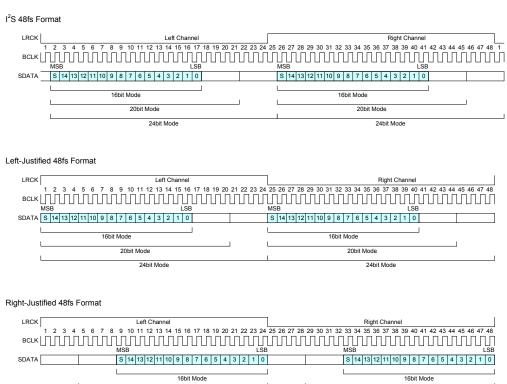

- BCLK: 32fs / 48fs / 64fs, SDATA: 16 / 20 / 24bits

- Two Digital Audio Output for Audio DAC and headphone.

- One PWM Output for Subwoofer.

- The sound quality decrease by the power supply variation is prevented with the output feedback circuit. In addition, a low noise and a low distortion are achieved. Mass electrolytic capacitor is unnecessary because it is strong in the power supply variation.

- It contributes to miniaturizing, making to the thin type, and the power saving of the system by highly effective (10W+10W output and 8Ω on-load) 90% and low generation of heat.

- Low current at the Power down Mode.

- The pop noise at power supply on/off is prevented, and a more high-quality soft mute function is built into. Highly reliable design with built-in various protection functions.

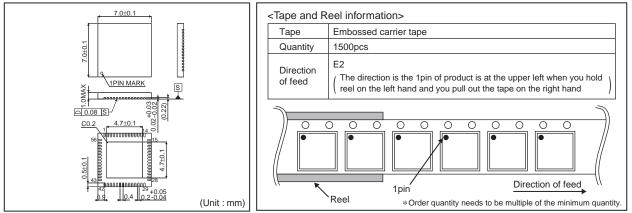

- The component side product can be decreased because of small package (UQFN056V7070).

- The maximum output in the stereo is 25W+25W (VCC=20.5V, 8Ω load).

- The maximum output in the monaural(PBTL) is 50W(VCC=20.5V, 4Ω load)

- •Key Specifications

- Supply voltage (VCC):

Speaker output power

- Speaker output power (VCC=18V, RL=8Ω)

- THD+N

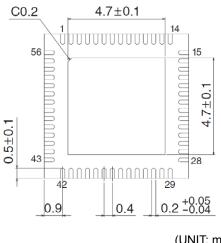

#### Package UQFN056V7070

10V to 26V 20W+20W(Typ.)

0.05 %( Typ.)

W (Typ.) x D (Typ.) x H(Max.) 7.00mm x 7.00mm x 1.00mm

- Applications

- Flat Panel TVs(LCD, Plasma)

- Home Audio

- Amusement equipments

- Electronic Music equipments etc.

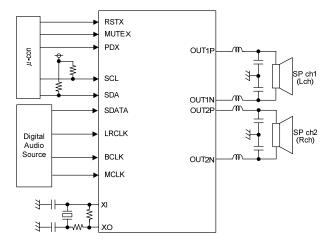

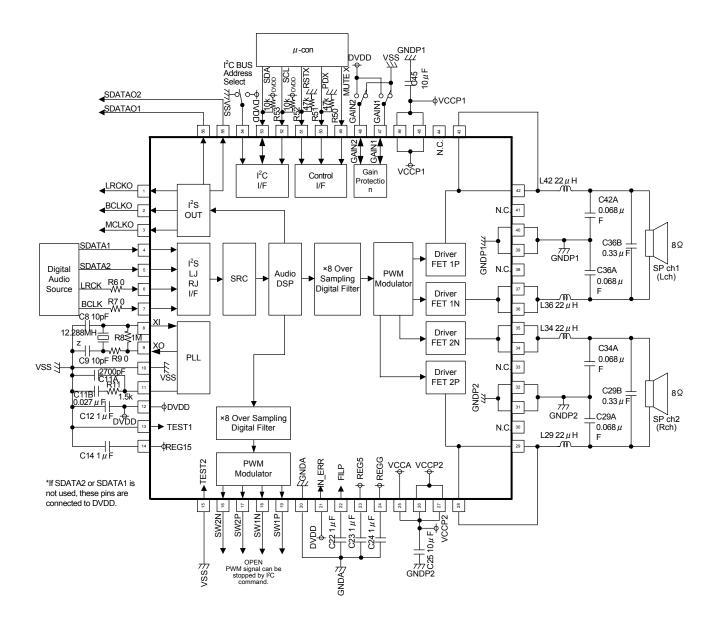

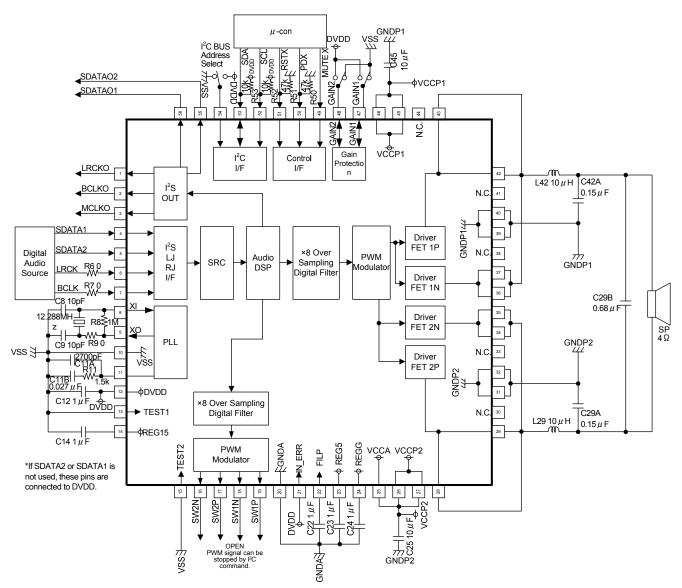

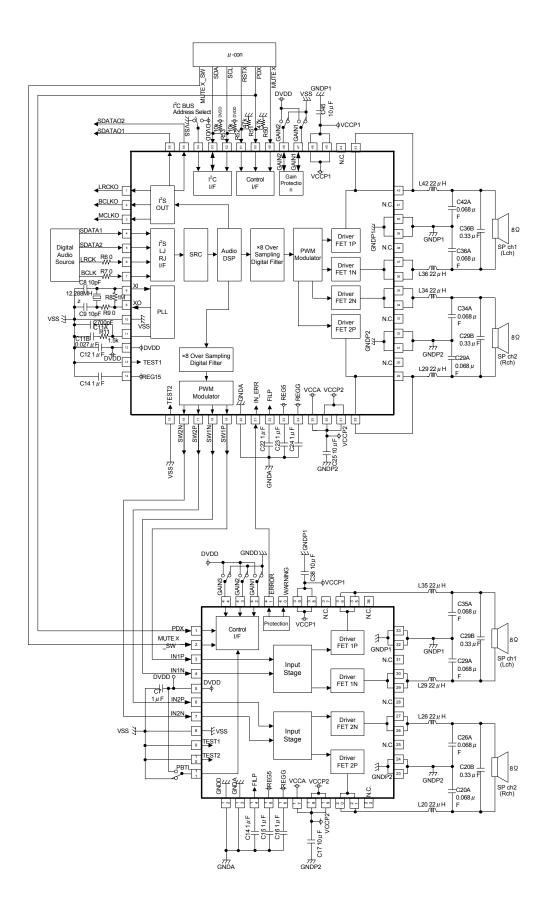

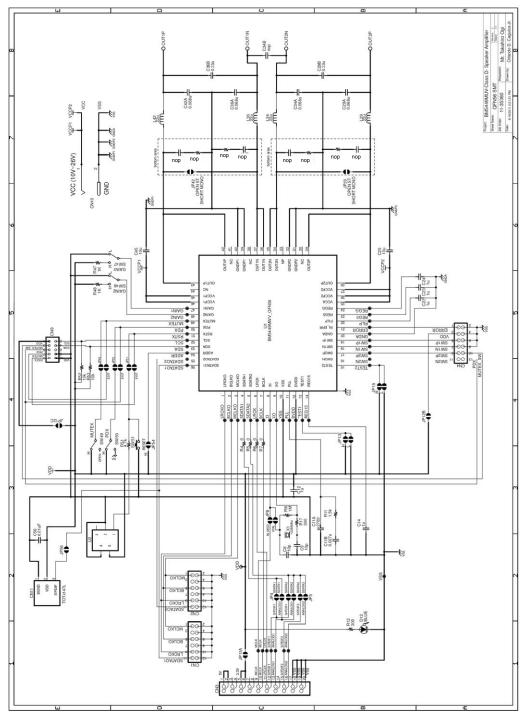

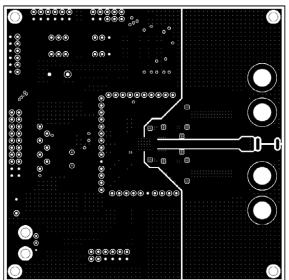

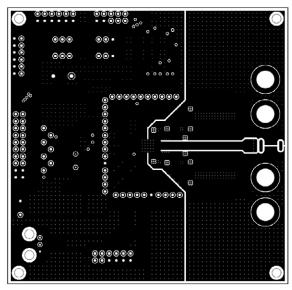

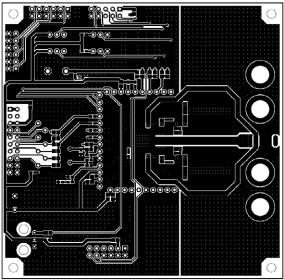

Typical Application Circuit

Figure 1. Typical application circuit

OProduct structure : Silicon monolithic integrated circuit OThis product is not designed protection against radiation.

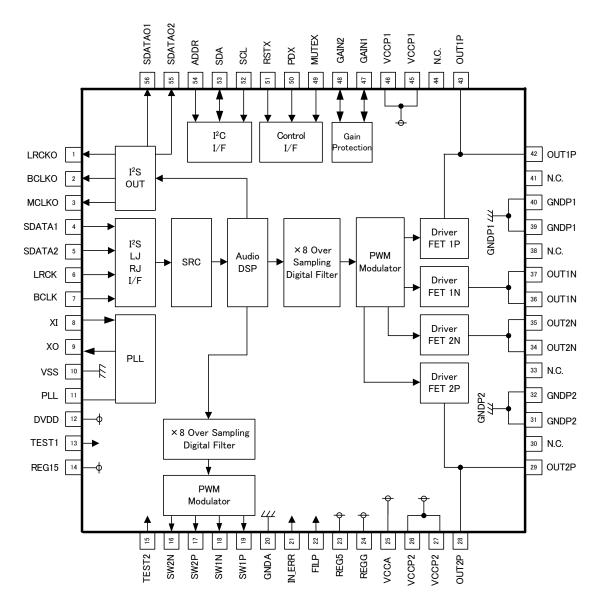

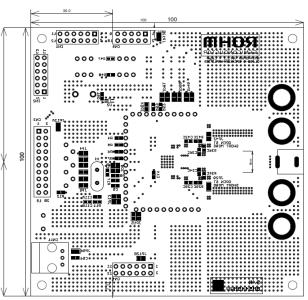

## Pin Configuration

Figure 2. Pin configuration (Top View)

## Pin Description

| No. | Name   | I/O | No. | Name   | I/O | No. | Name  | I/O | No. | Name    | I/O |

|-----|--------|-----|-----|--------|-----|-----|-------|-----|-----|---------|-----|

| 1   | LRCKO  | I/O | 15  | TEST2  | I   | 29  | OUT2P | 0   | 43  | OUT1P   | 0   |

| 2   | BCLKO  | I/O | 16  | SW2N   | 0   | 30  | N.C.  | -   | 44  | N.C.    | -   |

| 3   | MCLKO  | I/O | 17  | SW2P   | 0   | 31  | GNDP2 | -   | 45  | VCCP1   | -   |

| 4   | SDATA1 | I   | 18  | SW1N   | 0   | 32  | GNDP2 | -   | 46  | VCCP1   | -   |

| 5   | SDATA2 | I   | 19  | SW1P   | 0   | 33  | N.C.  | -   | 47  | GAIN1   | I/O |

| 6   | LRCK   | I   | 20  | GNDA   | -   | 34  | OUT2N | 0   | 48  | GAIN2   | I/O |

| 7   | BCLK   | I   | 21  | IN_ERR | I   | 35  | OUT2N | 0   | 49  | MUTEX   | Ι   |

| 8   | XI     | I   | 22  | FILP   | 0   | 36  | OUT1N | 0   | 50  | PDX     | Ι   |

| 9   | XO     | 0   | 23  | REG5   | 0   | 37  | OUT1N | 0   | 51  | RSTX    | Ι   |

| 10  | VSS    | -   | 24  | REGG   | 0   | 38  | N.C.  | -   | 52  | SCL     | Ι   |

| 11  | PLL    | 0   | 25  | VCCA   | -   | 39  | GNDP1 | -   | 53  | SDA     | I/O |

| 12  | DVDD   | -   | 26  | VCCP2  | -   | 40  | GNDP1 | -   | 54  | ADDR    | Ι   |

| 13  | TEST1  | I   | 27  | VCCP2  | -   | 41  | N.C.  | -   | 55  | SDATAO2 | I/O |

| 14  | REG15  | 0   | 28  | OUT2P  | 0   | 42  | OUT1P | 0   | 56  | SDATAO1 | I/O |

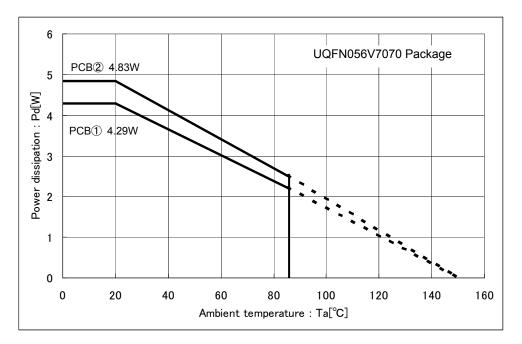

## Absolute Maximum Ratings(Ta=25°C)

| Item                         | Symbol            | Limit       | Unit | Conditions                            |       |

|------------------------------|-------------------|-------------|------|---------------------------------------|-------|

| Supply voltage               | V <sub>CC</sub>   | -0.3 to 30  | v    | Pin 25, 26, 27, 45, 46                | *1 *2 |

| Supply voltage               | V <sub>DD</sub>   | -0.3 to 4.5 | v    | Pin 12                                | *1 *2 |

| Power dissipation            | Pd                | 4.29        | w    |                                       | *3    |

|                              | Fu                | 4.83        | vv   |                                       | *4    |

| Input voltage                | V <sub>IN</sub>   | -0.3 to 4.5 | V    | Pin 4 to 8, 13, 15, 49to54            | *1    |

| Terminal voltage1            | V <sub>PIN1</sub> | -0.3 to 4.5 | V    | Pin 1 to 3, 9, 16to19, 47, 48, 55, 56 | *1    |

| Terminal voltage 2           | V <sub>PIN2</sub> | -0.3 to 7.0 | V    | Pin 22 to 24                          | *1    |

| Terminal voltage 3           | V <sub>PIN3</sub> | -0.3 to 30  | V    | Pin 28, 29, 34 to 37, 42, 43          | *1 *5 |

| Operating temperature range  | T <sub>opr</sub>  | -25 to +85  | °C   |                                       |       |

| Storage temperature range    | T <sub>stg</sub>  | -55 to +150 | °C   |                                       |       |

| Maximum junction temperature | T <sub>jmax</sub> | +150        | °C   |                                       |       |

\*1 The voltage that can be applied reference to GND(Pin 10, 20, 31, 32, 39, 40)

\*2 Do not, however exceed Pd and Tjmax=150°C.

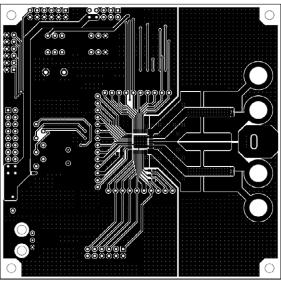

\*3 74.2mm×74.2mm×1.6mm FR4, 4-layer glass epoxy board (Top and bottom layer back copper foil size : 34.09mm<sup>2</sup>, 2nd, 3rd layer back copper foil size:5505mm<sup>2</sup>)

Derating in done at 34.3 mW/°C for operating above Ta=25°C. There are thermal via on the board.

\*4 74.2mm×74.2mm×1.6mm F FR4, 4-layer glass epoxy board (Copper area 5505mm2) Derating in done at 38.6 mW/°C for operating above Ta=25°C. There are thermal via on the board.

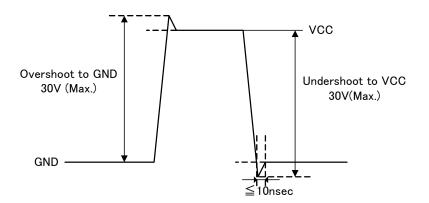

\*5 It should use it below this ratings limit including the AC peak waveform (overshoot) for all conditions. At only undershoot, it is admitted using at ≦10nse and ≦30V by the VCC reference. (Please refer following figure.)

#### RecommendedOperating Ratings (Ta=25°C)

| Item                   | Symbol          | Limit      | Unit | Conditions                 |    |    |

|------------------------|-----------------|------------|------|----------------------------|----|----|

| Supply voltage         | V <sub>CC</sub> | 10 to 26   | V    | Pin 25, 26, 27, 45, 46     | *1 | *2 |

| Supply voltage         | V <sub>DD</sub> | 3.0 to 3.6 | v    | Pin 12                     | *1 | *2 |

|                        |                 | 3.6        | 0    | Vcc≦18V, Stereo BTL mode   |    | *6 |

| Minimum load impedance | RL              | 3.0        | Ω    | Monaural Parallel BTL mode |    | *6 |

|                        |                 | 5.4        | Ω    | Vcc≦26V, Stereo BTL mode   |    | *6 |

\*6 Do not, however exceed Pd.

## Electrical characteristics

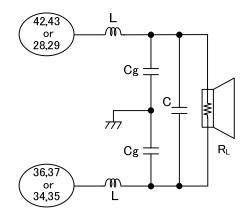

(Unless otherwise specified Ta=25°C, Vcc=18V, V<sub>DD</sub>=3.3V, fin=1kHz, R<sub>L</sub>=8Ω, RSTX=3.3V, PDX=3.3V, MUTEX=3.3V fs= 48kHz, GAIN=20dB, DSP : Through, Output LC filter : L=22µH, C=0.33µF, Cg=0.068µF)

|                                                  | IS-46KHZ, GAIN-200B, DSF. THIOUGH, Output LC HILET. L-22H, C-0.30H, C9-0.000HF) |                         |              |                         |      |                                                                   |

|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------|--------------|-------------------------|------|-------------------------------------------------------------------|

| Item                                             | Symbol                                                                          | Min                     | Limit<br>Typ | Max                     | Unit | Conditions                                                        |

| Total circuit                                    |                                                                                 |                         |              |                         |      |                                                                   |

| Circuit current                                  | I <sub>CC1</sub>                                                                | -                       | 0.1          | 0.2                     | mA   | Pin 25, 26, 27, 45, 46 No load<br>RSTX=3.3V, PDX=0V, MUTEX=0V     |

| (Power down mode)                                | I <sub>DD1</sub>                                                                | -                       | 3.7          | 7.5                     |      | Pin 12, Noload<br>RSTX=3.3V, PDX=0V, MUTEX=0V                     |

| Circuit current                                  | I <sub>CC2</sub>                                                                | -                       | 7.0          | 25                      | ~    | Pin 25, 26, 27, 45, 46 No load<br>RSTX=3.3V, PDX=3.3V, MUTEX=0V   |

| (mute mode)                                      | I <sub>DD2</sub>                                                                | -                       | 25           | 70                      | mA   | Pin 12 Noload<br>RSTX=3.3V, PDX=3.3V, MUTEX=0V                    |

| Circuit current                                  | I <sub>CC3</sub>                                                                | -                       | 50           | 80                      | mA   | Pin 25, 26, 27, 45, 46 No load<br>RSTX=3.3V, PDX=3.3V, MUTEX=3.3V |

| (Normal mode)                                    | I <sub>DD3</sub>                                                                | -                       | 30           | 70                      | IIIA | Pin 12 Noload<br>RSTX=3.3V, PDX=3.3V, MUTEX=3.3V                  |

|                                                  | $V_{REG15}$                                                                     | 1.3                     | 1.5          | 1.7                     |      | Pin 14                                                            |

| Regulator output voltage                         | V <sub>REG5</sub>                                                               | 4.7                     | 5.0          | 5.3                     | V    | Pin 23                                                            |

|                                                  | V <sub>REGG</sub>                                                               | 4.7                     | 5.0          | 5.3                     |      | Pin 24                                                            |

| ERROR WARNING terminal<br>L level voltage        | V <sub>ERR</sub>                                                                | -                       | 0.4          | 0.8                     | V    | Pin 47, 48, I <sub>0</sub> =0.1mA                                 |

| H level input voltage                            | V <sub>IH</sub>                                                                 | V <sub>DD</sub><br>x0.8 | -            | -                       | V    | Pin 4 to 7, 13, 15, 21, 49 to 54                                  |

| L level input voltage                            | V <sub>IL</sub>                                                                 | -                       | -            | V <sub>DD</sub><br>x0.2 | V    | Pin 4 to 7, 13, 15, 21, 49 to 54                                  |

| Input current (Input pull-up terminal)           | $I_{IL}$                                                                        | 50                      | 100          | 150                     | μA   | Pin 4 to 7, VIN = 0V                                              |

| Input current(Input pull-down terminal)          | Iн                                                                              | 30                      | 70           | 105                     | μA   | Pin 49 to 51, 54, VIN = 3.3V                                      |

| Input current(SCL, SDA terminal)                 | lı –                                                                            | -                       | 0            | 1                       | μA   | Pin 52, 53, VIN = 3.3V                                            |

| Input current (SCL, SDA terminal)                | Ι <sub>ο</sub>                                                                  | -1                      | 0            | -                       | μA   | Pin 52, 53, VIN = 0V                                              |

| Digital Audio Signal<br>Output H level voltage 1 | V <sub>OH1</sub>                                                                | V <sub>DD</sub><br>-0.5 | -            | V <sub>DD</sub>         | V    | Pin 1 to 3,55,56, lo=1mA                                          |

| PWM for Subwoofer<br>Output H level voltage 2    | V <sub>OH2</sub>                                                                | V <sub>DD</sub><br>-0.5 | -            | V <sub>DD</sub>         | V    | Pin 16 to 19, lo=1mA                                              |

| Digital Audio Signal<br>Output L level voltage 1 | V <sub>OL1</sub>                                                                | 0                       | -            | 0.5                     | V    | Pin 1 to 3,55,56, lo=1mA                                          |

| PWM for Subwoofer<br>Output L level voltage 2    | V <sub>OL2</sub>                                                                | 0                       | -            | 0.5                     | V    | Pin 16 to 19, lo=1mA                                              |

| Speaker output                                   |                                                                                 |                         |              |                         |      |                                                                   |

|                                                  | P <sub>01</sub>                                                                 | -                       | 10           | -                       | W    | Vcc=13V, THD+n=10%, Gain=20dB *7                                  |

| Maximum output                                   | P <sub>02</sub>                                                                 | -                       | 20           | -                       | W    | Vcc=18V, THD+n=10%, Gain=22dB *7                                  |

|                                                  | P <sub>03</sub>                                                                 | -                       | 25           | -                       | W    | Vcc=20.5V、THD+n=10%、Gain=23dB*7                                   |

| Total harmonic distortion                        | THD                                                                             | -                       | 0.05         | -                       | %    | P <sub>0</sub> =1W, BW=20 to 20kHz *7                             |

| Oreastall                                        | OT                                                                              | <u></u>                 | 00           |                         |      |                                                                   |

|                        | ппυ               | -  | 0.05  | -   | 70    | F0-100, D00-20 10 20KHZ                     | 1  |

|------------------------|-------------------|----|-------|-----|-------|---------------------------------------------|----|

| Crosstalk              | СТ                | 60 | 80    | -   | dB    | P <sub>O</sub> =1W, BW=IHF-A                | *7 |

| PSRR                   | PSRR              | -  | 70    | -   | dB    | Vripple=1Vrms, f=1KHz                       | *7 |

| Output noise voltage   | V <sub>NO</sub>   | -  | 80    | 140 | μVrms | -∞dBFS, BW=IHF-A                            | *7 |

|                        | f <sub>PWM1</sub> | -  | 384   | -   |       | fs=8kHz, 16kHz, 32kHz                       | *7 |

| PWM sampling frequency | f <sub>PWM2</sub> | -  | 352.8 | -   | KHz   | fs=11.025kHz, 22.05kHz, 44.1kHz,<br>88.2kHz | *7 |

|                        | f <sub>PWM3</sub> | -  | 384   | -   |       | fs=12kHz, 24kHz, 48kHz, 96kHz               | *7 |

\*7 These items show the typical performance of device and depend on board layout, parts, and power supply.

The standard value is in mounting device and parts on surface of ROHM's board directly.

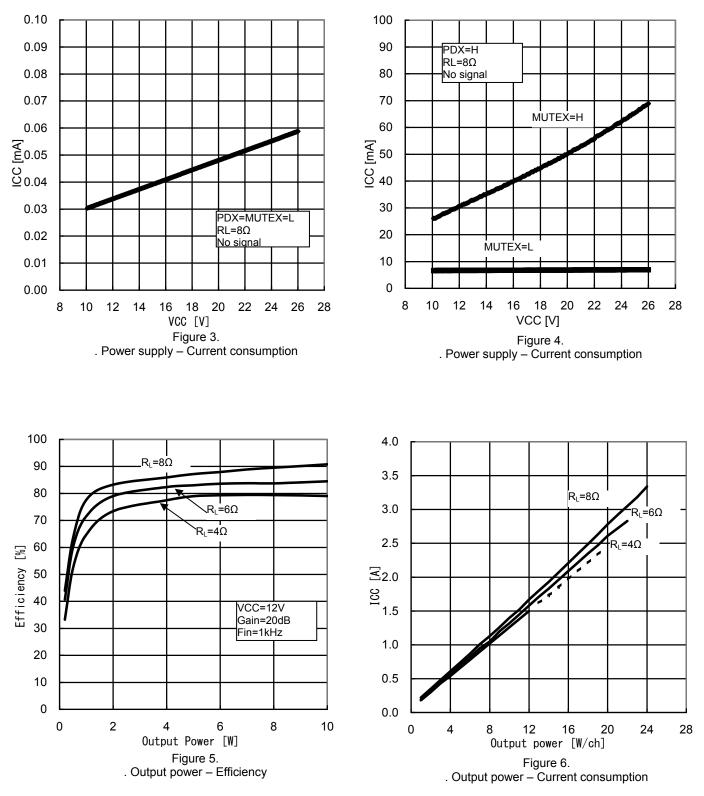

## Typical Performance Curves

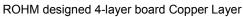

$(Ta=25^{\circ}C,Vcc=18V,V_{DD}=3.3V,fin=1kHz,R_{L}=8\Omega,RSTX=3.3V,PDX=3.3V,MUTEX=3.3V,fs=48kHz,GAIN=23dB,DSP\ through)\ Measured\ by\ ROHM\ designed\ 4-layer\ board.$

Continued on next page.

\*Dotted line means internal dissipation is over package power.

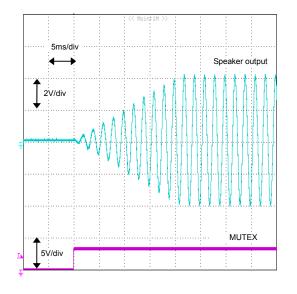

## Typical Performance Curves (Continuation on previous page)

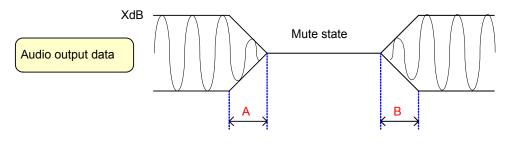

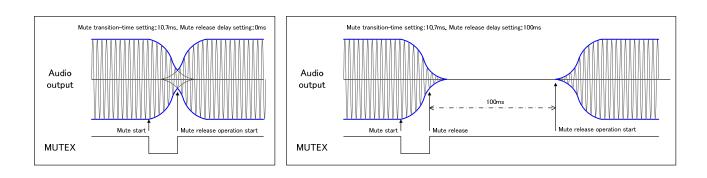

Figure 7. Waveform at smooth start

Figure 8. Waveform at smooth mute

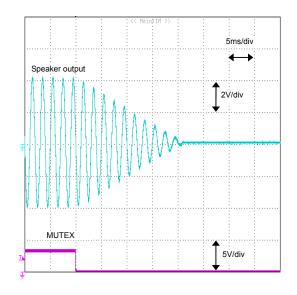

## Typical Performance Curves

$(Ta=25^{\circ}C,Vcc=18V,V_{DD}=3.3V,fin=1kHz,R_{L}=8\Omega,RSTX=3.3V,PDX=3.3V,MUTEX=3.3V,fs=48kHz,GAIN=23dB,DSP \ through) \ Measured by ROHM \ designed \ 4 \ layer \ board.$

Continued on next page.

\*Dotted line means internal dissipation is over package power.

Typical Performance Curves (Continuation on previous page)

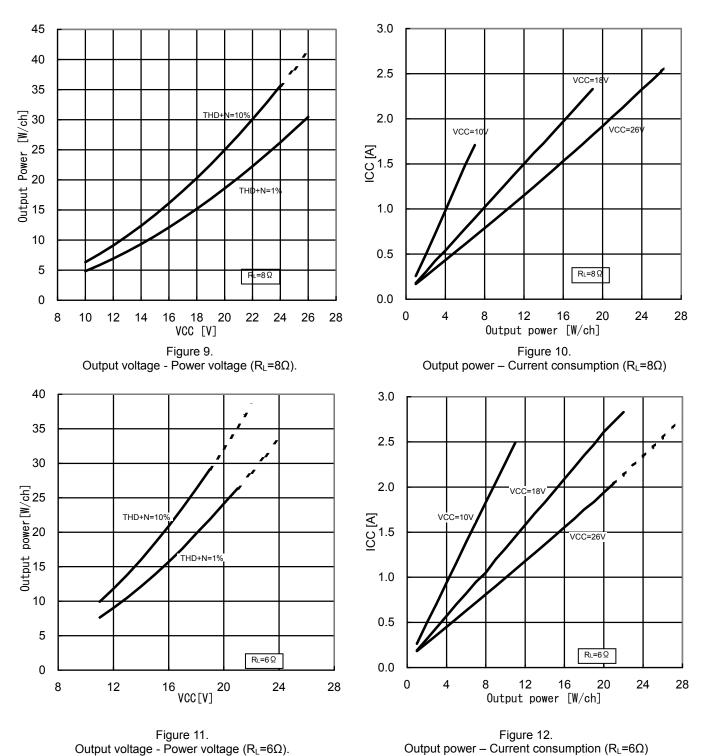

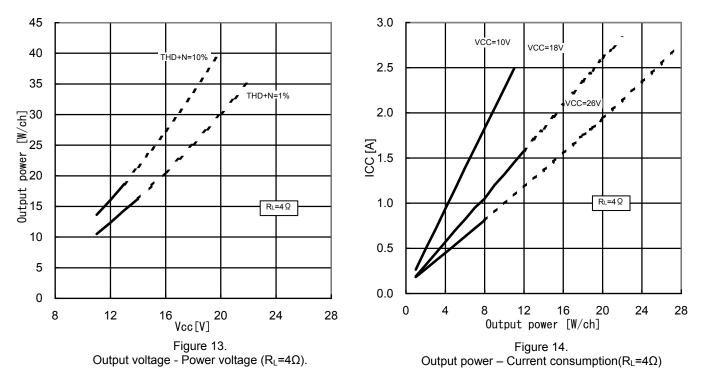

#### Typical Performance Curves

$(Ta=25\ ^\circ\text{C}\ , Vcc=18V, V_{\text{DD}}=3.3V, fin=1kHz, R_{\text{L}}=4\Omega, RSTX=3.3V, PDX=3.3V, MUTEX=3.3V, fs=\ 48kHz, GAIN=20dB, DSP\ through, Output LCfilter: L=10uH, C=0.68uF, Cg=0.15uF, Monaural Parallel BTL mode) Measured by ROHM designed 4-layer board.$

Figure 15. Output voltage - Power voltage ( $R_L$ =4 $\Omega$ , Monaural Parallel BTL mode)

\*Dotted line means internal dissipation is over package power.

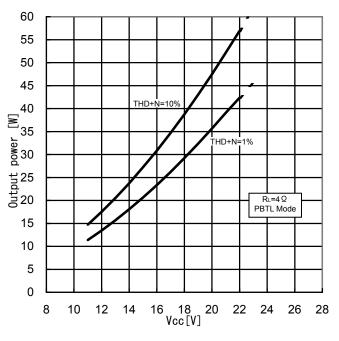

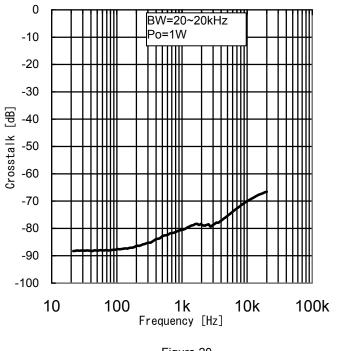

## ●Typical Performance Curves

(Ta=25 °C,Vcc=18V,V<sub>DD</sub>=3.3V,fin=1kHz,R<sub>L</sub>=8Ω,RSTX=3.3V,PDX=3.3V,MUTEX=3.3V,fs= 48kHz,GAIN=20dB,DSP through, Output LCfilter:L=22uH,C=0.33uF,Cg=0.068uF) Measured by ROHM designed 4-layer board.

Output power – THD+N ( $R_L=8\Omega$ )

Figure 19. Frequency – THD+N ( $R_L=8\Omega$ )

Continued on next page.

Typical Performance Curves (Continuation on previous page)

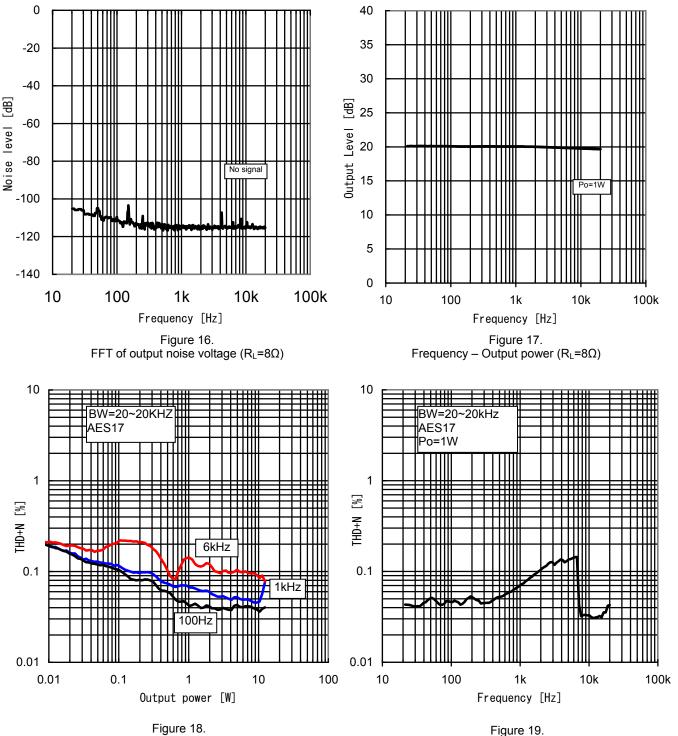

Figure 20. Frequency – Crosstalk ( $R_L$ =8 $\Omega$ )

## Typical Performance Curves

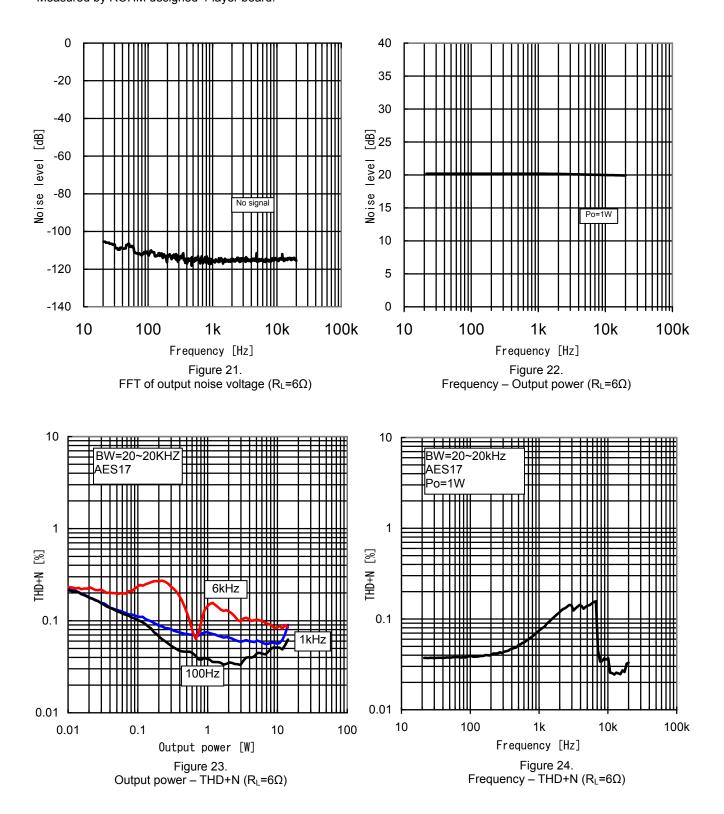

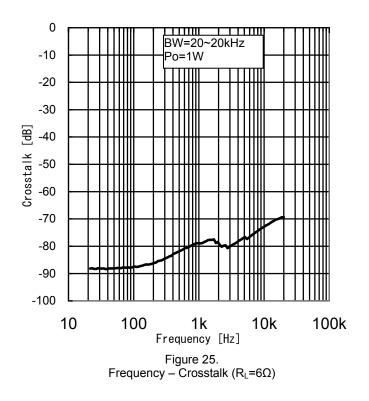

(Ta=25 °C,Vcc=18V,V<sub>DD</sub>=3.3V,fin=1kHz,R<sub>L</sub>=6Ω,RSTX=3.3V,PDX=3.3V,MUTEX=3.3V,fs= 48kHz,GAIN=20dB,DSP through, Output LCfilter:L=15uH,C=0.47uF,Cg=0.1uF) Measured by ROHM designed 4-layer board.

Continued on next page.

•Typical Performance Curves (Continuation on previous page)

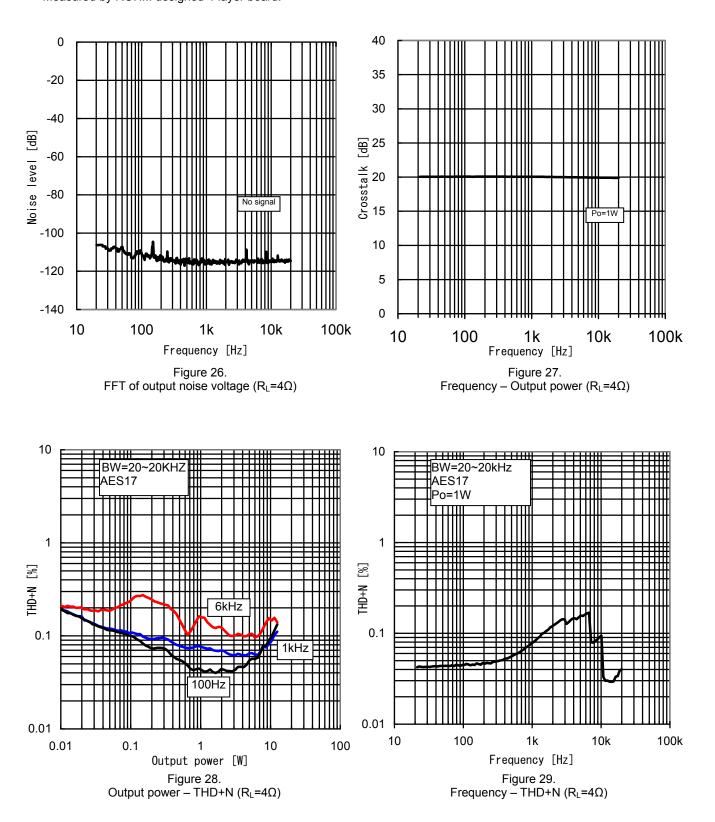

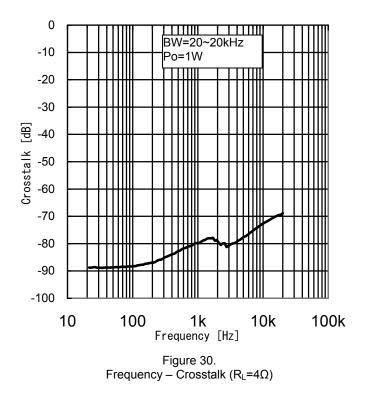

## Typical Performance Curves

(Ta=25 °C,Vcc=18V,V<sub>DD</sub>=3.3V,fin=1kHz,R<sub>L</sub>=4Ω,RSTX=3.3V,PDX=3.3V,MUTEX=3.3V,fs= 48kHz,GAIN=20dB,DSP through, Output LCfilter:L=10uH,C=0.68uF,Cg=0.15uF) Measured by ROHM designed 4-layer board.

Continued on next page.

•Typical Performance Curves (Continuation on previous page)

## About external setting pin

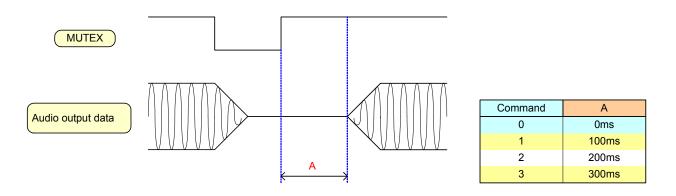

(1) RSTX pin, PDX pin, MUTEX pin function

| 1 |         | - ,     |         |                                   |                 |                   |  |  |  |

|---|---------|---------|---------|-----------------------------------|-----------------|-------------------|--|--|--|

|   | RSTX    | PDX     | MUTEX   | Norm                              | Normal state    |                   |  |  |  |

|   | (51pin) | (50pin) | (49pin) | PWM output<br>(OUT1P, 1N, 2P, 2N) | ERROR<br>output | WARNING<br>output |  |  |  |

|   | L       | L or H  | L or H  | HiZ_L<br>(Power down mode)        | Н               | н                 |  |  |  |

|   | н       | L       | L or H  | HiZ_L<br>(Power down mode)        | Н               | н                 |  |  |  |

|   | Н       | Н       | L       | HIZ_L<br>(MUTE ON)                | Н               | н                 |  |  |  |

|   | Н       | Н       | Н       | Normal<br>(MUTE OFF)              | Н               | Н                 |  |  |  |

| DOTY            | PDX     |                  | ERROR                             | detection       |                   |

|-----------------|---------|------------------|-----------------------------------|-----------------|-------------------|

| RSTX<br>(51pin) | (50pin) | MUTEX<br>(49pin) | PWM output<br>(OUT1P, 1N, 2P, 2N) | ERROR<br>output | WARNING<br>output |

| L               | L or H  | L or H           | HiZ_L<br>(Power down mode)        | Н               | Н                 |

| н               | L       | L or H           | HiZ_L<br>(Power down mode)        | Н               | н                 |

| н               | Н       | L                | HiZ_L<br>(MUTE ON)                | Н               | Н                 |

| н               | Н       | Н                | HiZ_L<br>(Latch)                  | L               | Н                 |

| RSTX    | PDX     | MUTEX   | WARNIN                            | G detection     |                   |

|---------|---------|---------|-----------------------------------|-----------------|-------------------|

| (51pin) | (50pin) | (49pin) | PWM output<br>(OUT1P, 1N, 2P, 2N) | ERROR<br>output | WARNING<br>output |

| L       | L or H  | L or H  | HiZ_L<br>(Power down mode)        | Н               | Н                 |

| н       | L       | L or H  | HiZ_L<br>(Power down mode)        | Н               | н                 |

| н       | Н       | L       | HiZ_L<br>(MUTE ON)                | Н               | Н                 |

| н       | Н       | Н       | HiZ_L                             | Н               | L                 |

\* RSTX, PDX and MUTEX pin are set Low, internal registers are initialized.

## (2) ADDR pin function

| ADDR<br>(54pin) | I <sup>2</sup> C BUS<br>Slave address |

|-----------------|---------------------------------------|

| L               | 80(hex)                               |

| Н               | 82(hex)                               |

\* ADDR pin is set to low level, internal resisters are initialized

#### (3) GAIN pin function

| GAIN2   | GAIN1   | Speaker output | Speaker output limitation power |

|---------|---------|----------------|---------------------------------|

| (48pin) | (47pin) | setting gain   | (*1)                            |

| L       | L       | 13.7dB         | 3.3W (THD+n=1%)                 |

| L       | Н       | 18.9dB         | 11.0W(THD+n=1%)                 |

| Н       | L       | 15.9dB         | 5.5W (THD+n=1%)                 |

| Н       | Н       | 20.7dB         | 16.5W (THD+n=1%)                |

\*1: It provides for the limitation power in the speaker output by the speaker maximum output when RL=8Ω, DSP=0dB, 0dBFS corresponding is input. Please set it according to the speaker used. 18dB, 20dB, 22dB, and 23dB can be set by the command besides the above-mentioned, set gain.

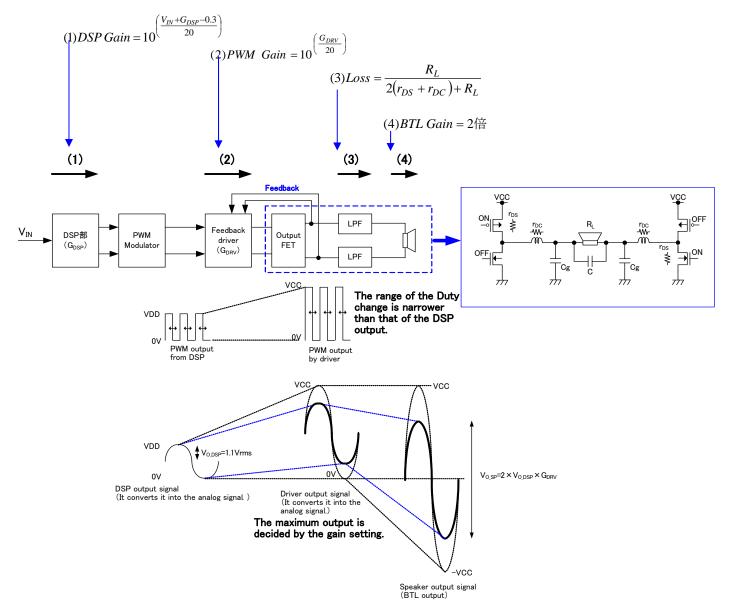

#### (4) Level diagram

$$\begin{split} V_{O\_DSP} &= \frac{VDD}{2\sqrt{2}} \left( 10^{\frac{V_{IN} + G_{DSP} - 0.3}{20}} \right) \quad \text{[Vrms]} \\ V_{O\_DSP} &= \frac{V_{O\_DSP}}{2\sqrt{2}} \left( 10^{\frac{V_{IN} + G_{DSP} - 0.3}{20}} \right) \times \frac{R_L}{2(r_{DS} + r_{DC}) + R_L} \times 2 \quad \text{[Vrms]} \\ V_{O\_SP} &= V_{O\_DSP} \times 10^{\left(\frac{G_{DRV}}{20}\right)} \times \frac{R_L}{2(r_{DS} + r_{DC}) + R_L} \times 2 \quad \text{[Vrms]} \\ P_{O(THD=1\%)} &= \frac{\left[ \frac{VDD}{2\sqrt{2}} \left( 10^{\frac{V_{IN} + G_{DSP} - 0.3}{20}} \right) \times 10^{\left(\frac{G_{DRV}}{20}\right)} \times \frac{R_L}{2(r_{DS} + r_{DC}) + R_L} \times 2 \quad \text{[Vrms]} \right]^2}{R_L} \\ \end{split}$$

## Datasheet

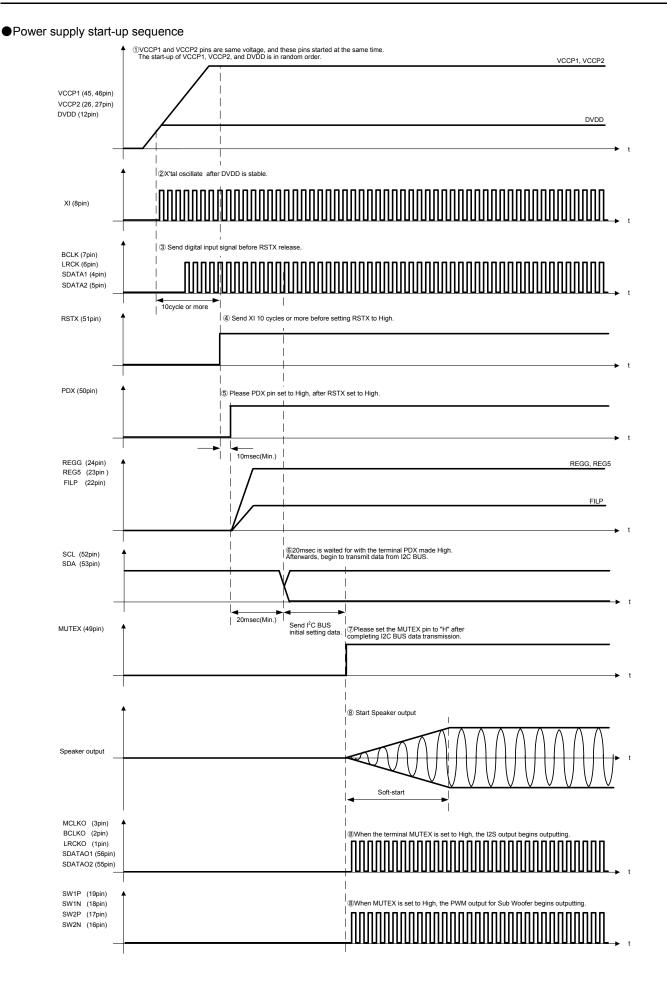

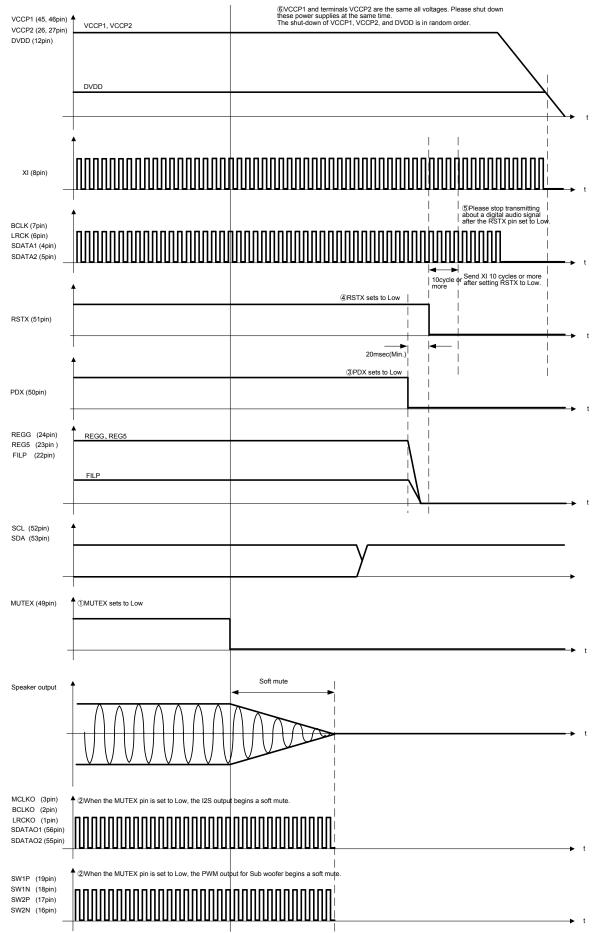

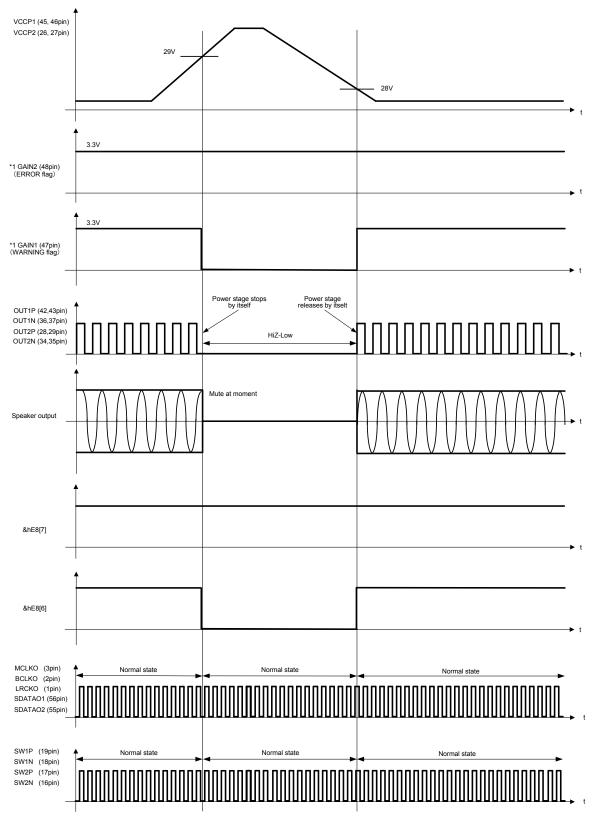

#### Power supply start-up sequence

#### •About the protection function

| Protection<br>function  |                     | Detecting & Releasing condition                             | Speaker<br>PWM output    | ERROR<br>flag output | WARNING flag output |

|-------------------------|---------------------|-------------------------------------------------------------|--------------------------|----------------------|---------------------|

| Output short protection | Detecting condition | Detecting current = 10A (TYP.)                              | HiZ_Low<br>(Latch)       | L                    | Н                   |

| DC voltage protection   | Detecting condition | Speaker PWM output fixes 40msec or more by Duty=0% or 100%. | HiZ_Low<br>(Latch)       | L                    | Н                   |

| High temperature        | Detecting condition | Chip temperature to be over 150°C (TYP.)                    | HiZ_Low<br>(Auto return) | н                    | L                   |

| protection              | Releasing condition | Chip temperature to be under 120°C (TYP.)                   | Normal                   | п                    | Н                   |

| Under voltage           | Detecting condition | Power supply voltage to be below 8V (TYP.)                  | HiZ_Low<br>(Auto return) | н                    | L                   |

| protection              | Releasing condition | Power supply voltage to be above 9V (TYP.)                  | Normal                   |                      | Н                   |

| Over voltage            | Detecting condition | Power supply voltage to be above 29V (TYP.)                 | HiZ_Low<br>(Auto return) | н                    | L                   |

| protection              | Releasing condition | Power supply voltage to be below 28V (TYP.)                 | Normal                   | П                    | Н                   |

| Clock stop              | Detecting condition | BCLK or LRCK stops 100µsec (default) or more stops.         | HiZ_Low<br>(Auto return) |                      | L                   |

| protection              | Releasing condition | BCLK and LRCK normal input it.                              | Normal                   | Н                    | Н                   |

\* It doesn't return automatically even if abnormal state is released when becoming a latch state. It is possible to release it by the method of the following ①or②.

①After the terminal MUTEX is made Low (10 time maintained in Low = msec(Min.)) once, it returns it to High again.

②Please reenter the power supply after it drops to power-supply voltage Vcc<3V that the internal power-on reset circuit operates (10msec(Min.) maintenance).

\* GAIN1 and GAIN2 pin can respectively be changed to the WARNING flag output pin and the ERROR flag output pin by the command.

\* The stop detection time of BCLK and LRCK can respectively be changed with &h09 and &h08.

Output selection of Stereo or Monaural on Main side.

Main side output can be set to stereo or monaural output. Initial value is set to "stereo output".

| Default = 0h | Defau | lt = | 0h |

|--------------|-------|------|----|

|--------------|-------|------|----|

| Select Address                                                               | Value | Explanation of operation                            | R/W  |  |  |  |  |

|------------------------------------------------------------------------------|-------|-----------------------------------------------------|------|--|--|--|--|

|                                                                              |       |                                                     |      |  |  |  |  |

|                                                                              | 0     | Stereo output on main side. (Normal BTL Output)     | R/W  |  |  |  |  |

| &hF0 [ 7 ]                                                                   | 1     | Monaural output on main side. (Parallel BTL Output) | K/VV |  |  |  |  |

| Places refer to the item of "Change of CAINIA and CAINIA ain "for other hite |       |                                                     |      |  |  |  |  |

Please refer to the item of "Change of GAIN1 and GAIN2 pin "for other bits.

| Defau | lt = | 01 | ſ |

|-------|------|----|---|

|       |      |    |   |

| Select Address | Value | Explanation of operation                           |     |  |  |

|----------------|-------|----------------------------------------------------|-----|--|--|

| &hF1 [ 7 ]     | 0     | Reserved. (This bit should be set to "0")          |     |  |  |

|                | 0     | Stereo output on main side. (Normal BTL Output)    |     |  |  |

| &hF1 [ 6 ]     | 1     | Monaural output on main side. (Parallel BT Output) | R/W |  |  |

| &hF1 [ 5:3 ]   | 0     | Reserved. (This bit should be set to "0")          | R/W |  |  |

| &hF1 [ 2:0 ]   | 1     | Transmit address                                   | R   |  |  |

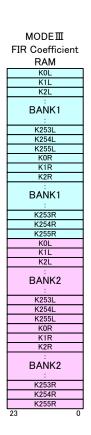

After it sets it as follows, Channel Mixer 2 is set to set it to monaural.

- (1) Write 1h to &hF0 [7] register.

- (2) Write 41h to &hF1 [7:0] register.

- (3) Write 01h to &hF8 [7:0] register.

When the Main side is output by the monaural output, the output of the DSP side is set to the monaural output with Channel Mixer 2. The example of setting that time is as follows.

- When you use L ch as a monaural output &h26 = 19h : L out set to L in, R out set to inverse L in.

- (2) When you use R ch as a monaural output &h26 = 2Ah : L out set to R in, R out set to inverse R in.

- (3) When you use L ch as a monaural output &h26 = 3Bh : L out set to (Lch + Rch)/2, R out set to inverse (Lch + Rch)/2.

\*Changing the stereo or monaural should be done after MUTEX terminal set to "L".

Please refer to "4-11. The channel setting with the phase reversing function" for details of Channel Mixer 2.

Output selection of Stereo or Monaural on Sub side.

The output of the Sub side can be set to the stereo or monaural as well as the Main side. An initial value is a stereo output. If the Sub side is monaural output, it should be set to monaural output by Channel Mixer 3 of the DSP. The example of setting that time is as follows.

- (1) When you use L ch as a monaural output &h27 = 19h : L out set to L in, R out set to inverse L in.

- (2) When you use R ch as a monaural output &h27 = 2Ah : L out set to R in, R out set to inverse R in.

- (3) When you use L ch as a monaural output &h27 = 3Bh : L out set to (Lch + Rch)/2, R out set to inverse (Lch + Rch)/2

\*Changing the stereo or monaural should be done after MUTEX terminal set to "L".

Please refer to "4-11. The channel setting with the phase reversing function" for details of Channel Mixer 3.

## •Change of GAIN1 and GAIN2 pin

After address &hF0 [3] is set to 1, it is necessary to set to 1 in &hF8 [0] to change the terminal GAIN1 and the terminal GAIN2 to the WARNING flag output and the ERROR flag output terminal respectively.

Moreover, the gain value can be changed by writing 1 in &hF8 [0] after the speaker output setting gain value also similarly sets the gain value to &hF0 [6:4]. Please set &hF0 [3] to 1 when you set the gain by this command.

Restrictions on output power supply for 3W speaker

| Default=00h    |       |                                                   | 1   |

|----------------|-------|---------------------------------------------------|-----|

| Select Address | Value | Explanation of operation                          | R/W |

| &hF0 [ 6 : 4 ] | 0     | 13.7dB<br>(Output power limitter for 3W speaker)  |     |

|                | 1     | 19.0dB<br>(Output power limitter for 10W speaker) |     |

|                | 2     | 15.9dB<br>(Output power limitter for 5W speaker)  |     |

|                | 3     | 20.7dB<br>(Output power limitter for 15W speaker) | R/W |

|                | 4     | 18.0dB                                            |     |

|                | 5     | 20.0dB                                            |     |

|                | 6     | 22.0dB                                            |     |

|                | 7     | 23.0dB                                            |     |

|                | 0     | Gain setting by external pin                      |     |

| &hF0 [ 3 ]     | 1     | Output flag setting for WARNING/ERROR             | R/W |

| &hF0 [ 2:0 ]   | 0     | Transmit address                                  | R   |

#### Default=0h

| Select Address | Value | Explanation of operation                                       | R/W |

|----------------|-------|----------------------------------------------------------------|-----|

|                | 0     | Force stop transmission invalid                                |     |

| &hF8 [ 1 ]     | 1     | Force stop transmission valid                                  | R/W |

|                | 0     | Stop transmission                                              |     |

| &hF8 [ 0 ]     | 1     | Start transmission<br>(This bit is cleared 0 by automatically) |     |

|                |       | (This bit is cleared 0 by automatically)                       |     |

\*The address from &hF1 to &hF7 is register for LSI test. Please don't access these register.

## •Reading of ERROR and WARNING flag with I<sup>2</sup>C

It is also possible to read it through  $I^2C$  I/F though WARNING and the ERROR flag can be output to the terminal GAIN1 and the terminal GAIN2 respectively. The reading address is as follows.

| Select Address | Value | Explanation of operation | R/W |

|----------------|-------|--------------------------|-----|

| &hE8 [ 7 ]     | 0     | ERROR state              | п   |

|                | 1     | Normal                   | R   |

| &hE8 [ 6 ]     | 0     | WARNING state            | ſ   |

|                | 1     | Normal                   | R   |

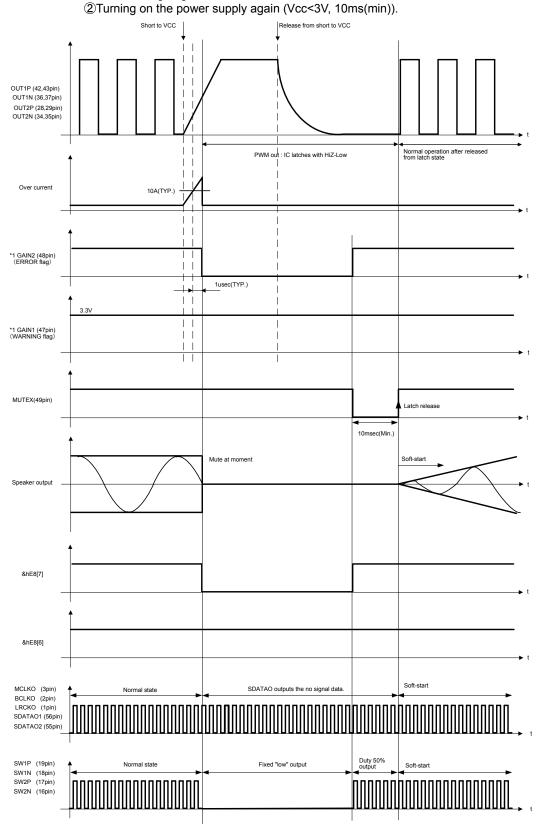

Output short protection (Short to the power supply)

This IC has the output short protection circuit that stops the PWM output when the PWM output is short-circuited to the power supply due to abnormality.

Detecting condition - It will detect when MUTEX pin is set High and the current that flows in the PWM output pin becomes 10A(TYP.) or more. The PWM output instantaneously enters the state of HiZ-Low if detected, and IC does the latch.

Releasing method - ①After MUTEX pin is set Low once over the soft mute transition time(Min.:10msec), MUTEX pin is returned to High again.

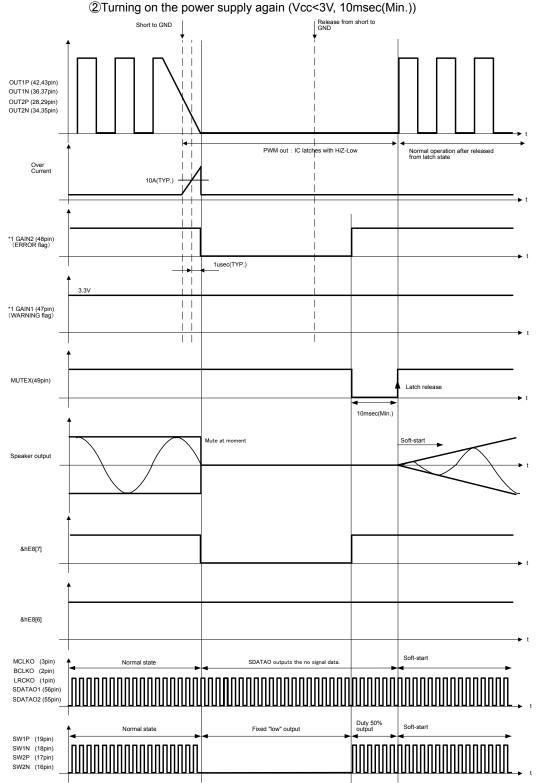

Output short protection (Short to GND)

This IC has the output short protection circuit that stops the PWM output when the PWM output is short-circuited to GND due to abnormality.

Detecting condition - It will detect when MUTEX pin is set High and the current that flows in the PWM output terminal becomes 10A(TYP.) or more. The PWM output instantaneously enters the state of HiZ-Low if detected, and IC does the latch.

Releasing method – ①After MUTEX pin is set Low once over the soft mute transition time(10msec(Min.)), MUTEX pin is returned to High again.

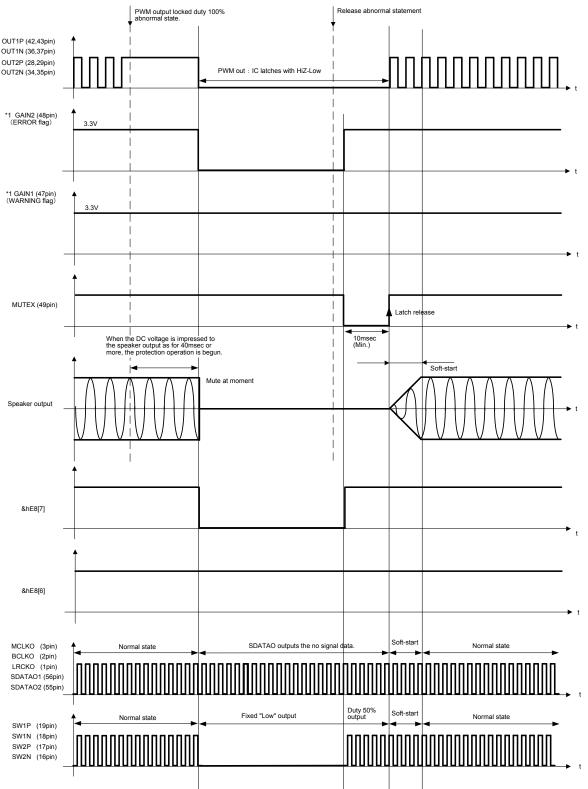

## DC voltage protection in the speaker

When the DC voltage in the speaker is impressed due to abnormality, this IC has the protection circuit where the speaker is defended from destruction.

Detecting condition - It will detect when MUTEX pin is set High and PWM output Duty=0% or 100% over 40msec. Once detected, The PWM output instantaneously enters the state of HiZ-Low, and IC does the latch.

Releasing method – ①After MUTEX pin is set Low once over the soft mute transition time(10msec(Min.)), MUTEX pin is returned to High again.

②Turning on the power supply again (Vcc<3V, 10msec(Min)).

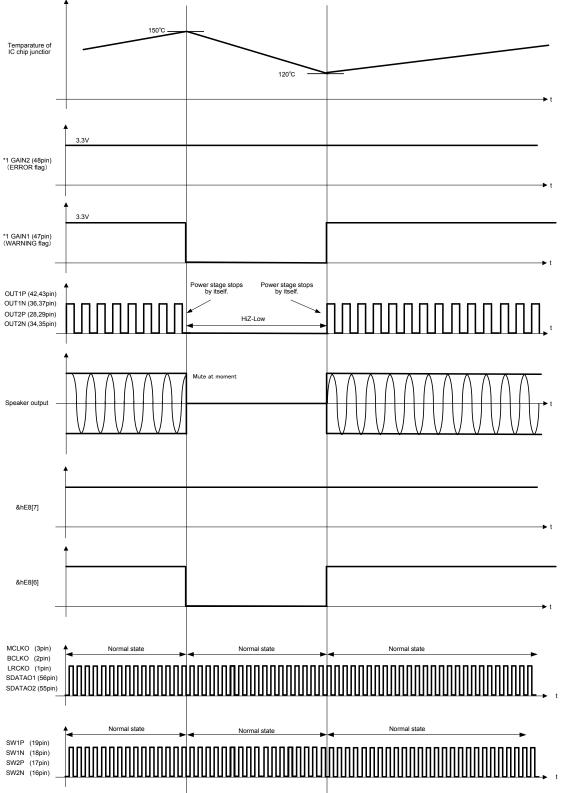

#### High temperature protection

This IC has the high temperature protection circuit that prevents thermal reckless driving under an abnormal state for the temperature of the chip to exceed Tjmax=150°C.

Detecting condition - It will detect when MUTEX pin is set to High and the temperature of the chip becomes 150°C(TYP.) or more. The speaker output is muted when detected.

Releasing condition - It will release when MUTEX pin is set High and the temperature of the chip becomes 120°C(TYP.) or less. The speaker output is outputted when released.

\* When the WARING outgoing signal of Sub Woofer is connected with the IN\_ERR pin of BM5449MWV, it is recognized ERROR in BM5449MWV.

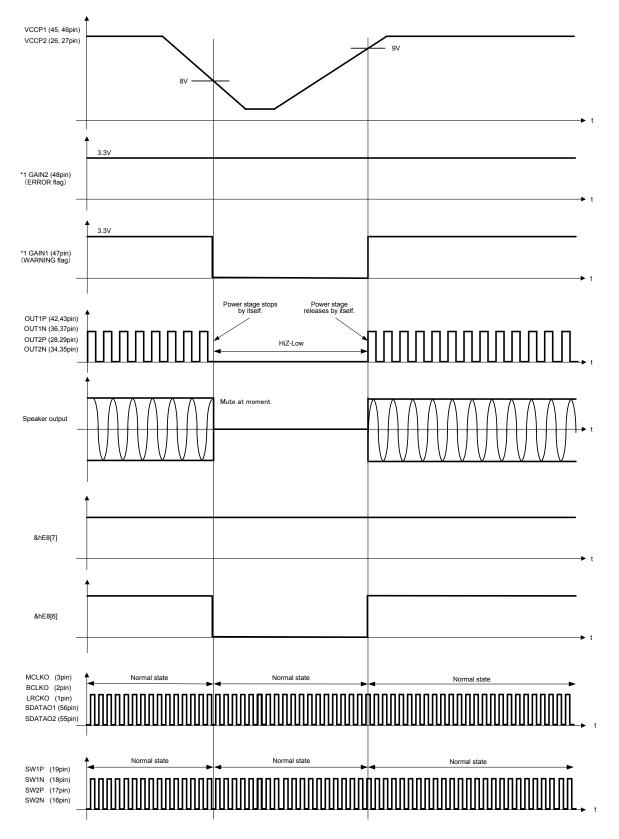

#### Under voltage protection

This IC has the under voltage protection circuit that make speaker output mute once detecting extreme drop of the power supply voltage.

Detecting condition – It will detect when MUTEX pin is set to High and the power supply voltage becomes lower than 8V. The speaker output is muted when detected.

Releasing condition – It will release when MUTEX pin is set to High and the power supply voltage becomes more than 9V. The speaker output is outputted when released

#### •Over voltage protectione

This IC has the over voltage protection circuit that make speaker output mute once detecting extreme drop of the ower supply voltage.

Detecting condition – It will detect when MUTEX pin is set High and the power supply voltage becomes more than 29V. The speaker output is muted when detected.

Releasing condition – It will release when MUTEX pin is set High and the power supply voltage becomes less than 28V. The speaker output is outputted when released.

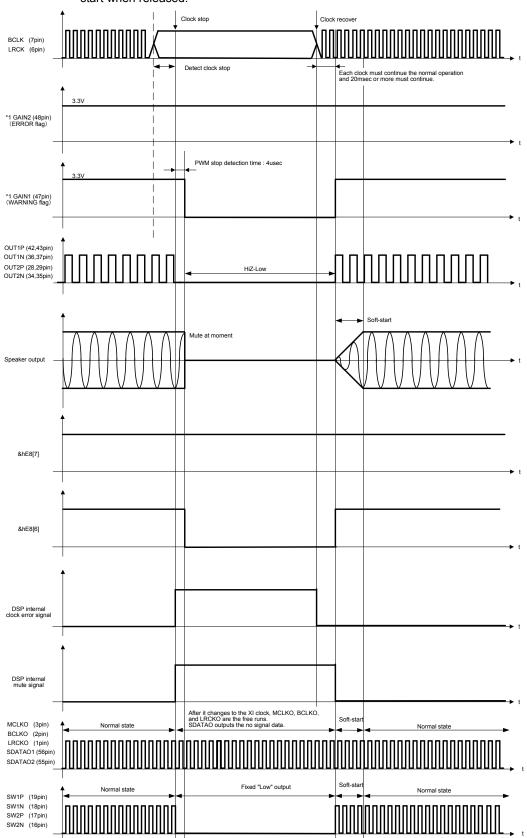

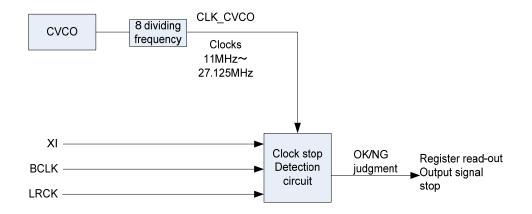

#### Clock stop protection

This IC has the clock stop protection circuit that make the speaker output mute when the BCLK and LRCLK frequency of the digital sound input are decreased.

Detecting condition - It enters the state of detection when BCLK or LRCK stops at 100 µsec or more when the MUTE pin is High. The speaker output instantaneously enters the state of HiZ-Low if detected. Releasing condition - A It enters the state of release if BCLK or LRCK returns to a normal clock motion when the terminal MUTEX is High. The speaker output returns to the signal output state through a soft start when released.

#### •DSP part Functional specification

1. Command Interface

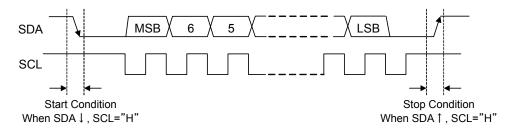

BM5449MWV uses I<sup>2</sup>C-bus system for the command interface with a host CPU.

The register of BM5449MWV has Write-mode and Read-mode.

BM5449MWV specifies a slave address and 1 byte of selection address, and it performs writing and read-back.

The slave mode format of  $I^2C$  bus is shown below.

|   | MSB         | LSB | Μ | SB           | LSB | MSE | 3    | LSB |   |   |

|---|-------------|-----|---|--------------|-----|-----|------|-----|---|---|

| S | Slave Addre | ess | А | Select Addre | ess | Α   | Data |     | А | Ρ |

S: Start condition

Slave Address: After the slave address (7 bits) set up by I2CADR, bit of a read-mode (H") and a write-mode (L") is attached, and a total of 8-bit data is sent. (MSB first)

A: Acknowledge an acknowledge bit is added on to each bit of data transmitted.

When data transmission is being done correctly, "L" is transmitted.

"H" transmission means there was no acknowledge.

Select Address: BM5449MWV uses a 1-byte select address. (MSB first)

Data:Data byte, transmitted data (MSB first)P:Stop condition

#### 1-1. Data Write-In

| S SI  | ave Ado | lress | A    | Select    | Address | ;  | A D  | ata       |              | A P          |        |             |     |   |

|-------|---------|-------|------|-----------|---------|----|------|-----------|--------------|--------------|--------|-------------|-----|---|

|       | Ļ       |       |      |           |         |    | : N  | laster to | o Slave      | Slave        | e to l | Master      |     |   |

| ADDR= | 0       |       |      |           |         |    |      | 5         | Setting of E | 3M5449 slave | add    | lress       |     |   |

| MSB   |         |       | 1    | 1         |         |    | LS   | SВ        | Termir       | nal setting  |        | Write-mod   | e   | ] |

| A6    | A5      | A4    | A3   | A2        | A1      | A0 | R/W  |           |              | .DDR         |        | Slave-addre | ess |   |

| 1     | 0       | 0     | 0    | 0         | 0       | 0  | 0    |           |              | 0            |        | 80h         |     | 1 |

| ADDR= | 1       |       |      |           |         |    |      |           |              | 1            |        | 82h         |     |   |

| MSB   |         |       |      |           |         |    | LS   | BB        |              |              |        |             |     |   |

| A6    | A5      | A4    | A3   | A2        | A1      | A0 | R/W  |           |              |              |        |             |     |   |

| 1     | 0       | 0     | 0    | 0         | 0       | 1  | 0    |           |              |              |        |             |     |   |

|       |         |       |      |           |         |    |      |           |              |              |        |             |     |   |

| S SI  | ave Ado | lress | A Se | elect Add | dress   | Α  | Data |           | A Data       | а            | Α      | Data        | A   | Ρ |

| (ex.) | 80ł     | ו     |      | 20h       |         |    | 00   | ٦         |              | 00h          |        | 00h         |     |   |

|       |         |       |      |           |         |    | : N  | laster to | o Slave      | Slav         | ve to  | Master      |     |   |

#### Write-in Procedure

| Step | Clock | Master          | Slave(BM5449) | Note                           |

|------|-------|-----------------|---------------|--------------------------------|

| 1    |       | Start Condition |               |                                |

| 2    | 7     | Slave Address   |               |                                |

| 3    | 1     | R/W (0)         |               | &h80 (&h82)                    |

| 4    | 1     |                 | Acknowledge   |                                |

| 5    | 8     | Select Address  |               | Write-in target register: 8bit |

| 6    | 1     |                 | Acknowledge   |                                |

| 7    | 8     | Data            |               | 8bit write-in data             |

| 8    | 1     |                 | Acknowledge   |                                |

| 9    |       | Stop Condition  |               |                                |

OWhen transmitting continuous data, the auto-increment function moves the select address up by one.

Repeat steps 7 and 8.

#### 1-2. Data Read-Out

During read-out, the corresponding read-out address is first written into the &hD0 address register (&h20h in the example). In the following stream, the data is read out after the slave address. Do not return an acknowledge after completing the reception.

| S    | Slave Address | Α | Req_Addr | Α | Select Address | Α | Ρ | ]            |

|------|---------------|---|----------|---|----------------|---|---|--------------|

| Ex.) | 80h           |   | D0h      |   | 20h            |   |   |              |

|      |               |   |          |   |                |   |   |              |

| S    | Slave Address | Α | Data 1   | Α | Data 2         | А |   | A Data N Ā P |

EX.) 81n "In The State of Master A: With acknowledge, Ā:Without acknowledge

#### Read-out Procedure

| Step | Clock | Master          | Slave(BM5449) | Note                                   |

|------|-------|-----------------|---------------|----------------------------------------|

| 1    |       | Start Condition |               |                                        |

| 2    | 7     | Slave Address   |               | 8600 (8600)                            |

| 3    | 1     | R/W (0)         |               | &h80 (&h82)                            |

| 4    | 1     |                 | Acknowledge   |                                        |

| 5    | 8     | Req_Addr        |               | I <sup>2</sup> C read-out address &hD0 |

| 6    | 1     |                 | Acknowledge   |                                        |

| 7    | 8     | Select Address  |               | Read-out target register: 8bit         |

| 8    | 1     |                 | Acknowledge   |                                        |

| 9    | 1     | Stop Condition  |               |                                        |

| 10   | 1     | Start Condition |               |                                        |

| 11   | 7     | Slave Address   |               | 8604 (8602)                            |

| 12   | 1     | R/W (1)         |               | &h81 (&h83)                            |

| 13   | 1     |                 | Acknowledge   |                                        |

| 14   | 8     |                 | Data          | 8bit read-out data                     |

| 15   | 1     | Acknowledge     |               |                                        |

| 16   |       | Stop Condition  |               |                                        |

OWhen transmitting continuous data, the auto-increment function moves up the select address by one. Repeat steps 14 and 15. 1-3. Control Signal Specifications

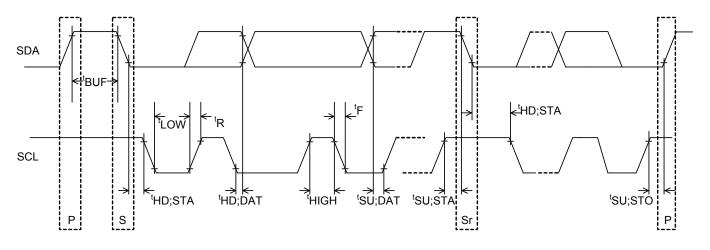

OElectrical Characteristics and Timing for Bus Line and I/O Stage

Figure 31. Timing Chart

| Table 1-1: SDA and SCL | Bus Line Characteristics | (Ta=25°C and DVDD=3.3V) |

|------------------------|--------------------------|-------------------------|

|                        | Buo Ento onaraotoriotico |                         |

| Parameters |                                                        | Qumbal  | High-Speed Mode  |      |      |

|------------|--------------------------------------------------------|---------|------------------|------|------|

|            |                                                        | Symbol  | Min.             | Max. | Unit |

| 1          | SCL clock frequency                                    | fSCL    | 0                | 400  | kHz  |

| 2          | Bus free time between "stop" condition and             |         | 1.3              | -    | μs   |

| 2          | "start" condition                                      | tBUF    |                  |      |      |

| 0          | Hold time (re-transmit) "start" condition.             | tHD;STA | 0.6              | -    | μs   |

| 3          | After this period, the first clock pulse is generated. |         |                  |      |      |

| 4          | SCL clock LOW state hold time                          | tLOW    | 1.3              | -    | μs   |

| 5          | SCL clock HIGH state hold time                         | tHIGH   | 0.6              | -    | μs   |

| 6          | Re-transmit set-up time of "start" condition           | tSU;STA | 0.6              | -    | μs   |

| 7          | Data hold time                                         | tHD;DAT | 0 <sup>1)</sup>  | -    | μs   |

| 8          | Data setup time                                        | tSU;DAT | 2/(XI frequency) | -    | ns   |

| 9          | SDA and SCL signal stand-up time                       | tR      | 20+0.1Cb         | 300  | ns   |

| 10         | SDA and SCL signal stand-down time                     | tF      | 20+0.1Cb         | 300  | ns   |

| 11         | Set-up time for "stop" condition                       | tSU;STO | 0.6              | -    | μS   |

| 12         | Each bus line's capacitive load                        | Cb      | -                | 400  | pF   |

The values above correspond with  $V_{\text{IH}\,\text{min}}$  and  $V_{\text{IL}\,\text{max}}$  levels.

1) Because the transmission device exceeds the undefined domain of the SCL fall edge, it is necessary to internally provide a minimum

300ns hold time for the SDA signal (of  $V_{IH min}$  of SCL signal).

The above-mentioned characteristic is a theory value in IC design and it doesn't be guaranteed by shipment inspection. When problem occurs by any chance, we talk in good faith and correspond. Neither terminal SCL nor terminal SDA correspond to 5V tolerant. Please use it within absolute maximum rating 4.5V.

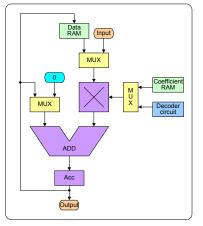

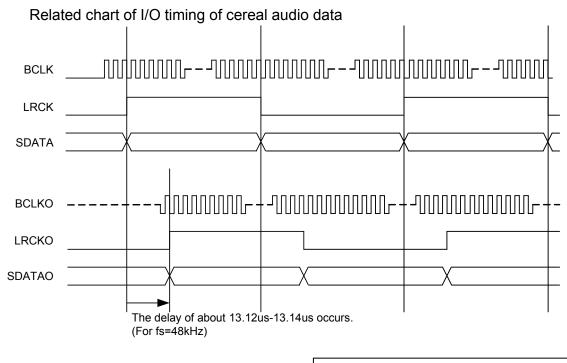

## 2. Data and system clock distribution diagram

The audio input data and audio output data distribution diagram of BM5449MWV is shown below.

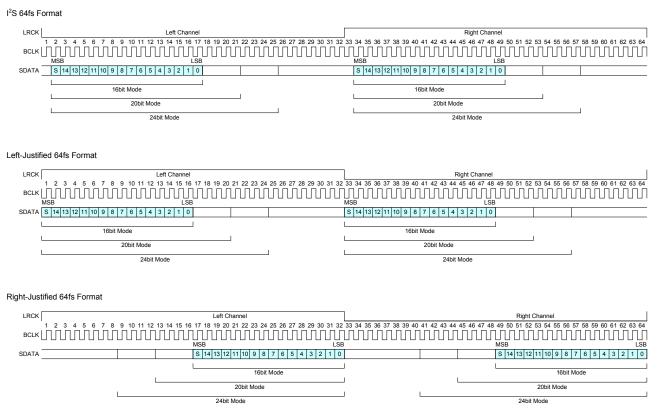

#### 3. S-P conversion

In BM5449MWV, the conversion circuit from serial data to parallel data is built in.

S-P conversion is blocks which receive 3-line serial input audio data from pins and convert it to parallel data.

The three input formats are IIS, left-justified and right-justified. The bit clock frequency may be selected from either 64fs or 48fs or 32fs. 16bit, 20bit and 24bit output may be selected for each format.

The timing chart of each transmission mode is shown in the following figure.

## Bit clock frequency: 64fs form

I<sup>2</sup>S 64fs Format

20bit Mode

24bit Mode

20bit Mode

24bit Mod

## Bit clock frequency: 48fs form

20bit Mode

24hit Mode

#### Bit clock frequency: 32fs form

20bit Mode

24bit Mode

3-1. Timing reset setup of input 3-line serial data circuit

After changing into parallel data from serial data, the timing which takes in data is adjusted.

(Synchronization)

This function is used when the time of power supply starting of IC and an input sampling rate change or 3-line serial-data input format change.

When data taking-in timing shifts more than fixed, it adjusts automatically.

Default = 0

| Select Address | Value | Explanation of operation            |

|----------------|-------|-------------------------------------|

| &h03 [6]       | 0     | Auto adjustment function is invalid |

|                | 1     | Auto adjustment function is valid   |

It resets by &h04[0] = 1 after the stability of PLLA.

This Resister is cleared automatically, after Reset function is finished.

| Select Address | Value | Explanation of operation  |

|----------------|-------|---------------------------|

| &h04 [0]       | 1     | Synchronous counter reset |

## 3-2. Bit clock frequency setup of 3-line serial-data input

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h03 [5:4]     | 0     | 64fs form                |

|                | 1     | 48fs form                |

|                | 2     | 32fs form                |

#### 3-3. Serial data format

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h03 [3:2]     | 0     | IIS format               |

|                | 1     | Left-justified format    |

|                | 2     | Right-justified format   |

## 3-4. Data bit width

## Default = 2

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h03 [1:0]     | 0     | 16 bit                   |

|                | 1     | 20 bit                   |

|                | 2     | 24 bit                   |

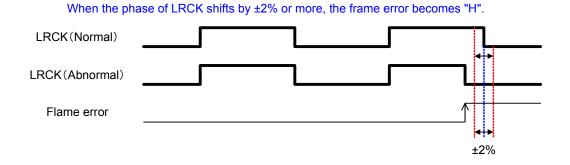

# 3-5. LRCK flame error flag

Setting the number of times of the conclusion of the LRCK frame error

When detecting a frame error above the number of times which was set here, &h04 [2] becomes "1".

#### Default = 1h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h04 [6:4]     | 0     | Inhibit                  |

|                | 1     | 1 time                   |

|                | 2     | 2 times                  |

|                | :     | :                        |

|                | 7     | 7 times                  |

Please set to 1h or more

#### The flame error is read out by &h04 [2].

| Select Address | Value | Explanation of operation    |

|----------------|-------|-----------------------------|

| &h04 [2]       | 0     | Normal                      |

|                | 1     | Detect the LRCK flame error |

It clears the LRCK frame error flag which latches in executing &h04 [1] command.

Operation is automatically cleared about the register after complete.

Default = 0

| Select Address | Value | Explanation of operation        |

|----------------|-------|---------------------------------|

| &h04 [1]       | 0     | Normal                          |

|                | 1     | Clear the LRCK flame error flag |

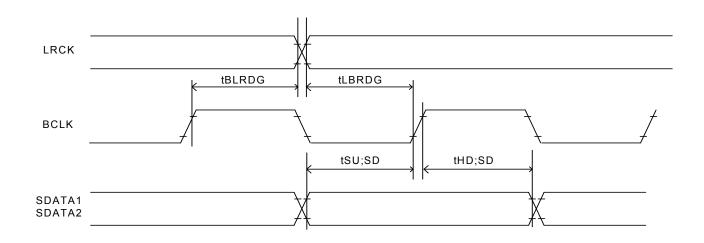

# 3-6. Audio interface signal specification

OElectric specification and timings of BCLK,LRCK and SDATA

|                      | Davaa                                                      | -4          | Symbol |        |      | 11.1 |

|----------------------|------------------------------------------------------------|-------------|--------|--------|------|------|

|                      | Parameter                                                  |             |        | Min.   | Max. | Unit |

| 1                    | LDOK                                                       | Frequency   | fLRCK  | 8      | 96   | kHz  |

| 2                    | LRCK                                                       | DUTY        | dLRCK  | 40     | 60   | %    |

| 3                    |                                                            | Cycle       | tBCK   | 162.76 | -    | ns   |

| 4                    | BCLK                                                       | Hi Section  | tBCKH  | 65     | -    | ns   |

| 5                    |                                                            | Low Section | tBCKL  | 65     | -    | ns   |

| 6                    | 6 Time from the rising edge of BCLK to the edge of LRCK *1 |             |        | 20     | -    | ns   |

| 7                    | 7 Time from the edge of LRCK to the rising edge of BCLK *1 |             |        | 20     | -    | ns   |

| 8                    | 8 Setup time of SDATA                                      |             |        | 20     | -    | ns   |

| 9 Hold time of SDATA |                                                            | tHD;SD      | 20     | -      | ns   |      |

$^{\ast}1$  This standard value has specified that the edge of LRCK and the rising edge of BCLK do not overlap.

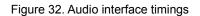

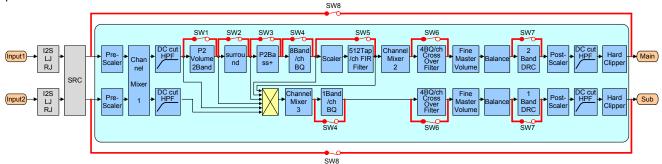

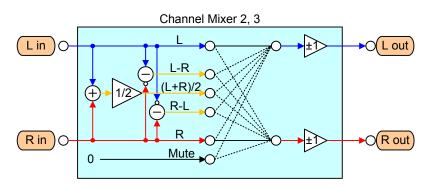

4. Digital Sound Processing (DSP)

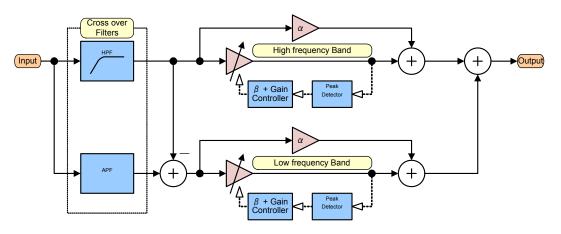

The digital sound processing (DSP) part of BM5449MWV is composed of the special hard ware which is the optimal for FPD-TV, the Mini/Micro Compo. BM5449MWV does the following processing using this special DSP. Pre-scaler, Channel mixer, DC cut HPF, P2Volume, Surround, P2Bass+, 8 Band P-EQ, 512Tap FIR,

Cross Over Filter, Fine Master Volume, Balance Volume, 2 Band DRC, Post-scaler, Hard Clipper

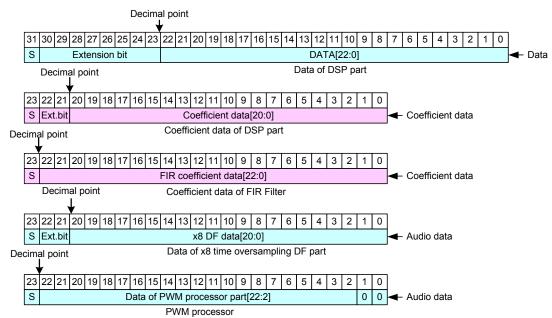

The outline and signal flow of the DSP part

| Data width:          | 32 bit (DATA RAM)                      |

|----------------------|----------------------------------------|

| Machine cycle:       | 20.3ns (1024fs, fs=48kHz)              |

| Multiplier:          | $32 \times 24 \rightarrow 56$ bit      |

| Adder:               | $56+56 \rightarrow 56$ bit             |

| Data RAM:            | 512×32 bit                             |

| Coefficient RAM:     | 512×24 bit                             |

| Sampling frequency : | fs=8k, 11.025k, 12k, 16k, 22.05k, 32k, |

|                      | 44.1k, 48k, 88.2k, 96k, 176.4k, 192kHz |

|                      |                                        |

The input sampling frequency is converted into 48kHz or 44.1kHz in SRC.

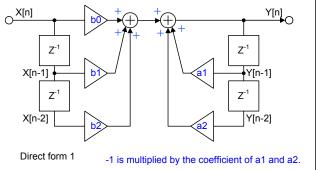

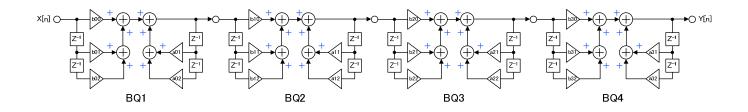

The digital signal from 16 bits to 24 bits is inputted to the DSP but extends 8bit (+42dB) as the overflow margin to the upper side. When doing the processing which exceeds this range, it processes a clip in the DSP. Incidentally, in case of the 2nd IIR-type (BQ) filter which is often used generally as the digital filter, because it consumes a lot of overflow margins, the output of the multiplier and the adder inside needs note.

The output of multipliers and the adding machine might exceed +48dB by the coefficient of a1, a2, b0, b1, and b2. In that case, data becomes saturation power. Therefore, the output of the filter cannot obtain the aimed characteristic.

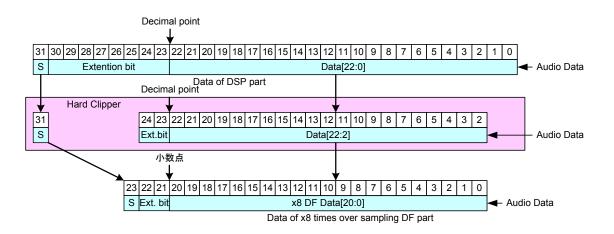

The management of audio data is as follows by each block.

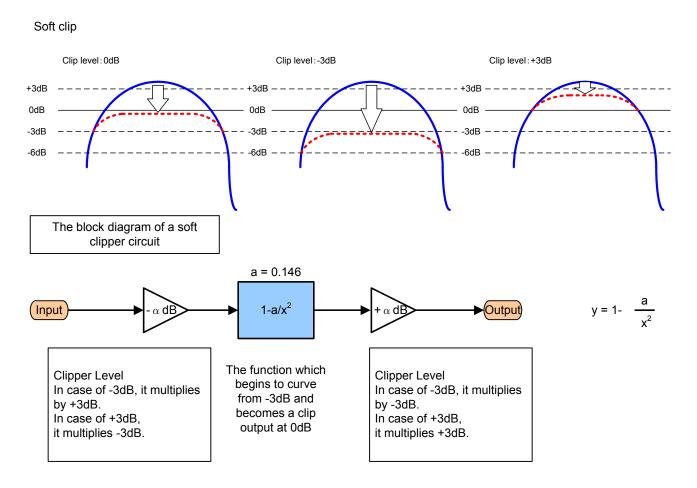

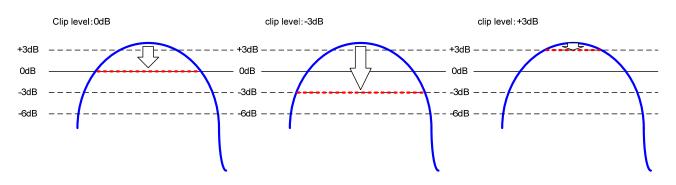

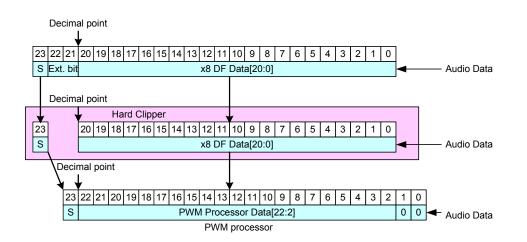

It is using 2 bits of extension of 8 times over sampling parts for the calculation by the soft clipper function.

It is 2 bits shifted to the upper side when delivering data to the PWM processor, it makes up of 0 and it delivers 0 to 2 bits of lower ranks as the 24-bit data.

#### 4-1. Bypass

It passes in the each function of the DSP by the command. Because it left the set value of the each function can be passed in, it is possible to do the confirmation of ON/OFF of the sound effect easily.

The effect which is possible about the bypass, 1) P2Volume, 2) The surround 3) P2Bass + (The suspected low voice), 4) 8Band BQ/1Band BQ, 5) 512 Tap FIR Filter, 6) 4 BQ Cross Over Filter, 7)2Band DRC/1Band DRC and the whole DSP can be passed.

| S١ |

|----|

| Select Address | bit | Explanation of operation                      |

|----------------|-----|-----------------------------------------------|

| &h02 [ 7:0 ]   | 7   | Bypass of P <sup>2</sup> Volume(SW1)          |

|                | 7   | 0 : Nomal, 1 : Bypass                         |

|                | 6   | Bypass of Surround(SW2)                       |

|                | 0   | 0 : Normal, 1: Bypass                         |

|                | 5   | Bypass of P <sup>2</sup> Bass+(SW3)           |

|                | 5   | 0 : Normal, 1 : Bypass                        |

|                | 4   | Bypass of 8Band/1Band BQ(SW4)                 |

|                | 4   | 0 : Normal, 1 : Bypass                        |

|                | 3   | Bypass of Scaler and 512 Taps FIR Filter(SW5) |

|                |     | 0 : Normal, 1 : Bypass                        |

|                | 2   | Bypass of 4 BQ Cross Over Filter(SW6)         |

|                | 2   | 0 : Normal, 1 : Bypass                        |

|                | 1   | Bypass of 2 Band/1Band DRC(SW7)               |

|                |     | 0 : Normal, 1 : Bypass                        |

|                | 0   | Bypass of the whole DSP(SW8)                  |

|                | 0   | 0 : Normal, 1 : Bypass                        |

Default = 00h

### 4-2. Pre-scaler

To overflow when the level sometimes is full scale entry in case of the digital signal which is inputted to the sound DSP and does surround and equalizer processing, it adjusts an entry gain with Pre-scaler. The adjustable-range can be set from +48 dB to -79 dB with the 0.5-dB step. (Lch/Rch concurrency control)

Pre-scaler doesn't have a soft transfer feature. Input1 and Input2 become an independent control.

| Default = 60h |

|---------------|

|---------------|

| Select Address      | Explanation   | n of operation |

|---------------------|---------------|----------------|

| Input1 &h21 [ 7:0 ] | Command Value | Gain           |

| Input2 &h22 [ 7:0 ] | 00            | +48dB          |

|                     | 01            | +47.5dB        |

|                     | :             | :              |

|                     | 60            | 0dB            |

|                     | 61            | -0.5dB         |

|                     | 62            | -1dB           |

|                     | :             | ÷              |

|                     | FE            | -79dB          |

|                     | FF            | -∞             |

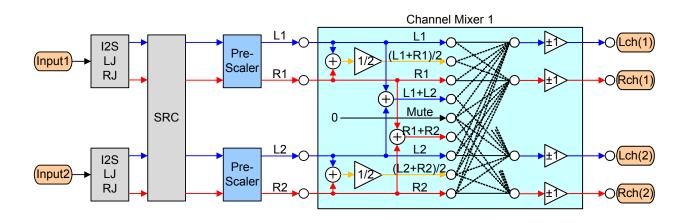

4-3. Channel setup with a phase inversion function (Channel Mixer 1)

It sets a mixing in the sound on the left channel and the right channel of the digital signal which was inputted to the DSP. It makes a stereo signal a monaural here. Also, the phase-inversion, the mute on each channel can be set. The sound of Input1 and Input2 can be replaced and be added, too.

DSP Input1: The data inputted into Lch (1) of DSP is inverted.

Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h24 [7]       | 0     | Normal                   |

|                | 1     | Invert                   |

DSP Input1: The data inputted into Lch (1) of DSP is mixed.

Default = 1

| Select Address | Value | Explanation of operation    |

|----------------|-------|-----------------------------|

| &h24 [ 6:4 ]   | 0     | Mute                        |

|                | 1     | Input Lch(1)                |

|                | 2     | Input Rch(1)                |

|                | 3     | Input (Lch(1) + Rch(1)) / 2 |

|                | 4     | Input Lch(2)                |

|                | 5     | Input Rch(2)                |

|                | 6     | Input (Lch(2) + Rch(2)) / 2 |

|                | 7     | Input Lch(1) + Lch(2)       |

DSP Input1: The data inputted into Rch (1) of DSP is inverted.

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h24 [3]       | 0     | Normal                   |

|                | 1     | Invert                   |

DSP Input1: The data inputted into Rch (1) of DSP is mixed.

Default = 2

| Select Address | Value | Explanation of operation    |

|----------------|-------|-----------------------------|

| &h24 [ 2:0 ]   | 0     | Mute                        |

|                | 1     | Input Lch(1)                |

|                | 2     | Input Rch(1)                |

|                | 3     | Input (Lch(1) + Rch(1)) / 2 |

|                | 4     | Input Lch(2)                |

|                | 5     | Input Rch(2)                |

|                | 6     | Input (Lch(2) + Rch(2)) / 2 |

|                | 7     | Input Lch(1) + Lch(2)       |

DSP Input2: The data inputted into Lch (2) of DSP is inverted.

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h25 [7]       | 0     | Normal                   |

|                | 1     | Invert                   |

DSP Input2: The data inputted into Lch (2) of DSP is mixed.

# Default = 4

| Select Address | Value | Explanation of operation    |  |

|----------------|-------|-----------------------------|--|

| &h25 [ 6:4 ]   | 0     | Mute                        |  |

|                | 1     | Input Lch(1)                |  |

|                | 2     | Input Rch(1)                |  |

|                | 3     | Input (Lch(1) + Rch(1)) / 2 |  |

|                | 4     | Input Lch(2)                |  |

|                | 5     | Input Rch(2)                |  |

|                | 6     | Input (Lch(2) + Rch(2)) / 2 |  |

|                | 7     | Input Lch(1) + Lch(2)       |  |

DSP Input2: The data inputted into Rch (2) of DSP is inverted.

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h25 [3]       | 0     | Normal                   |

|                | 1     | Invert                   |

# DSP Input2: The data inputted into Rch (2) of DSP is mixed.

| Default | = | 5 |  |

|---------|---|---|--|

|         |   |   |  |

| Select Address | Value | Explanation of operation    |

|----------------|-------|-----------------------------|

| &h25 [ 2:0 ]   | 0     | Mute                        |

|                | 1     | Input Lch(1)                |

|                | 2     | Input Rch(1)                |

|                | 3     | Input (Lch(1) + Rch(1)) / 2 |

|                | 4     | Input Lch(2)                |

|                | 5     | Input Rch(2)                |

|                | 6     | Input (Lch(2) + Rch(2)) / 2 |

|                | 7     | Input Lch(1) + Lch(2)       |

# 4-4. 1st HPF for DC cut

It cuts the DC offset component of the digital signal which is inputted to the sound DSP with this HPF. The cut off frequency fc of HPF is using 1 Hz and the degree is using the 1st filter.

#### Default = 1

| Select Address    | Value | Explanation of operation |

|-------------------|-------|--------------------------|

| Input1 &h28 [ 3 ] | 0     | Not use DC cut HPF       |

| Input2 &h28 [ 2 ] | 1     | Use DC cut HPF           |

# 4-5. 2 Band P<sup>2</sup>Volume

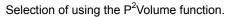

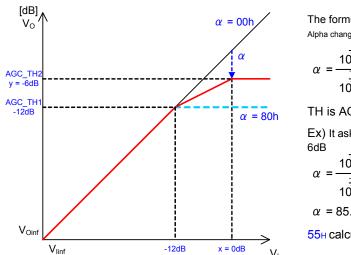

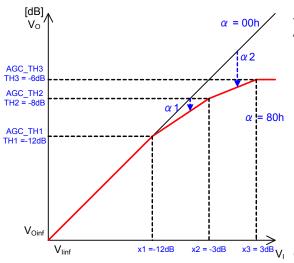

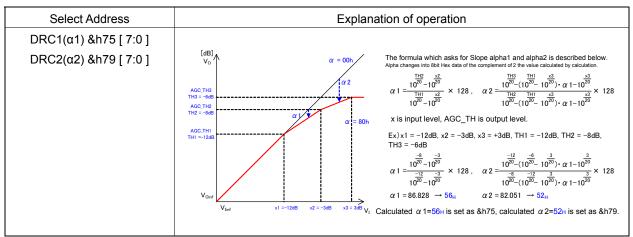

When the sound suddenly grows like blasts that exist in the TV commercial and the action picture, the volume is automatically controlled. Moreover, a sound small as the serif can be caught even if the volume is squeezed in the bedroom of nighttime is enlarged, and the loud sound is suppressed. The compression can operate each two bands (the low and the high pass). Use as one band is also possible according to the command setting. Moreover, it is also possible that the sound below the set value is soft muted.

2 Band P<sup>2</sup>Volume

It works, dividing  $P^2$ Volume feature into the area of 1 and 2 and 3 according to the input level.

① V<sub>linf</sub>(-∞) - V<sub>lmin</sub>

It prevents P<sup>2</sup>Volume feature's generating noise.

(2) Input level is more than  $V_{Imin,}$  and Output level is less than  $V_{omax}$

$$V_0 = V_1 + \beta$$

β: It lifts the whole power level for offset value beta.

③ When power level V<sub>O</sub> exceeds V<sub>omax</sub>

$$V_{O} = \alpha \cdot V_{I} + \beta$$

$\alpha$ : The inclination to suppress a D-range (P2V\_ $\alpha$ )

The power level can be made constant, too.

Default = 0

| Select Address | Value | Explanation of operation               |

|----------------|-------|----------------------------------------|

| &h02 [ 7 ]     | 0     | Use P <sup>2</sup> Volume function     |

|                | 1     | Not use P <sup>2</sup> Volume function |

Vo /

V<sub>Oma</sub>

$V_{\mathsf{Omi}}$

$V_{Imin}$

P2V MIN

P2V MAX

0dB

Selection of using the 2 Band P<sup>2</sup>Volum function for high frequency

Default = 0

| Select Address | Value | Explanation of operation                                            |  |

|----------------|-------|---------------------------------------------------------------------|--|

| &h40 [ 7 ]     | 0     | Not use the 2 Band P <sup>2</sup> Volum function for high frequency |  |

|                | 1     | Use the 2 Band P <sup>2</sup> Volum function for high frequency     |  |

Selection of using the 2 Band P<sup>2</sup>Volum function for high frequency

Default = 0

| Select Address | Value | Explanation of operation                                           |  |

|----------------|-------|--------------------------------------------------------------------|--|

| &h40 [ 6 ]     | 0     | Not use the 2 Band P <sup>2</sup> Volum function for low frequency |  |

|                | 1     | Use the 2 Band P <sup>2</sup> Volum function for high frequency    |  |

[Attention] It uses it only for the high frequency when using it as 1Band P2Volume.

Selection of using soft mute when the small signal inputs in operating P<sup>2</sup>Volum.

Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h41 [ 2 ]     | 0     | Not mute                 |

|                | 1     | Mute                     |

&h56 and the &h57 command adjust to the setting when attacking and releasing it.

The setting of  $V_{\text{Imin}}$

As for P2V\_MIN, to cancel that noise and so on are lifted by P2Volume, P2Volume sets a functioning minimum level. Default = 00h

| Select Address              |         |       | Explar  | nation of | operatio | n     |         |       |

|-----------------------------|---------|-------|---------|-----------|----------|-------|---------|-------|

| for high freq. &h54 [ 4:0 ] | Command | Gain  | Command | Gain      | Command  | Gain  | Command | Gain  |

| for low freq. &h5C [ 4:0 ]  | 00      | -00   | 08      | -76dB     | 10       | -60dB | 18      | -44dB |

|                             | 01      | -90dB | 09      | -74dB     | 11       | -58dB | 19      | -42dB |

|                             | 02      | -88dB | 0A      | -72dB     | 12       | -56dB | 1A      | -40dB |

|                             | 03      | -86dB | 0B      | -70dB     | 13       | -54dB | 1B      | -38dB |

|                             | 04      | -84dB | 0C      | -68dB     | 14       | -52dB | 1C      | -36dB |

|                             | 05      | -82dB | 0D      | -66dB     | 15       | -50dB | 1D      | -34dB |

|                             | 06      | -80dB | 0E      | -64dB     | 16       | -48dB | 1E      | -32dB |

|                             | 07      | -78dB | 0F      | -62dB     | 17       | -46dB | 1F      | -30dB |

The setting of  $V_{\text{omax}}$

P2V\_MAX sets an output suppression level. The input level VI when  $\alpha$  setting "80h"

When  $\alpha$ =80h (slope 0) is set, output power level V<sub>omax</sub> at level VI=0dB input time is shown.

Default = 40h

| Select Address                  | Explanation of operation |           |  |  |  |  |

|---------------------------------|--------------------------|-----------|--|--|--|--|

| High frequency band &h50[ 6:0 ] | Command                  | Threshold |  |  |  |  |

|                                 | 00                       | -32dB     |  |  |  |  |

| Low frequency band &h58[ 6:0 ]  | :                        | :         |  |  |  |  |

|                                 | ЗF                       | -0.5dB    |  |  |  |  |

|                                 | 40                       | 0dB       |  |  |  |  |

|                                 | 41                       | +0.5dB    |  |  |  |  |

|                                 | :                        | :         |  |  |  |  |

|                                 | 58                       | +12dB     |  |  |  |  |

|                                 |                          |           |  |  |  |  |

|                                 |                          |           |  |  |  |  |

# $\alpha$ setting

$\boldsymbol{\alpha}$  sets the slope of D range.

#### Default = 00h

# $\beta$ setting

A small voice is made the offset level  $\beta$  easy to hear by lifting the entire output power level.

Default = 18h

| Select Address                |         | Explanation of operation |         |       |         |       |         |       |  |

|-------------------------------|---------|--------------------------|---------|-------|---------|-------|---------|-------|--|

| High frequency band &h55[4:0] | Command | Gain                     | Command | Gain  | Command | Gain  | Command | Gain  |  |

|                               | 00      | 0dB                      | 08      | +8dB  | 10      | +16dB | 18      | +24dB |  |

| Low frequency band &h5D[4:0]  | 01      | +1dB                     | 09      | +9dB  | 11      | +17dB | 19      | -     |  |

|                               | 02      | +2dB                     | 0A      | +10dB | 12      | +18dB | 1A      | -     |  |

|                               | 03      | +3dB                     | 0B      | +11dB | 13      | +19dB | 1B      | -     |  |

|                               | 04      | +4dB                     | 0C      | +12dB | 14      | +20dB | 1C      | -     |  |

|                               | 05      | +5dB                     | 0D      | +13dB | 15      | +21dB | 1D      | -     |  |

|                               | 06      | +6dB                     | 0E      | +14dB | 16      | +22dB | 1E      | -     |  |

|                               | 07      | +7dB                     | 0F      | +15dB | 17      | +23dB | 1F      | -     |  |

[Attention] The setting change of the offset level  $\beta$  should be made to &h40 [7] =0 and &h40 [6] =0 and be done.

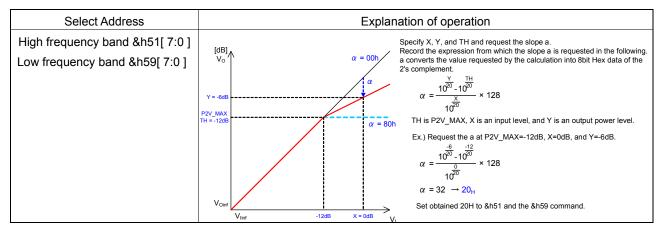

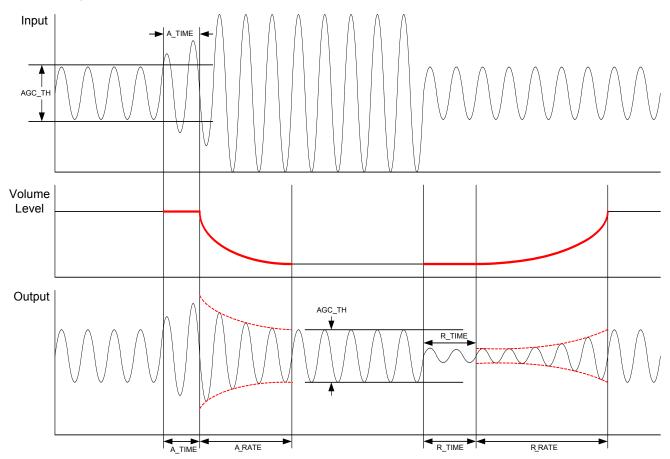

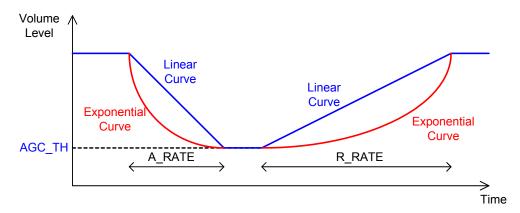

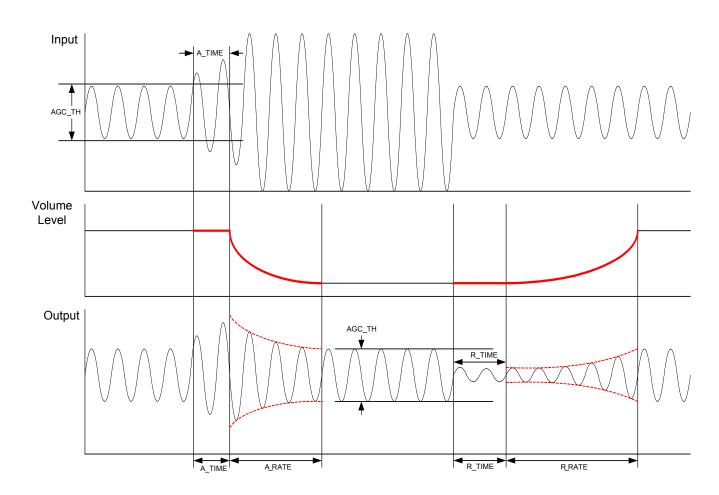

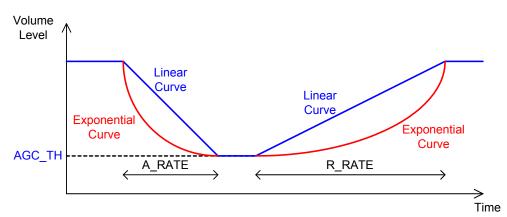

# The setting of a transition time in attack (1)

A\_RATE is the transition time setting when the condition of the  $P^2$ Volume feature transfers from (2) to (3).

Default = 3

| Select Address                | Explanation of operation |         |             |         |             |  |  |

|-------------------------------|--------------------------|---------|-------------|---------|-------------|--|--|

| High frequency band &h52[6:4] | C                        | Command | A_RATE time | Command | A_RATE time |  |  |

| Low frequency band &h5A[6:4]  |                          | 0       | 1ms         | 4       | 5ms         |  |  |

| Low inequency band anon[0.4]  |                          | 1       | 2ms         | 5       | 10ms        |  |  |

|                               |                          | 2       | 3ms         | 6       | 20ms        |  |  |

|                               |                          | 3       | 4ms         | 7       | 40ms        |  |  |

The setting of a transition time in release (1)

R\_RATE is the transition time setting when the condition of the P<sup>2</sup>Volume feature transfers from (3) to (2).

Default = Bh

| Select Address                | Explanation of operation |             |         |             |  |  |  |  |

|-------------------------------|--------------------------|-------------|---------|-------------|--|--|--|--|

| High frequency band &h52[3:0] | Command                  | R_RATE time | Command | R_RATE time |  |  |  |  |

| Low frequency band &h5A[3:0]  | 0                        | 0.125s      | 8       | 2s          |  |  |  |  |

|                               | 1                        | 0.1825s     | 9       | 2.5s        |  |  |  |  |

|                               | 2                        | 0.25s       | А       | 3s          |  |  |  |  |

|                               | 3                        | 0.5s        | В       | 4s          |  |  |  |  |

|                               | 4                        | 0.75s       | С       | 5s          |  |  |  |  |

|                               | 5                        | 1s          | D       | 6s          |  |  |  |  |

|                               | 6                        | 1.25s       | Е       | 7s          |  |  |  |  |

|                               | 7                        | 1.5s        | F       | 8s          |  |  |  |  |

Attack detection time setup (1)

A\_TIME is the transfer operation beginning setting of P2Volume feature. When the output power level when changing A\_TIME time continues from (2) to (3), the state transition of P2Volume is begun.

Default = 1

| Select Address                | Explanation of operation |        |             |         |             |  |  |

|-------------------------------|--------------------------|--------|-------------|---------|-------------|--|--|

| High frequency band &h53[7:4] | Cor                      | ommand | A_TIME time | Command | A_TIME time |  |  |

| Low frequency band &h5B[7:4]  |                          | 0      | 0ms         | 8       | 6ms         |  |  |

|                               |                          | 1      | 0.5ms       | 9       | 7ms         |  |  |

|                               |                          | 2      | 1ms         | А       | 8ms         |  |  |

|                               |                          | 3      | 1.5ms       | В       | 9ms         |  |  |

|                               |                          | 4      | 2ms         | С       | 10ms        |  |  |

|                               |                          | 5      | 3ms         | D       | 20ms        |  |  |

|                               |                          | 6      | 4ms         | E       | 30ms        |  |  |

|                               |                          | 7      | 5ms         | F       | 40ms        |  |  |

|                               |                          |        |             |         |             |  |  |

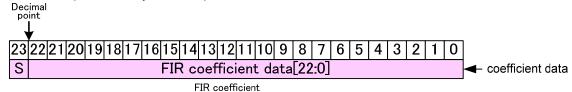

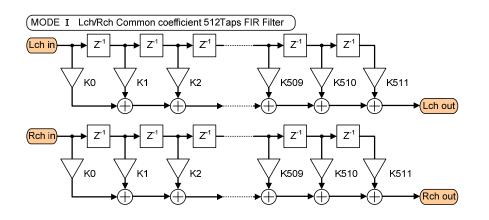

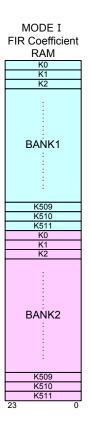

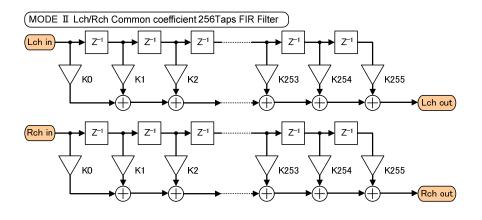

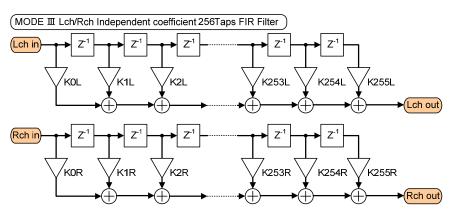

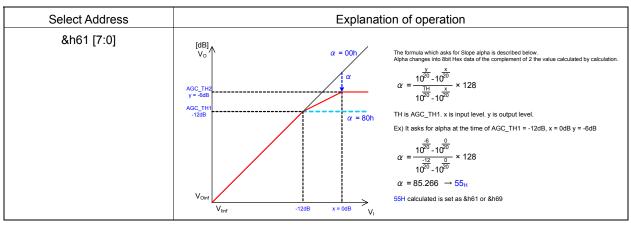

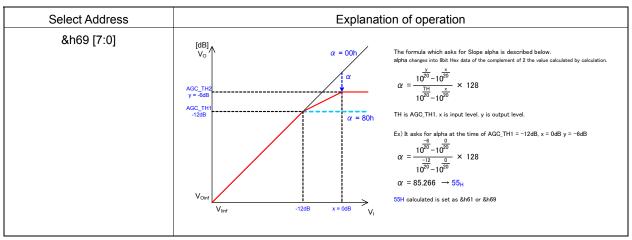

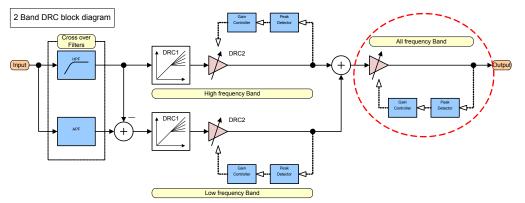

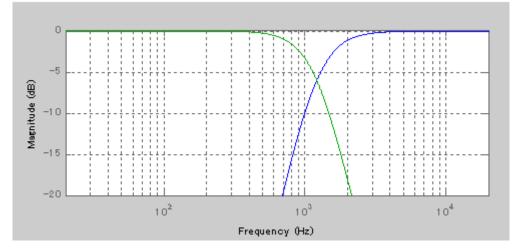

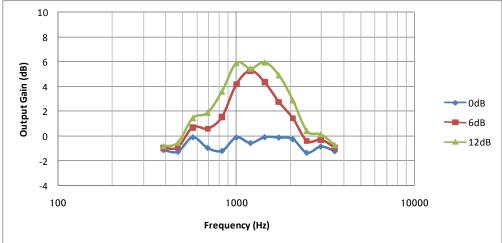

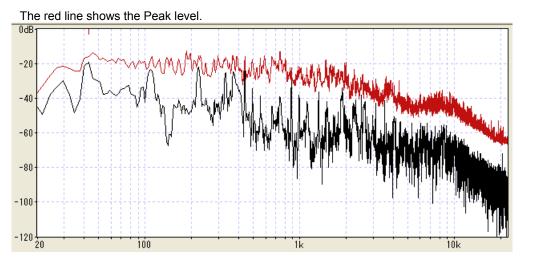

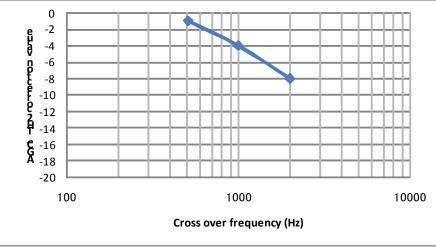

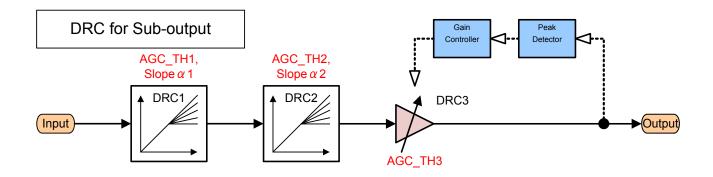

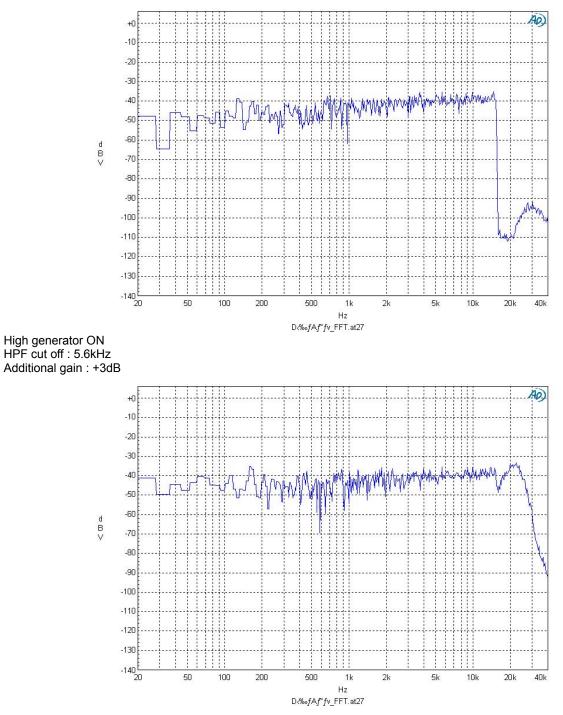

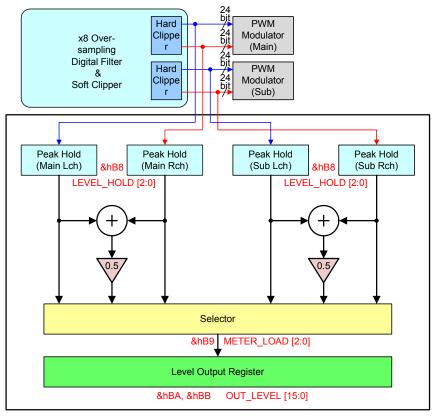

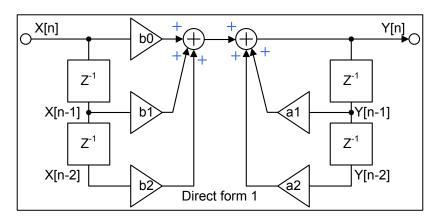

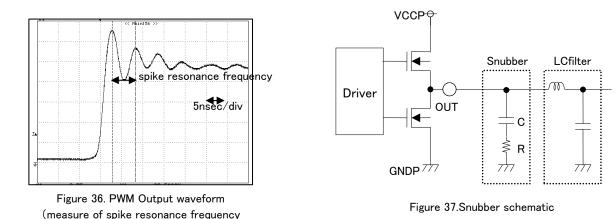

Release detection time setup (1)