# 8-Channel, 10-Bit, 40MSPS, 1.8V CMOS ANALOG-TO-DIGITAL CONVERTER

### FEATURES

- 8 DIFFERENTIAL ANALOG INPUTS

- 1V<sub>PP</sub> DIFFERENTIAL INPUT RANGE

- INT/EXT VOLTAGE REFERENCE

- ANALOG/DIGITAL SUPPLY: 1.8V

- DIGITAL I/O SUPPLY: 1.8V/3.3V

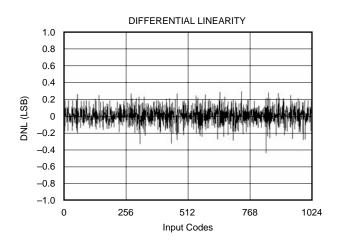

- DIFFERENTIAL NONLINEARITY: ±0.4LSB

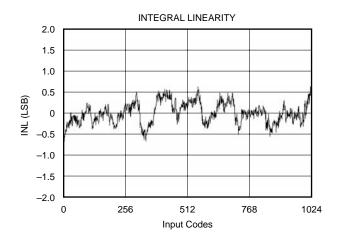

- INTEGRAL NONLINEARITY: ±0.6LSB

- SIGNAL-TO-NOISE: 60dB at f<sub>IN</sub> = 20MHz

- POWER DISSIPATION: 500mW

- INDIVIDUAL CHANNEL POWER-DOWN

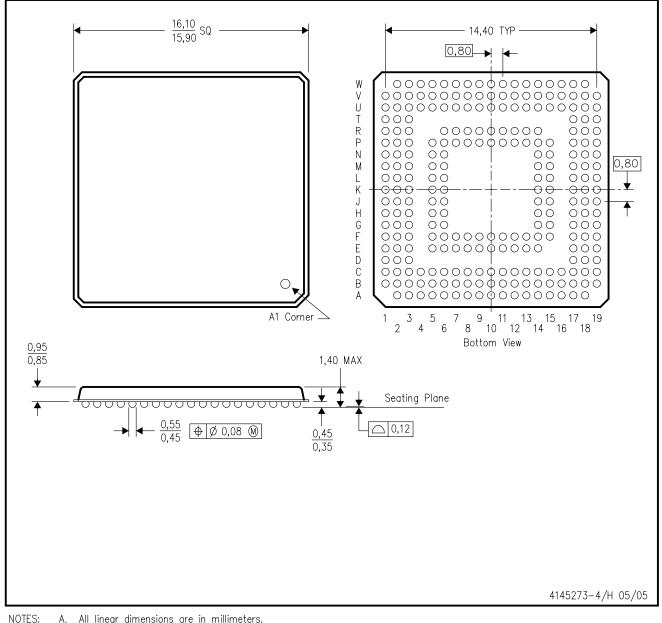

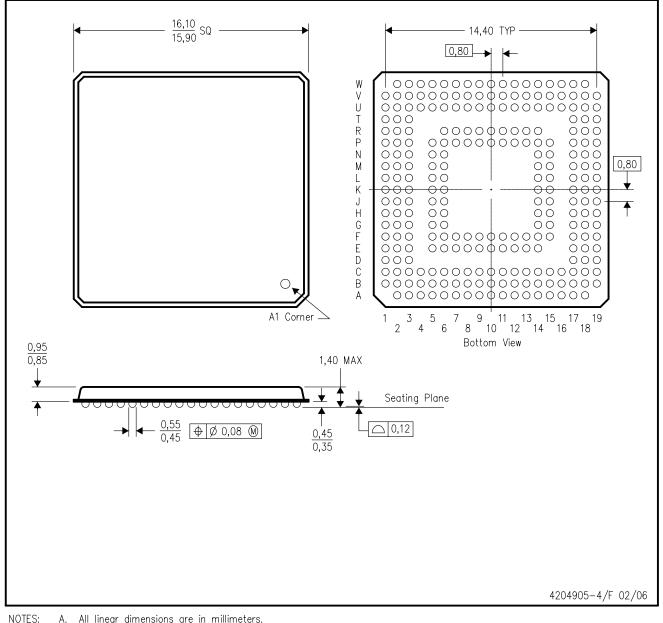

- 257-LEAD, 0.8 BALL PITCH, PLASTIC MicroSTAR BGA™ (16mm • 16mm)

### APPLICATIONS

- PORTABLE ULTRASOUND

- PORTABLE INSTRUMENTATION

### DESCRIPTION

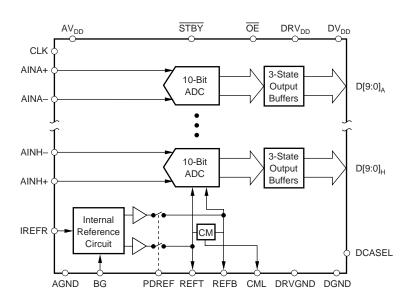

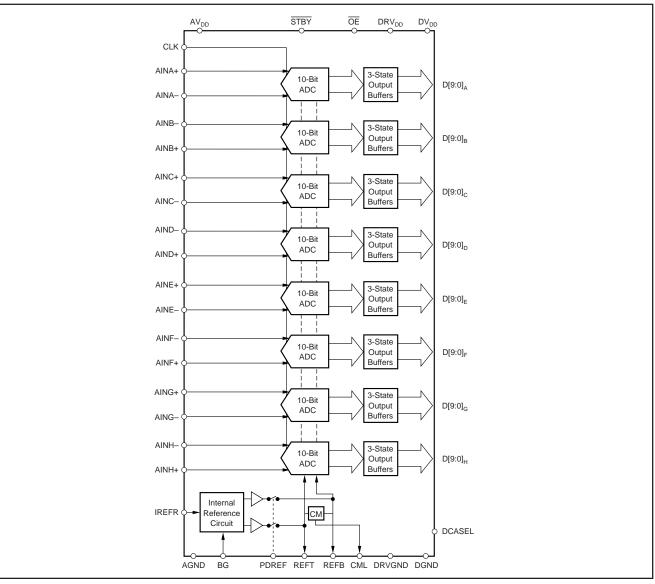

The ADS5121 is a low-power, 8-channel, 10-bit, 40MSPS CMOS Analog-to-Digital Converter (ADC) that operates from a single 1.8V supply, while offering 1.8V and 3.3V digital I/O flexibility. A single-ended input clock is used for simultaneous sampling of up to eight analog differential input channels. The flexible duty cycle adjust circuit (DCASEL) allows the use of a non-50% clock duty cycle. Individual standby pins allow users the ability to power-down any number of ADCs.

The internal reference can be bypassed to use an external reference to suit the accuracy and temperature drift requirements of the application. A 10-bit parallel bus on eight channels is provided with 3-state outputs.

The speed, resolution, and low power of the ADS5121 make it ideal for applications requiring high-density signal processing in low-power environments.

The ADS5121 is characterized for operation from  $-40^\circ\text{C}$  to  $+85^\circ\text{C}.$

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MicroSTAR BGA is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

Copyright © 2003-2006, Texas Instruments Incorporated

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Supply Voltage: AV <sub>DD</sub> to AGND, DV <sub>DD</sub> to DGND0.3V to +2.2V |

|---------------------------------------------------------------------------------|

| DRV <sub>DD</sub> to DRGND0.3V to +4.0V                                         |

| AGND to DGND0.3V to +0.3V                                                       |

| AV <sub>DD</sub> to DV <sub>DD</sub> 2.2V to +2.2V                              |

| Reference Voltage Input Range REFT, REFB to AGND0.3V to AV <sub>DD</sub> + 0.3V |

| Analog Input Voltage Range AIN to AGND0.3V to AV <sub>DD</sub> + 0.3V           |

| Clock Input CLK to DGND0.3V to DRV <sub>DD</sub> + 0.3V                         |

| Digital Input to DGND0.3V to DV <sub>DD</sub> + 0.3V                            |

| Digital Outputs to DRGND0.3V to DRV <sub>DD</sub> + 0.3V                        |

| Operating Temperature Range (T <sub>J</sub> )0°C to +105°C                      |

| Storage Temperature Range (T <sub>STG</sub> )65°C + 150°C                       |

|                                                                                 |

NOTE: (1) Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### PACKAGE/ORDERING INFORMATION(1)

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT | PACKAGE-LEAD             | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|--------------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| ADS5121 | MicroSTAR BGA-257        | GHK                   | -40°C to +85°C                    | ADS5121IGHK        | ADS5121IGHK        | Tray, 90                     |

| ADS5121 | ROHS-Compliant MicroSTAR | ZHK                   | –40°C to +85°C                    | ADS5121IZHK        | ADS5121IZHK        | Tray, 90                     |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

### **BLOCK DIAGRAM**

# **DC CHARACTERISTICS**

$AV_{DD} = DV_{DD} = 1.8V, DRV_{DD} = 3.3V, Clock = 40MSPS, 50\% Clock Duty Cycle, -0.5dBFS Input Span, Internal Reference, I_{REFR} = 6.8k\Omega, T_{MIN} = -40^{\circ}C, T_{MAX} = +85^{\circ}C, and typical values at T_A = 25^{\circ}C, unless otherwise noted.$

|                                                                                                                                                                                                                               |                                                                                                                                     |                      | ADS5121                                             |                                 |                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------|---------------------------------|----------------------------------------------|

| PARAMETER                                                                                                                                                                                                                     | CONDITION                                                                                                                           | MIN                  | ТҮР                                                 | MAX                             | UNITS                                        |

| RESOLUTION                                                                                                                                                                                                                    |                                                                                                                                     |                      | 10                                                  |                                 | Bits                                         |

| DC ACCURACY<br>Differential Nonlinearity, DNL<br>Integral Nonlinearity, INL<br>No Missing Codes<br>Gain Error<br>Offset Error<br>Gain Temperature Coefficient<br>Gain Matching                                                | External Reference<br>External Reference                                                                                            | -0.9<br>-1.5<br>-0.6 | ±0.4<br>±0.6<br>Tested<br>0.1<br>0.2<br>6.0<br>±0.4 | +1.0<br>+1.5<br>+0.6<br>+1.8    | LSB<br>LSB<br>%FSR<br>%FSR<br>ppm/°C<br>%FSR |

| ANALOG INPUT<br>Input Voltage Range (AIN+, AIN–)<br>Input Voltage, Differential Full-Scale<br>Input Common-Mode Range<br>Input Resistance, R <sub>IN</sub><br>Input Capacitance, C <sub>IN</sub>                              | f <sub>CLK</sub> = 40MSPS                                                                                                           | REFB<br>(F           | 1<br>REFT + REFB)<br>  31<br>5                      | REFT                            | V<br>V <sub>PP</sub><br>V<br>kΩ<br>pF        |

| INTERNAL REFERENCE VOLTAGES<br>Reference, Top (REFT)<br>Reference, Bottom (REFB)<br>Int Reference Temperature Coefficient                                                                                                     |                                                                                                                                     | 1.30<br>0.76         | 1.34<br>0.82<br>10                                  | 1.42<br>0.87                    | V<br>V<br>ppm/°C                             |

| EXTERNAL REFERENCE GENERATION<br>Reference, Top (REFT)<br>Reference, Bottom (REFB)<br>Input Resistance, REFR <sub>IN</sub><br>(between REFB and REFT)                                                                         |                                                                                                                                     | 1.15<br>0.65         | 1.25<br>0.75<br>80                                  | 1.35<br>0.85                    | V<br>V<br>Ω                                  |

| POWER SUPPLY<br>Operating Supply Current, I <sub>DD</sub><br>Analog Operating Supply Current, IAV <sub>DD</sub><br>Digital Operating Supply Current, IDV <sub>DD</sub><br>Driver Operating Supply Current, IDRV <sub>DD</sub> | f <sub>IN</sub> = 3.5MHz<br>C <sub>L</sub> = 20pF, 3.3V<br>C <sub>L</sub> = 20pF, 1.8V                                              |                      | 242<br>155<br>43<br>42<br>22                        | 255<br>170<br>48<br>48<br>30    | mA<br>mA<br>mA<br>mA<br>mA                   |

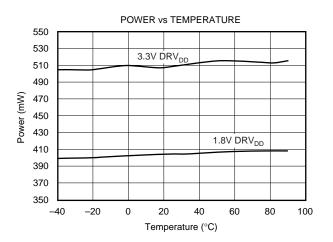

| Operating Voltage<br>AV <sub>DD</sub><br>DV <sub>DD</sub><br>DRV <sub>DD</sub><br>Power Dissipation                                                                                                                           | $DRV_{DD} = 3.3V$<br>$DRV_{DD} = 1.8V$                                                                                              | 1.65<br>1.65<br>1.65 | 1.8<br>1.8<br>1.8<br>500<br>404                     | 2.0<br>2.0<br>3.6<br>525<br>420 | V<br>V<br>W<br>mW                            |

| Power Standby Power-Supply Rejection Ratio, PSRR                                                                                                                                                                              | CLK Running<br>CLK Stopped<br>PDREF = 1, External REF, CLK Running<br>PDREF = 1, External REF, CLK Stopped<br>±5%, AV <sub>DD</sub> |                      | 404<br>62<br>52<br>12<br>1.6<br>2                   | 420<br>70<br>60<br>15<br>5      | mW<br>mW<br>mW<br>mW                         |

# **DC CHARACTERISTICS**

AV<sub>DD</sub> = DV<sub>DD</sub> = 1.8V, DRV<sub>DD</sub> = 3.3V, Clock = 40MSPS, 50% Clock Duty Cycle, -0.5dBFS Input Span, Internal Reference, and T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.

| PARAMETER                                                                                                                                                                                                                             | CONDITION                                                                                                 | MIN                      | TYP | MAX                                  | UNITS              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------------------|--------------------|

| DIGITAL INPUTS (STBY A-H, PDREF, OE, CLK)<br>High-Level Input Voltage, V <sub>II</sub><br>Low-Level Input Voltage, V <sub>IL</sub><br>High-Level Input Current, I <sub>IH</sub><br>Low-Level Input Current, I <sub>IL</sub>           | $\label{eq:DRV_DD} \begin{split} DRV_{DD} &= 3.3V/1.8V \\ V_{IH} &= DRV_{DD} \\ V_{IL} &= 0V \end{split}$ | 0.70 • DRV <sub>DD</sub> |     | 0.25 • DRV <sub>DD</sub><br>±1<br>±1 | V<br>V<br>μΑ<br>μΑ |

| DIGITAL INPUTS (DCASEL)<br>High-Level Input Voltage, V <sub>IH</sub><br>Low-Level Input Voltage, V <sub>IL</sub><br>High-Level Input Current, I <sub>IH</sub><br>Low-Level Input Current, I <sub>IL</sub>                             | $V_{IH} = DV_{DD}$<br>$V_{IL} = 0V$                                                                       | 0.70 • DV <sub>DD</sub>  |     | 0.25 • DV <sub>DD</sub><br>±1<br>±1  | V<br>V<br>μΑ<br>μΑ |

| DIGITAL OUTPUTS ( DRV <sub>DD</sub> = 3.3/1.8V)<br>High-Level Output Voltage, V <sub>OH</sub><br>Low-Level Output Voltage, V <sub>OL</sub><br>External Load Capacitance, C <sub>L</sub><br>3-State Leakage Current, I <sub>LEAK</sub> | $I_{OH} = -50\mu A$<br>$I_{OL} = 50\mu A$<br>$\overline{OE} = HIGH$                                       | 0.8 • DRV <sub>DD</sub>  | 15  | 0.2 • DRV <sub>DD</sub><br>±1        | V<br>V<br>pF<br>μA |

# AC CHARACTERISTICS

$AV_{DD} = DV_{DD} = 1.8V$ ,  $DRV_{DD} = 3.3V$ , 50% Clock Duty Cycle, CLK = 40MSPS, Analog Input at -0.5dBFS Input Span, Internal Voltage Reference, I<sub>REFR</sub> = 6.8k $\Omega$ , T<sub>MIN</sub> = -40°C, T<sub>MAX</sub> = +85°C, and typical values at T<sub>A</sub> = 25°C, unless otherwise noted.

|                                           |         |                                             |     | ADS5121 |     |         |

|-------------------------------------------|---------|---------------------------------------------|-----|---------|-----|---------|

| PARAMETER                                 |         | CONDITION                                   | MIN | TYP     | MAX | UNITS   |

| Signal-to-Noise Ratio                     | (SNR)   | f <sub>IN</sub> = 3.5MHz                    | 56  | 60      |     | dB      |

|                                           |         | f <sub>IN</sub> = 10MHz                     | 56  | 60      |     | dB      |

|                                           |         | $f_{IN} = 20MHz$                            |     | 60      |     | dB      |

| Signal-to-Noise and Distortion            | (SINAD) | f <sub>IN</sub> = 3.5MHz                    | 56  | 59      |     | dB      |

|                                           |         | f <sub>IN</sub> = 10MHz                     | 56  | 59      |     | dB      |

|                                           |         | $f_{IN} = 20MHz$                            |     | 59      |     | dB      |

| Effective Number of Bits                  | (ENOB)  | f <sub>IN</sub> = 3.5MHz                    | 9.0 | 9.5     |     | Bits    |

|                                           |         | f <sub>IN</sub> = 10MHz                     | 9.0 | 9.5     |     | Bits    |

|                                           |         | $f_{IN} = 20MHz$                            |     | 9.5     |     | Bits    |

| Spurious-Free Dynamic Range               | (SFDR)  | f <sub>IN</sub> = 3.5MHz                    | 66  | 75      |     | dBc     |

|                                           |         | f <sub>IN</sub> = 10MHz                     | 65  | 74      |     | dBc     |

|                                           |         | $f_{IN} = 20MHz$                            |     | 73      |     | dBc     |

| 2nd-Harmonic Distortion                   | (HD2)   | f <sub>IN</sub> = 3.5MHz                    | 69  | 85      |     | dBc     |

|                                           |         | f <sub>IN</sub> = 10MHz                     | 68  | 85      |     | dBc     |

|                                           |         | $f_{IN} = 20MHz$                            |     | 84      |     | dBc     |

| 3rd-Harmonic Distortion                   | (HD3)   | f <sub>IN</sub> = 3.5MHz                    | 66  | 77      |     | dBc     |

|                                           |         | f <sub>IN</sub> = 10MHz                     | 65  | 75      |     | dBc     |

|                                           |         | $f_{IN} = 20MHz$                            |     | 73      |     | dBc     |

| 2-Tone Intermodulation Distortion         | (IMD)   | $f_1 = 4.43MHz$ , $f_2 = 4.53MHz$ at -6.5dB |     | -69     |     | dBFS    |

| Channel-to-Channel Crosstalk              |         | $f_{IN} = 10MHz, DRV_{DD} = 3.3V$           |     | 89      |     | dB      |

| Effective Resolution Bandwidth            |         |                                             |     | 22      |     | MHz     |

| Over-Voltage Recovery Time <sup>(1)</sup> |         |                                             |     | 20      |     | ns      |

| Differential Gain <sup>(1)</sup>          |         |                                             |     | ±1      |     | %       |

| Differential Phase <sup>(1)</sup>         |         |                                             |     | ±0.25   |     | Degrees |

NOTE: (1) Assured by design.

## SWITCHING CHARACTERISTICS

$AV_{DD} = DV_{DD} = 1.8V$ ,  $DRV_{DD} = 3.3V$ , 50% Clock Duty Cycle, CLK = 40MSPS, Analog Input at -0.5dBFS Input Span, Internal Voltage Reference,  $T_{MIN} = -40^{\circ}C$ , and  $T_{MAX} = +85^{\circ}C$ . Typical values at  $T_A = 25^{\circ}C$ , unless othewise noted.

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                   | CONDITION      | MIN | TYP                                      | MAX | UNITS                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|------------------------------------------|-----|------------------------------------------------------------|

| $\begin{array}{c c} \mbox{Maximum Conversion Rate} \\ \mbox{Clock Duty Cycle} \\ \mbox{Data Latency}^{(1)} \\ \mbox{Clock $\downarrow$ to Data Valid} & t_{\mbox{DO}}^{(1)} \\ \hline \hline OE $\downarrow$ to Outputs Enabled} & t_{\mbox{EN}}^{(1)} \\ \hline OE $\uparrow$ Rising to Outputs Tri-Stated} & t_{\mbox{DIS}} \\ \mbox{Aperture Delay} \\ \mbox{Aperture Uncertainty (Jitter)} \end{array}$ | DCASEL Enabled | 5   | 30 to 70<br>6.5<br>8<br>8<br>8<br>1<br>2 | 40  | MSPS<br>%<br>Clk Cycles<br>ns<br>ns<br>ns<br>ns<br>ps, rms |

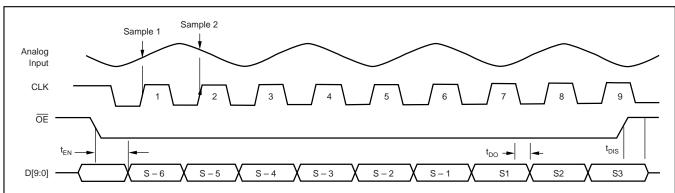

NOTE: (1) See timing diagram.

### TIMING DIAGRAM (Per ADC Channel)

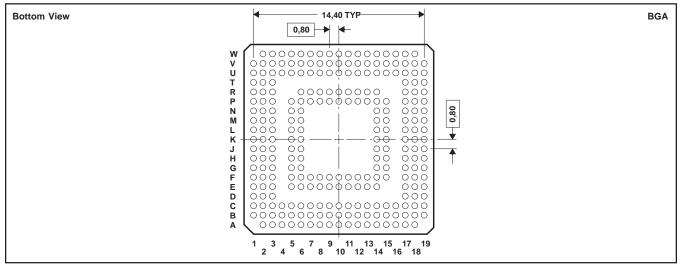

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| NAME             | PINS                                                                                                     | I/O   | TERMINAL DESCRIPTION                                        |

|------------------|----------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------|

| AV <sub>DD</sub> | C6, C7, E6, F1, F2, F3, F5, F6, J6, N3, P3, P5, P6, P7, R6, V6, W6                                       | Ι     | Analog Supply (1.8V)                                        |

| AGND             | A3, A5, B5, B9, C1, C5, C9, E3, E7, F7, G1, G5, G6, H6, J1, J2, M2, N5, N6, P8,                          | Т     | Analog Ground                                               |

|                  | R1, R2, R3, R7, U1, U5, U10, V5, V10, W3, W7                                                             |       |                                                             |

| AINA+            | U7                                                                                                       | 1     | Analog Input Channel A                                      |

| AINA-            | V7                                                                                                       | 1     | Complementary Analog Input Channel A                        |

| AINB+            | W4                                                                                                       |       | Analog Input Channel B                                      |

| AINB-            | V4                                                                                                       | 1     | Complementary Analog Input Channel B                        |

| AINC+            | T1                                                                                                       |       | Analog Input Channel C                                      |

| AINC-            | Τ2                                                                                                       |       | Complementary Analog Input Channel C                        |

| AIND+            | P2                                                                                                       |       | Analog Input Channel D                                      |

| AIND-            | P1                                                                                                       | 1     | Complementary Analog Input Channel D                        |

| AINE+            | G3                                                                                                       | 1     | Analog Input Channel E                                      |

| AINE-            | G2                                                                                                       | 1     | Complementary Analog Input Channel E                        |

| AINF+            | D1                                                                                                       | 1     | Analog Input Channel F                                      |

| AINF-            | D2                                                                                                       | 1     | Complementary Analog Input Channel F                        |

| AING+            | A4                                                                                                       | 1     | Analog Input Channel G                                      |

| AING-            | B4                                                                                                       | 1     | Complementary Analog Input Channel G                        |

| AINH+            | B6                                                                                                       |       | Analog Input Channel H                                      |

| AINH-            | A6                                                                                                       | 1     | Complementary Analog Input Channel H                        |

| CLK              | W9                                                                                                       | 1     | Clock Input                                                 |

| REFT             | K3, L1, J3                                                                                               | I/O   | Reference Top                                               |

| REFB             | K5, J5, L5                                                                                               | I/O   | Reference Bottom                                            |

| CML              | L2, L3                                                                                                   | 0     | Common-Mode Level Output                                    |

| BG               | K1                                                                                                       | I/O   | Bandgap Decoupling (Decouple with 0.1µF cap to AGND)        |

| IREFR            | K6                                                                                                       | 1     | Internal Reference Bias Current (Connect 6.8kΩ resistor     |

|                  |                                                                                                          |       | from this pin AGND to set internal bias amplifier current.) |

| DNC              | L6                                                                                                       | 1     | Do Not Connect                                              |

| DNC              | M1                                                                                                       | 1     | Do Not Connect                                              |

| NC               | E1, E2, E5, K2, U6, W5                                                                                   | 1     | No Internal Connection                                      |

| DCASEL           | N2                                                                                                       | 1     | Duty Cycle Adjust                                           |

| $DV_DD$          | C2, C3, C4, D3, E8, F8, H3, H5, M3, M5, R8, T3, U3, U4, U8, V3, P13, R13<br>P17, L15, J14, F17, F12, E12 | I     | Digital Supply (1.8V)                                       |

| DGND             | A2, A7, B1, B2, B3, B7, B13, C13, G15, H1, H2, H17, L17, M6, N1, N15, U2, U13,                           |       | Digital Ground                                              |

| 20112            | U14, V1, V2, V8, W2, W8                                                                                  |       |                                                             |

| PDREF            | V9                                                                                                       |       | Power-Down Ref: 0 = internal reference, 1 = external        |

|                  |                                                                                                          |       | reference. In external reference mode connect REFT to       |

|                  |                                                                                                          |       | BG pin.                                                     |

| STBY A           | W10                                                                                                      |       | Power-Down Channel A                                        |

| STBY B           | P9                                                                                                       |       | Power-Down Channel B                                        |

| STBY C           | R9                                                                                                       |       | Power-Down Channel C                                        |

| STBY D           | U9                                                                                                       |       | Power-Down Channel D                                        |

| STBY E           | C8                                                                                                       | li    | Power-Down Channel E                                        |

| STBY F           | B8                                                                                                       | l i   | Power-Down Channel F                                        |

| STBY G           | A8                                                                                                       |       | Power-Down Channel G                                        |

| STBY H           | A9                                                                                                       | l i   | Power-Down Channel H                                        |

| OE               | P10                                                                                                      | l i l | Enable all Digital Outputs, Ch. A-H. OE: 0 = Outputs        |

|                  |                                                                                                          | '     | Enable. OE: 1 = Outputs disabled (3-state).                 |

|                  | B17, C16, D17, E9, E10, E11, E17, F9, H14, H15, K17, L14, N14, P12, P14, P15                             | 1     | Driver Digital Supply (1.8V or 3.3V)                        |

| DDOND            | R10, R12, R14                                                                                            |       | Driver Disitel Occurred                                     |

| DRGND            | E13, F10, F11, F13, F14, F15, G14, G17, M14, M15, M17, N17, U11, U12, U15, U16                           |       | Driver Digital Ground                                       |

### DATA OUTPUT PINS

| NAME       | PINS       | I/O | TERMINAL DESCRIPTION                 | NAME       | PINS       | 1/0 | TERMINAL DESCRIPTION    |

|------------|------------|-----|--------------------------------------|------------|------------|-----|-------------------------|

|            |            |     |                                      | DOE        | F118       | 0   | Bit 1, Channel E (LSB)  |

| D0A        | V14        | 0   | Bit 1, Channel A (LSB)               | D1E        | F19        | 0   | Bit 2, Channel E        |

| D1A        | W14        | 0   | Bit 2, Channel A                     | D1E<br>D2E | G18        | 0   | Bit 3, Channel E        |

| D2A        | V13        | 0   | Bit 3, Channel A                     | D2E<br>D3E | G10<br>G19 | 0   | Bit 4, Channel E        |

| D3A        | W13        | 0   | Bit 4, Channel A                     | D3E<br>D4E | H18        | 0   | ,                       |

| D4A        | V12        | 0   | Bit 5, Channel A                     |            | -          | -   | Bit 5, Channel E        |

| D5A        | W12        | 0   | Bit 6, Channel A                     | D5E        | H19        | 0   | Bit 6, Channel E        |

| D6A        | R11        | 0   | Bit 7, Channel A                     | D6E        | J15        | 0   | Bit 7, Channel E        |

| D7A        | P11        | 0   | Bit 8, Channel A                     | D7E        | J17        | 0   | Bit 8, Channel E        |

| D8A        | V11        | 0   | Bit 9, Channel A                     | D8E        | J18        | 0   | Bit 9, Channel E        |

| D9A        | W11        | 0   | Bit 10, Channel A (MSB)              | D9E        | J19        | 0   | Bit 10, Channel E (MSB) |

| D0B        | V19        | 0   | Bit 1, Channel B (LSB)               | D0F        | A18        | 0   | Bit 1, Channel F (LSB)  |

| D1B        | V18        | 0   | Bit 2, Channel B                     | D1F        | B18        | 0   | Bit 2, Channel F        |

| D2B        | U17        | 0   | Bit 3, Channel B                     | D2F        | C17        | 0   | Bit 3, Channel F        |

| D3B        | W18        | 0   | Bit 4, Channel B                     | D3F        | B19        | 0   | Bit 4, Channel F        |

| D4B        | V17        | 0   | Bit 5, Channel B                     | D4F        | C18        | 0   | Bit 5, Channel F        |

| D5B        | W17        | 0   | Bit 6, Channel B                     | D5F        | C19        | 0   | Bit 6, Channel F        |

| D6B        | V16        | 0   | Bit 7, Channel B                     | D6F        | D18        | 0   | Bit 7, Channel F        |

| D7B        | W16        | 0   | Bit 8, Channel B                     | D7F        | D19        | 0   | Bit 8, Channel F        |

| D8B        | V15        | 0   | Bit 9, Channel B                     | D8F        | E18        | 0   | Bit 9, Channel F        |

| D9B        | W15        | 0   | Bit 10, Channel B (MSB)              | D9F        | E19        | 0   | Bit 10, Channel F (MSB) |

| DOC        | P19        | 0   | Bit 1, Channel C (LSB)               | D0G        | A14        | 0   | Bit 1, Channel G (LSB)  |

| D1C        | P18        | 0   | Bit 2, Channel C                     | D1G        | B14        | 0   | Bit 2, Channel G        |

| D2C        | R19        | 0   | Bit 3, Channel C                     | D2G        | C14        | 0   | Bit 3, Channel G        |

| D3C        | R18        | 0   | Bit 4, Channel C                     | D3G        | A15        | 0   | Bit 4, Channel G        |

| D4C        | R17        | 0   | Bit 5, Channel C                     | D4G        | B15        | 0   | Bit 5, Channel G        |

| D5C        | T19        | 0   | Bit 6, Channel C                     | D5G        | E14        | 0   | Bit 6, Channel G        |

| D6C        | T18        | 0   | Bit 7. Channel C                     | D6G        | C15        | 0   | Bit 7, Channel G        |

| D7C        | U19        | õ   | Bit 8, Channel C                     | D7G        | A16        | 0   | Bit 8, Channel G        |

| D8C        | U18        | õ   | Bit 9, Channel C                     | D8G        | B16        | 0   | Bit 9, Channel G        |

| D9C        | T17        | õ   | Bit 10, Channel C (MSB)              | D9G        | A17        | 0   | Bit 10, Channel G (MSB) |

| DOD        | K14        | õ   | Bit 1, Channel D (LSB)               | D0H        | C10        | 0   | Bit 1, Channel H (LSB)  |

| D1D        | K15        | 0   | Bit 2, Channel D                     | D1H        | B10        | 0   | Bit 2, Channel H        |

| D1D<br>D2D | K13<br>K18 | 0   | Bit 3, Channel D                     | D2H        | A10        | ō   | Bit 3, Channel H        |

| D2D<br>D3D | K10<br>K19 | 0   | Bit 4, Channel D                     | D3H        | C11        | ŏ   | Bit 4, Channel H        |

| D3D<br>D4D | L18        | 0   | Bit 5, Channel D                     | D4H        | B11        | 0   | Bit 5. Channel H        |

| D4D<br>D5D | L18<br>L19 | 0   | Bit 6, Channel D                     | D5H        | A11        | 0   | Bit 6, Channel H        |

| D5D<br>D6D | L19<br>M19 | 0   | Bit 6, Channel D<br>Bit 7, Channel D | D6H        | A12        | 0   | Bit 7, Channel H        |

|            |            | -   |                                      | D7H        | B12        | 0   | Bit 8, Channel H        |

| D7D        | M18        | 0   | Bit 8, Channel D                     | D8H        | C12        | 0   | Bit 9. Channel H        |

| D8D        | N19        | 0   | Bit 9, Channel D                     | D8H<br>D9H | A13        | 0   | Bit 10, Channel H (MSB) |

| D9D        | N18        | 0   | Bit 10, Channel D (MSB)              | Dau        | AIS        |     |                         |

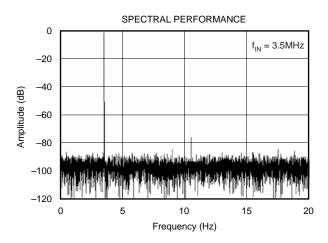

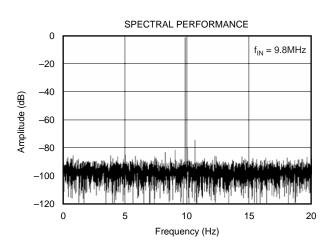

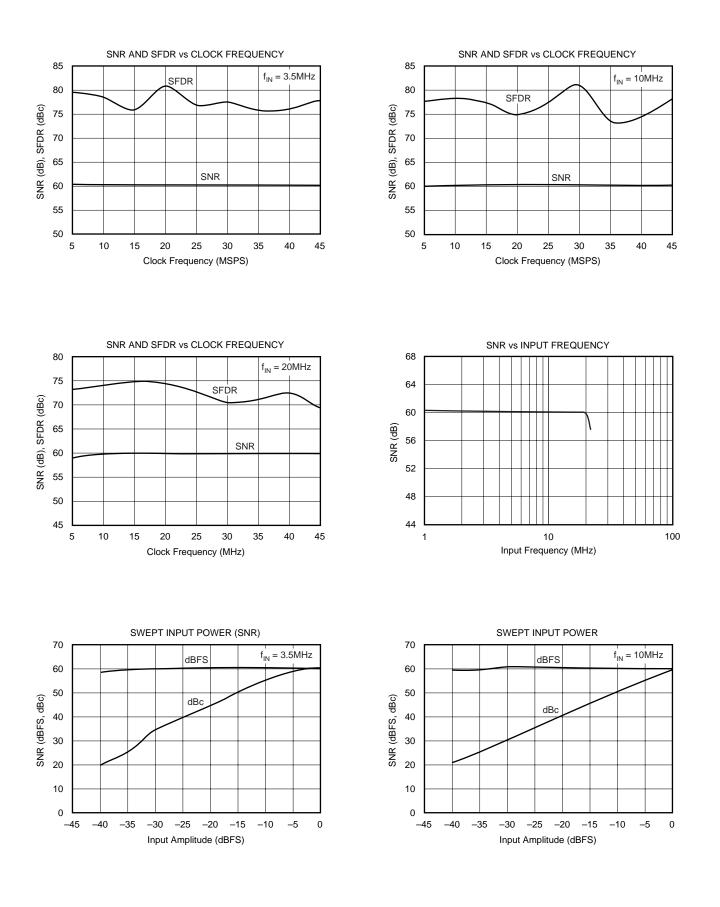

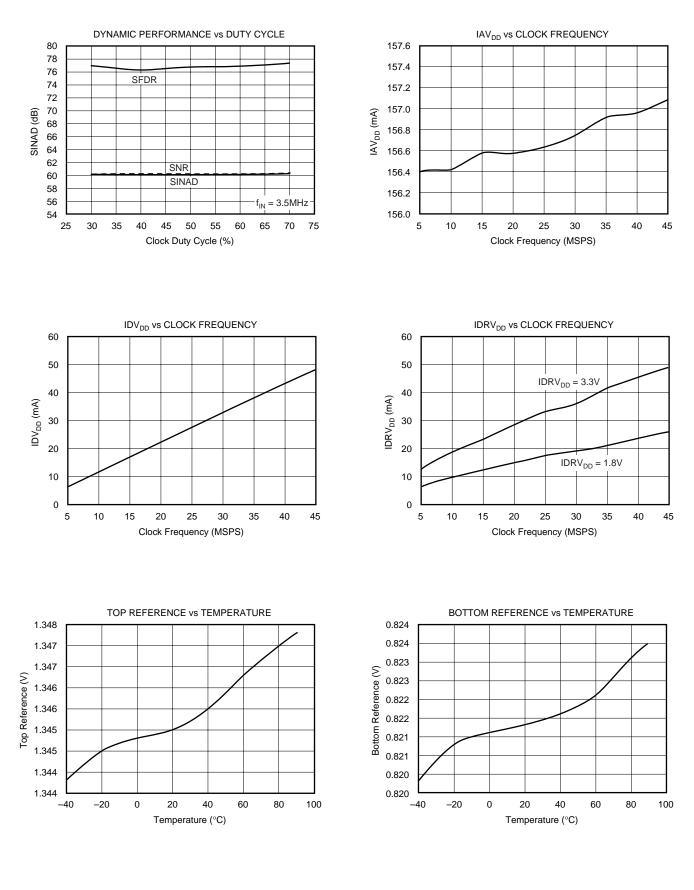

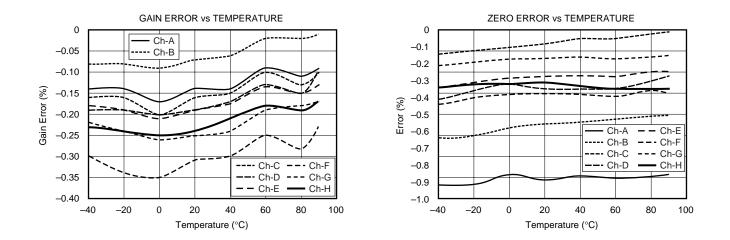

## **TYPICAL CHARACTERISTICS**

T<sub>A</sub> = 25°C, AV<sub>DD</sub> = DV<sub>DD</sub> = 1.8V, DRV<sub>DD</sub> = 3.3V, f<sub>IN</sub> = -0.5dBFS, Internal Reference, Clock = 40MSPS, and Differential Input Range = 1V<sub>PP</sub>, unless otherwise noted.

2ND- AND 3RD-HARMONIC vs INPUT FREQUENCY -60 -65 -70 3rd-Harmonic -75 Amplitude (dBc) -80 -85 -90 2nd-Harmonic -95 -100 -105 -110 1 10 100 Input Frequency (MHz)

## **TYPICAL CHARACTERISTICS (Cont.)**

T<sub>A</sub> = 25°C, AV<sub>DD</sub> = DV<sub>DD</sub> = 1.8V, DRV<sub>DD</sub> = 3.3V, f<sub>IN</sub> = -0.5dBFS, Internal Reference, Clock = 40MSPS, and Differential Input Range = 1V<sub>PP</sub>, unless otherwise noted.

## **TYPICAL CHARACTERISTICS (Cont.)**

T<sub>A</sub> = 25°C, AV<sub>DD</sub> = DV<sub>DD</sub> = 1.8V, DRV<sub>DD</sub> = 3.3V, f<sub>IN</sub> = -0.5dBFS, Internal Reference, Clock = 40MSPS, and Differential Input Range = 1V<sub>PP</sub>, unless otherwise noted.

ADS5121 SBAS281D TEXAS INSTRUMENTS www.ti.com

## **TYPICAL CHARACTERISTICS (Cont.)**

$T_{A} = 25^{\circ}C, \ AV_{DD} = DV_{DD} = 1.8V, \ DRV_{DD} = 3.3V, \ f_{IN} = -0.5dBFS, \ Internal \ Reference, \ Clock = 40MSPS, \ and \ Differential \ Input \ Range = 1V_{PP}, \ unless \ otherwise \ noted.$

### **APPLICATION INFORMATION**

### CONVERTER OPERATION

The ADS5121 is an 8-channel, simultaneous sampling ADC. Its low power and high sampling rate of 40MSPS is achieved using a state-of-the-art switched capacitor pipeline architecture built on an advanced low-voltage CMOS process. The ADS5121 operates primarily from a +1.8V single supply. For additional interfacing flexibility, the digital I/O supply (DRV<sub>DD</sub>) can be set to either +1.8V or +3.3V. The ADC core of each channel consists of 10 pipeline stages. Each of the 10 stages produces one digital bit per stage. Both the rising and the falling clock edges are utilized to propagate the sample through the pipeline every half clock, for a total of five clock cycles. Two additional clock cycles are needed to pass the sample data through the digital error correction logic and the output latches. The total pipeline delay, or data latency, is therefore 6.5 clock cycles long. Since a common clock controls the timing of all eight channels, the analog signal is sampled at the same time, as well as the data on the parallel ports that become updated simultaneously.

#### **INPUT IMPEDANCE**

Due to the switched capacitor input, the input impedance of the ADS5121 is effectively capacitive, and the driving source needs to provide sufficient slew current to charge and discharge the input sampling capacitor. The input impedance of the ADS5121 is also a function of the sampling rate. As the sampling frequency increases, the input impedance decreases at a linear rate of 1/fs. For most applications, this does not represent a limitation since the impedance remains relatively high, for example, approximately  $31k\Omega$  at the max sampling rate of 40MSPS. For applications using an op amp to drive the ADC, it is recommended that a series resistor, typically  $10\Omega$  to  $50\Omega$ , be added between the amplifier output and the converter inputs. This will isolate the converter capacitive input from the driver and avoid potential gain peaking, or instability.

#### **INPUT BIASING**

The ADS5121 operates from a single +1.8V analog supply, and requires each of the analog inputs (AIN+, AIN–) to be externally biased by a suitable common-mode voltage. For example, with a common-mode voltage of +1V, the  $1V_{PP}$  full-scale, differential input signal will swing symmetrically around +1V, or between 0.75V and 1.25V. This is determined by the two reference voltages, the top reference (REFT), and the bottom reference (REFB). Typically, the input common-mode level is related to the reference woltages and defined as (REFT + REFB)/2. This reference mid-point is provided at the common-mode level output (CML) pin and can directly be used for input biasing purposes. The voltage at CML will assume the mid-point for either internal or external reference

operation. In any case, it is recommended to bypass the CML pin with a ceramic  $0.1\mu F$  capacitor.

#### DRIVING THE ANALOG INPUTS

#### **Differential versus Single-Ended**

The analog input of the ADS5121 allows it to be driven either single-ended or differentially. Differential operation of the ADS5121 requires an input signal that consists of an inphase and a 180° out-of-phase part simultaneously applied to the inputs (AIN+, AIN–). The full-scale input range of the ADS5121 is defined by the reference voltages according to FSR = 2 x (REFT – REFB). For a typical  $1V_{PP}$  range, the differential input configuration only requires each input to see a signal swing of  $0.5V_{PP}$ . Operating the converter in single-ended configuration requires the full  $1V_{PP}$  swing applied to the chosen input. The differential operation offers a number of advantages, which in most applications will be instrumental in achieving the best dynamic performance of the ADS5121:

- Signal swing is half that required for the single-ended operation and is therefore less demanding to achieve while maintaining good linearity performance from the signal source.

- Reduced signal swing allows for more headroom of the interface circuitry and therefore a wider selection of the best suitable driver op amp.

- Even-order harmonics are minimized.

- Improved noise immunity based on the converter's common-mode input rejection.

For the single-ended mode, the signal is applied to one of the inputs while the other input is biased with a DC voltage to the required common-mode level. Both inputs are identical in terms of their impedance and performance. Applying the signal to the complementary input (AIN–) instead of the AIN+ input, however, will invert the orientation of the input signal relative to the output code. This could be helpful, for example, if the input driver operates in inverting mode using input AIN– as the signal input will restore the phase of the signal to its original orientation.

#### INPUT DRIVER CONFIGURATIONS

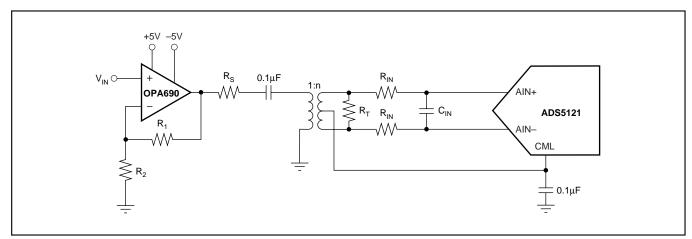

#### **Transformer-Coupled Interface**

If the application requires a signal conversion from a singleended source to drive the ADS5121 differentially, an RFtransformer might be a good solution. The selected transformer must have a center tap in order to apply the commonmode DC voltage necessary to bias the converter inputs. ACgrounding the center tap will generate the differential signal swing across the secondary winding. Consider a step-up transformer to take advantage of signal amplification without the introduction of another noise source. Furthermore, the reduced signal swing from the source may lead to an improved distortion performance.

The differential input configuration may provide a noticeable advantage of achieving good SFDR performance over a wide range of input frequencies. In this mode, both inputs (AIN+ and AIN–) of the ADS5121 see matched impedances. Figure 1 shows the schematic for the suggested transformercoupled interface circuit. The component values of the R-C low-pass may be optimized depending on the desired roll-off frequency.

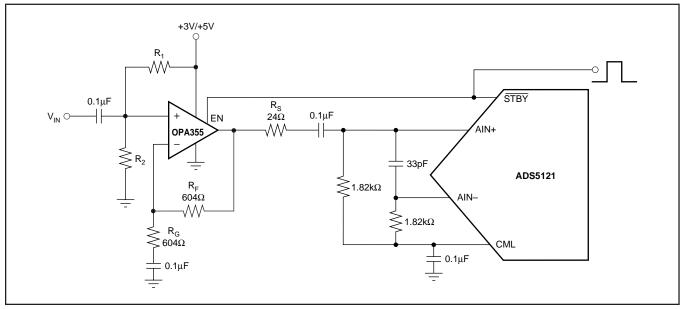

#### Single-Ended, AC-Coupled Driver

The circuit of Figure 2 shows an example for driving the inputs of the ADS5121 in a single-ended configuration. The signal is AC-coupled between the driver amplifier and the converter input (AIN+). This allows for setting the required common-mode voltages for the ADC and op amp separately. The single-supply op amp is biased at mid-supply by two resistors connected at its noninverting input. Connecting each input to the CML pin provides the required common-mode voltage for the inputs of the ADS5121. Here, two resistors of equal value ensure that the inputs see closely

matched source impedances. If the op amp features a disable function, it could be easily tied together with the power-down pin of the ADS5121 channel ( $\overline{STBY}$ ). In the circuit example depicted in Figure 2, the OPA355 EN pin is directly connected to the  $\overline{STBY}$  pin to allow for a power-down mode of the entire circuit. Other suitable op amps for single-supply driver applications include the OPA634, OPA635, or OPA690, for example.

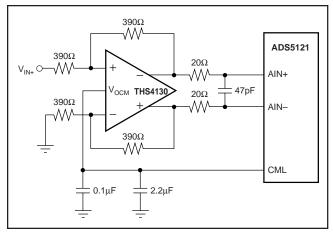

#### **DC-Coupled Interface with Differential Amplifier**

Differential input/output amplifiers can simplify the driver circuit for applications requiring input DC-coupling. Flexible in their configurations, such amplifiers can be used for singleended to differential conversion, allow for signal amplification, and also for filtering prior to the ADC. See Figure 3 for one possible circuit implementation using the THS4130 amplifier. Here, the amplifier operates with a gain of +1. The common- mode voltage available at the CML pin can be conveniently connected to the amplifier VOCM pin to set the required input bias for the ADS5121.

FIGURE 1. Converting a Single-Ended Input Signal into a Differential Signal Using an RF-Transformer.

FIGURE 2. Single-Ended, AC-Coupled Driver Configuration for a Single Supply.

FIGURE 3. DC-Coupled Interface Using Differential I/O Amplifier THS4130.

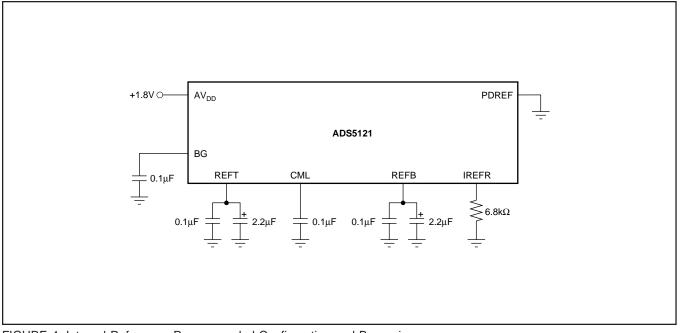

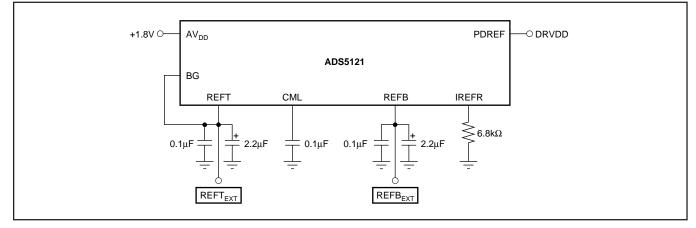

#### **REFERENCE OPERATION**

For proper operation of the ADS5121 and its reference, an external  $6.8k\Omega$  resistor must be connected from the IREFR pin to analog ground (AGND), as shown in Figure 4. While a 1% resistor tolerance is adequate, deviating from this resistor value will cause altered and degraded performance.

To ensure proper operation with any reference configuration, it is necessary to provide solid bypassing at all reference pins in order to keep the clock feedthrough to a minimum. Figure 4 shows the recommended decoupling scheme. Good performance can be obtained using  $0.1\mu$ F low inductance ceramic capacitors. Adding tantalum capacitors ( $1\mu$ F to  $10\mu$ F) may lead to a performance improvement, depending on the application. All bypassing capacitors should be located as close as possible to their respective pins.

#### INTERNAL REFERENCE

The internal reference circuit of the ADS5121 consists of a bandgap voltage reference, the drivers for the top and bottom reference, and the resistive reference ladder. The corresponding reference pins are REFT, REFB, CML, IREFR, BG, and PDREF. In order to enable the internal reference, PDREF must be at a logic LOW (= 0) level. In addition, the bandgap pin BG should be decoupled with a 0.1 $\mu$ F capacitor. The reference circuit provides the reference voltages to each of the eight channels.

The reference buffers can be utilized to supply up to 1mA (sink and source) to an external circuitry. The CML pin represents the mid-point of the internal resistor ladder and is an unbuffered node. Loading of this pin should be avoided, as it will lead to degradation of the converter linearity.

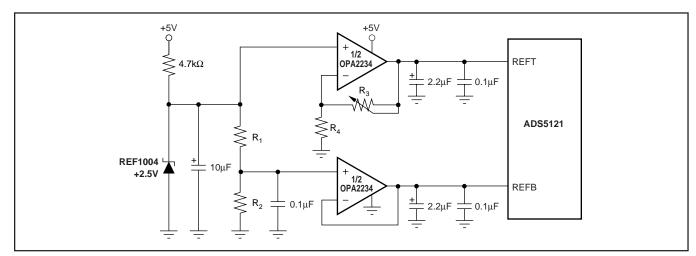

#### USING EXTERNAL REFERENCES

For even more design flexibility, the internal reference can be disabled and an external reference voltage used. The utilization of an external reference may be considered for applications requiring higher accuracy or improved temperature performance. Especially in multi-channel applications, the use of a common external reference has the benefit of obtaining better matching of the full-scale range between converters.

Setting the ADS5121 for external reference mode requires taking the PDREF pin HIGH. In addition, pins BG and REFT must be connected together (see Figure 5). The common-mode voltage at the CML pin will be maintained at approximately the mid-point of the applied reference voltages, according to CML  $\approx$  (VREFT – VREFB)/2. The internal buffer

FIGURE 4. Internal Reference; Recommended Configuration and Bypassing.

amplifiers for REFT and REFB are disabled when the ADS5121 operates in the external reference mode. The external reference circuit must be designed to drive the internal reference ladder (80 $\Omega$ ) located between the REFT and REFB pins. For example, setting REFT = +1.25V and REFB = +0.75V will require a current drive capability of at least 0.5V/80 $\Omega$  = 6.25mA. The external references can vary as long as the value of the external top reference (REFT<sub>EXT</sub>) stays within the range of +1.15V to +1.35V, and the external bottom reference (REFB<sub>EXT</sub>) stays within +0.65V to +0.85V (as shown in Figure 6).

#### DIGITAL INPUTS AND OUTPUTS Clock Input

The clock input is designed to operate with +1.8V or +3.3V CMOS logic levels. The clock circuitry is internally connected to the  $DRV_{DD}$  supply. Therefore, the input HIGH and LOW levels will vary depending on the applied  $DRV_{DD}$  supply; see the *DC Characteristics* tables. Since both edges of the clock are used in this pipeline ADC, the ideal clock should be a square-wave logic signal with a 50% duty-cycle.

Since this condition cannot always easily be met, the ADS5121 features an internal clock conditioning circuitry that can be activated through the duty-cycle adjust pin (DCASEL).

The DCASEL pin is a logic input, with its logic levels related to the DV<sub>DD</sub> supply (+1.8V only):

- a) DCASEL = LOW (GND); in this mode the clock conditioning circuitry is disabled. Use this setting if the applied clock signal is a square-wave clock with a duty cycle of 50%, or if the duty cycle stays within a range of 48% to 52%.

- b) DCASEL = HIGH (DV<sub>DD</sub>); in this mode the clock conditioning circuitry is enabled. Use this setting if the applied external clock signal is a square-wave clock that does not meet the criteria listed above, but has a duty cycle in the range of 30% to 70%.

#### MINIMUM SAMPLING RATE

The pipeline architecture of the ADS5121 uses a switched capacitor technique for the internal track-and-hold stages. With each clock cycle, charges representing the captured signal level are moved within the ADC pipeline core. The high sampling rate necessitates the use of very small capacitor values. In order to hold the droop errors low, the capacitors require a minimum refresh rate. To maintain full accuracy of the acquired sample charge, the sampling clock of the ADS5121 should not be lower than the specified minimum of 5MSPS.

FIGURE 5. External Reference; Recommended Configuration and Bypassing.

FIGURE 6. Circuit Example of an External Reference Circuit Using a Single-Supply, Low-Power, Dual Op Amp (OPA2234).

#### DATA OUTPUT FORMAT

The output data format of the ADS5121 is a positive Straight Offset Binary (SOB) code. Tables I and II show output coding of a single-ended and differential signal. For all data output channels, the MSBs are located at the D9x pins.

| SINGLE-ENDED INPUT<br>(AIN- = CML) | STRAIGHT OFFSET BINARY<br>(SOB) |

|------------------------------------|---------------------------------|

| +FS – 1LSB (AIN+ = CML + FSR/2)    | 11 1111 1111                    |

| +1/2 FS                            | 11 0000 0000                    |

| Bipolar Zero (AIN+ = CML)          | 10 0000 0000                    |

| -1/2 FS                            | 01 0000 0000                    |

| -FS (AIN+ = CML - FSR/2)           | 00 0000 0000                    |

TABLE I. Coding Table for Single-Ended Input Configuration with Input AIN– Tied to the Common-Mode Voltage (CML).

| DIFFERENTIAL INPUT                    | STRAIGHT OFFSET BINARY<br>(SOB) |

|---------------------------------------|---------------------------------|

| +FS – 1LSB (AIN+ = REFT, AIN– = REFB) | 11 1111 1111                    |

| +1/2 FS                               | 11 0000 0000                    |

| Bipolar Zero (AIN+ = AIN- = CML)      | 10 0000 0000                    |

| -1/2 FS                               | 01 0000 0000                    |

| –FS (AIN+ = REFB, AIN– = REFT)        | 00 0000 0000                    |

TABLE II. Coding Table for Differential Input Configuration and  $1V_{PP}$  Full-Scale Range.

#### DIGITAL OUTPUT LOADING

Minimizing the capacitive loading on the digital outputs is very important in achieving the best performance. The total load capacitance is typically made up of two sources: the next stage input capacitance, and the parasitic/printed circuit board (PCB) capacitance. It is recommended to keep the total capacitive loading on the data lines as low as possible (≤ 20pF). Higher capacitive loading will cause larger dynamic currents as the digital outputs are dynamic states. High current surges may cause feedback into the analog portion of the ADS5121 and affect the performance. If necessary, external buffers or latches close to the converter output pins may be used to minimize the capacitive loading. A suggested device is the SN74AVC16827 (20-bit buffer/driver), a member of the Advanced Very Low Voltage CMOS logic family (AVC). Using such a logic device can also provide the added benefit of isolating the ADS5121 from any digital noise activities on the bus coupling back high-frequency noise. Some applications may also benefit from the use of series resistors ( $\leq 100\Omega$ ) in the data lines. This will provide a current limit and reduce any existing over- or undershoot.

#### **OUTPUT ENABLE**

The ADS5121 provides one output enable pin  $(\overline{OE})$  that controls the digital outputs of all channels simultaneously. A LOW (L = 0) level on the  $\overline{OE}$  pin will have all channels active and the converter in normal operation. Taking the  $\overline{OE}$  pin HIGH (H = 1) will disable or tri-state the outputs of all channels. Note that the  $\overline{OE}$  pin has no internal pull-up

resistor and therefore requires a defined potential to be applied. The timing relations between  $\overline{OE}$  and the output bus enable/disable times are shown in the Timing Diagram.

#### POWER-UP SEQUENCE

Ideally, the three main power supplies for the ADS5121 should be applied and ramped up simultaneously. If this cannot be ensured, the following power-up sequence is recommended:

- 1.  $AV_{DD}$  (+1.8 typ)

- 2. DV<sub>DD</sub> (+1.8 typ)

- 3. DRV<sub>DD</sub> (+3.3 typ)

The clock signal should also be applied with proper logic levels during power-up of the ADS5121. Deviating from this power-up sequence may cause the device to enter a mode such that the digital outputs do not approach the full specified output levels.

#### **POWER-DOWN (STANDBY)**

The ADS5121 is equipped with a power-down function for each of the eight channels. Labeled as  $\overline{STBY}$  pins, the channel is in normal operating mode when the  $\overline{STBY}$  pin is connected to logic high (H = 1). The selected ADC channel will be in a power-down mode if the corresponding  $\overline{STBY}$  pin is connected to logic LOW (L = 0). The logic levels for the  $\overline{STBY}$  pins are dependent on the DRV<sub>DD</sub> supply. The powerdown function controls internal biasing nodes, and as a consequence, any data present in the pipeline of the converter will become invalid. This is independent of whether the clock remains applied during power-down or not. Following a power-up, new valid data will become available after a minimum of seven clock cycles. As a note, the operation of the  $\overline{STBY}$  pins is not intended for the use of dynamically multiplexing between the eight channels of the ADS5121.

#### DIGITAL OUTPUT DRIVER SUPPLY, DRV<sub>DD</sub>

The ADS5121 uses a dedicated supply connection for the output logic drivers,  $DRV_{DD}$ , along with its digital driver ground connections, labeled DRGND.

Setting the voltage at  $DRV_{DD}$  to either +3.3V or +1.8V also sets the output logic levels accordingly, allowing the ADS5121 to directly interface to a selected logic family. The output stages are designed to supply sufficient current to drive a variety of logic families. However, it is recommended to use the ADS5121 with a +1.8V driver supply. This will lower the power dissipation in the output stages due to the lower output swing and reduce current glitches on the supply lines, which otherwise may affect the AC performance of the converter. In some applications it might be advantageous to decouple the DRV<sub>DD</sub> supply with additional capacitors or a pi-filter.

#### **GROUNDING AND DECOUPLING**

Proper grounding and bypassing, short lead length, and the use of ground planes are particularly important for highfrequency designs. Multilayer PCBs are recommended for best performance since they offer distinct advantages such

as minimizing ground impedance, separation of signal layers by ground layers, etc. The ADS5121 should be treated as an analog component. Whenever possible, the supply pins should be powered by the analog supply. This will ensure the most consistent results, since digital supply lines often carry high levels of noise which otherwise would be coupled into the converter and degrade the achievable performance. The ground pins should directly connect to an analog ground plane covering the PCB area under the converter. While designing the layout it is important to keep the analog signal traces separated from any digital line to prevent noise coupling onto the analog signal path. Due to its high sampling rate, the ADS5121 generates high-frequency current transients and noise (clock feedthrough) that are fed back into the supply and reference lines. This requires that all supply and reference pins are sufficiently bypassed. In most cases 0.1µF ceramic chip capacitors at each pin are adequate to keep the impedance low over a wide frequency range. Their effectiveness depends largely on the proximity to the individual supply pin. Therefore, they should be located as close as possible to the supply pins. In addition, a larger bipolar capacitor (1µF to 22µF) should be placed on the PCB in proximity to the converter circuit.

#### LAYOUT OF THE PCB WITH A MICROSTAR BGA PACKAGE

The ADS5121 is housed in a polyimide film-based chipscale package (CSP). Like most CSPs, solder alloy balls are used as the interconnect between the package substrate and the PCB on which the package is soldered. For detailed information regarding these packages, please refer to literature number SSYZ015B, MicroStar BGA Packaging Reference Guide, which addresses the specific considerations required when integrating a MicroStar BGA package into the PCB design. This document can be found at:

http://www-s.ti.com/sc/psheets/ssyz015b/ssyz015b.pdf

### TERMINOLOGY

#### ANALOG BANDWIDTH

The analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3dB.

#### APERTURE DELAY

The delay between the 50% point of the rising edge of the clock and the instant at which the analog input is sampled.

#### **APERTURE UNCERTAINTY (JITTER)**

The sample-to-sample variation in aperture delay.

#### **EFFECTIVE NUMBER OF BITS (ENOB)**

The ENOB is calculated from the measured SINAD based on the equation:

$$\mathsf{ENOB} = \left(\frac{\mathsf{SINAD} - 1.76\mathsf{dB}}{6.02}\right)$$

#### EFFECTIVE RESOLUTION BANDWIDTH

The maximum analog input frequency at which the SINAD is decreased by 3dB or the ENOB by half a bit.

#### GAIN ERROR

Gain Error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

#### GAIN MATCHING

Variation in Gain Error between adjacent channels.

#### 2ND-HARMONIC DISTORTION

The ratio of the rms signal amplitude to the rms value of the 2nd-harmonic component, reported in dBc.

#### **3RD-HARMONIC DISTORTION**

The ratio of the rms signal amplitude to the rms value of the 3rd-harmonic component, reported in dBc.

#### **INTERMODULATION DISTORTION (IMD)**

The 2-tone IMD is the ratio expressed in decibels of either input tone to the worst 3rd-order (or higher) Intermodulation products. The individual input tone levels are at -6.5dB full-scale, and their envelope is at -0.5dB full-scale.

#### OFFSET ERROR (ZERO-SCALE ERROR)

The first transition should occur for an analog value 1/2 LSB above negative full-scale. Offset error is defined as the deviation of the actual transition from that point.

#### **OFFSET MATCHING**

The change in offset error between adjacent channels.

#### POWER-SUPPLY REJECTION RATIO (PSRR)

The ratio of a change in input offset voltage to a change in power-supply voltage.

#### SIGNAL-TO-NOISE AND DISTORTION (SINAD)

The ratio of the rms signal amplitude (set 0.5dB below fullscale) to the rms value of the sum all other spectral components, including harmonics but excluding DC.

#### SIGNAL-TO-NOISE RATIO (WITHOUT HARMONICS)

The ratio of the rms signal amplitude (set 0.5dB below fullscale) to the rms value of the sum of all other spectral components, excluding the first five harmonics and DC.

#### SPURIOUS-FREE DYNAMIC RANGE (SFDR)

The ratio of the rms signal amplitude to the rms value of the peak spurious spectral component. The peak spurious component may or may not be a harmonic. May be reported in dBc (that is, degrades as signal level is lowered), or dBFS (always related back to converter full-scale).

### **Revision History**

| DATE  | REVISION | PAGE   | SECTION                                                   | DESCRIPTION                                                                                                                                                                     |

|-------|----------|--------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5/06  | D        | 17     | Application Information                                   | Added Revision History table.                                                                                                                                                   |

| 11/05 | С        | 2      | Package/Ordering Table                                    | Include the new package designator ZHK for green/Pb-free package.                                                                                                               |

| 6/05  | В        | 3      | DC Characteristics                                        | Corrected typos: Power Dissipation-removed hyphen                                                                                                                               |

|       |          | 14     | Application Information                                   | Corrected Figure 5. Remove trace connection between ${\rm AV}_{\rm DD}$ 1.8V input and PDREF output, identify PDREF output as ${\rm DRV}_{\rm DD}$                              |

|       |          | 15, 16 | Application Information                                   | Corrected "PC-board" as "printed circuit board (PCB)"                                                                                                                           |

| 6/04  | Ratings  |        |                                                           | Changed incorrect spec in AbsMax table: Was: Clock Input CLK to DGND: $-0.3V$ to AV <sub>DD</sub> +0.3V Changed to: Clock input CLK to DGND: $-0.3V$ to DRV <sub>DD</sub> +0.3V |

|       |          | 3      | DC Characteristics                                        | Changed Input Resistance $R_{IN}$ from $83k\Omega$ to $31k\Omega.$ Added CLK to Digital Inputs list.                                                                            |

|       |          | 11     | Driving Analog Inputs,<br>Differential vs<br>Single-Ended | Added definition of full-scale input range and clarified differential input configuration requirements.                                                                         |

|       |          | 15     | Power-Up Sequence                                         | Added Power-Up Sequence section.                                                                                                                                                |

|       |          | 16     | PCB Layout                                                | "polymide" corrected to "polyimide"                                                                                                                                             |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

11-Apr-2013

### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type     | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|------------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)    |                  | Drawing |      | Qty     | (2)                        |                  | (3)                 |              | (4)               |         |

| ADS5121IGHK      | ACTIVE | BGA<br>MICROSTAR | GHK     | 257  | 90      | TBD                        | SNPB             | Level-3-220C-168 HR | -40 to 85    | ADS5121IGHK       | Samples |

| ADS5121IZHK      | ACTIVE | BGA<br>MICROSTAR | ZHK     | 257  | 90      | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-3-260C-168 HR | -40 to 85    | ADS5121IZHK       | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

GHK (S-PBGA-N257)

PLASTIC BALL GRID ARRAY

A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

ZHK (S-PBGA-N257)

PLASTIC BALL GRID ARRAY

Α. All linear dimensions are in millimeters.

Β. This drawing is subject to change without notice.

C. This is a lead-free solder ball design.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated