# 16-Bit, 250kSPS, 6-Channel, Simultaneous Sampling SAR ANALOG-TO-DIGITAL CONVERTERS

# **FEATURES**

www.ti.com

- Six Input Channels

- Fully Differential Inputs

- Six Independent 16-Bit ADCs

- 4µs Total Throughput per Channel

- Low Power: 200mW in Normal Mode 5mW in Nap Mode 50μW in Power-Down Mode

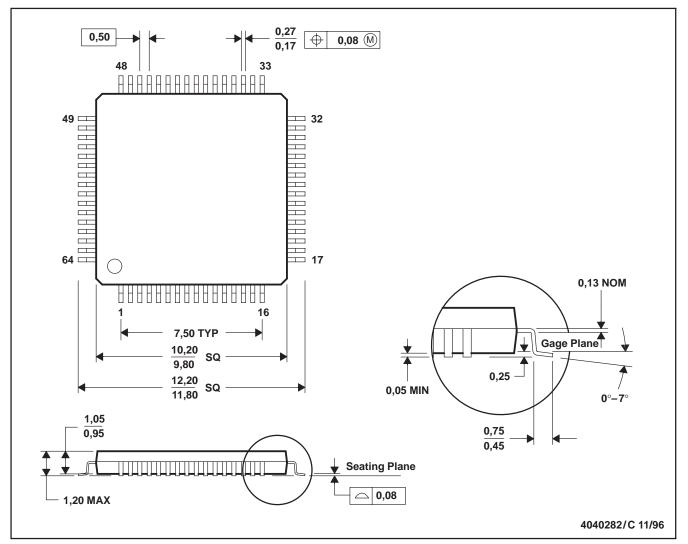

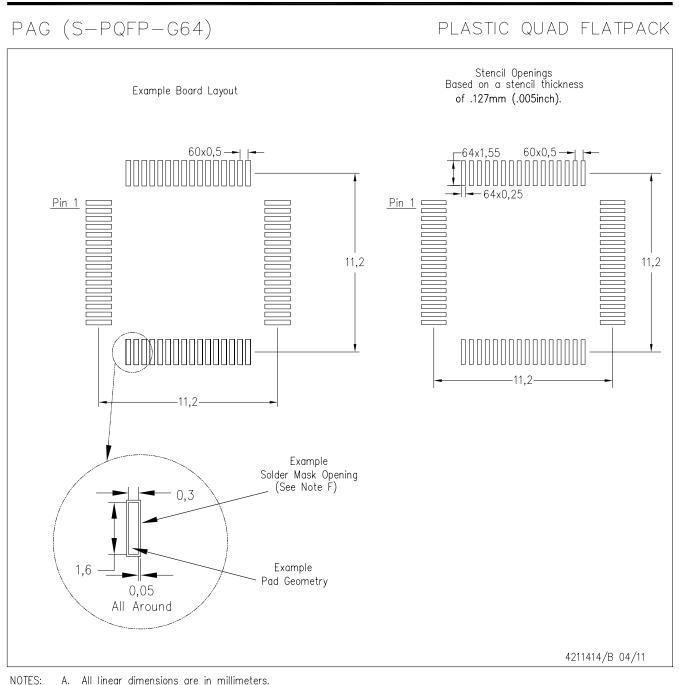

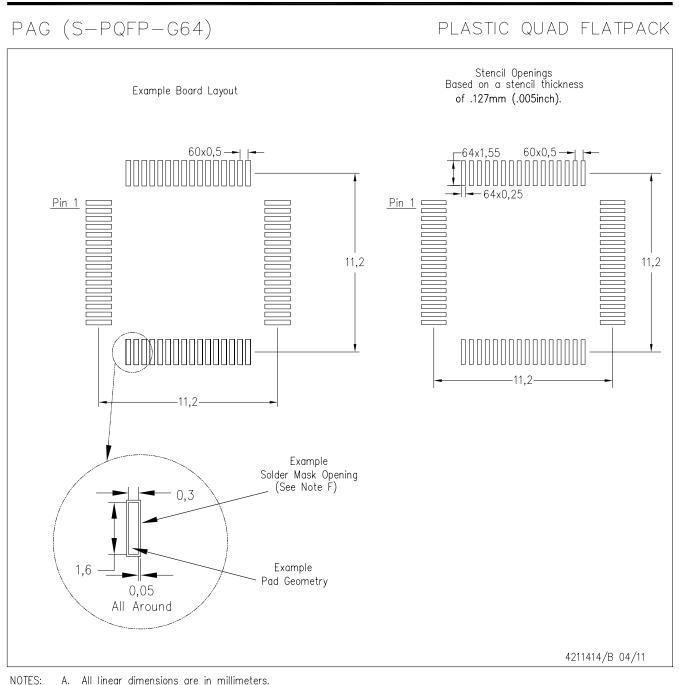

- TQFP-64 Package Package

# APPLICATIONS

- Motor Control

- Multi-Axis Positioning Systems

- 3-Phase Power Control

# DESCRIPTION

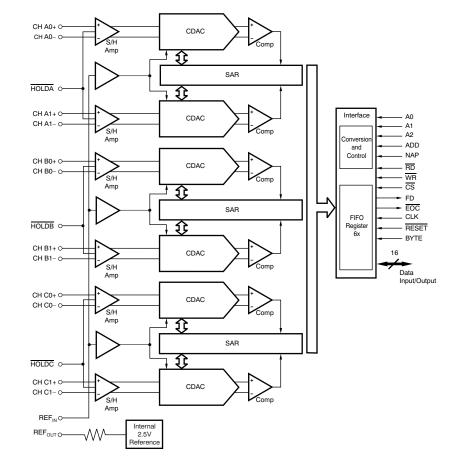

The ADS8365 includes six, 16-bit, 250kSPS analog-to-digital converters (ADCs) with six fully differential input channels grouped into three pairs for high-speed simultaneous signal acquisition. Inputs to the sample-and-hold amplifiers are fully differential and are maintained differential to the input of the provides ADC. This architecture excellent common-mode rejection of 80dB at 50kHz, which is important in high-noise environments.

The ADS8365 offers a flexible, high-speed parallel interface with a direct address mode, a cycle, and a FIFO mode. The output data for each channel is available as a 16-bit word.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# ADS8365

#### SBAS362C-AUGUST 2006-REVISED MARCH 2008

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>ERROR<br>(LSB) | NO<br>MISSING<br>CODES<br>ERROR<br>(LSB) | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|---------|----------------------------------------------------|------------------------------------------|------------------|-----------------------|-----------------------------------|--------------------|--------------------|---------------------------------|

|         |                                                    |                                          |                  |                       |                                   |                    | ADS8365IPAG        | Tray, 160                       |

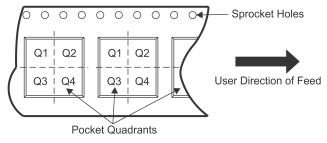

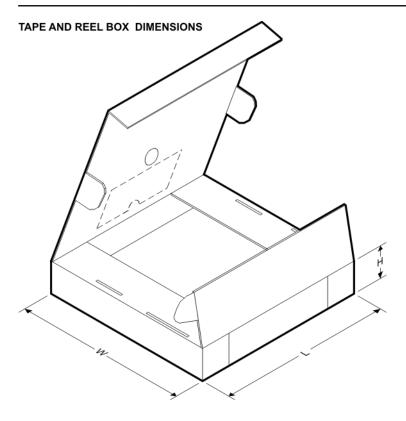

| ADS8365 | ±4                                                 | 14                                       | TQFP-64          | PAG                   | –40°C to +85°C                    | ADS8365AI          | ADS8365IPAGR       | Tape and<br>Reel, 1500          |

#### **ORDERING INFORMATION**<sup>(1)</sup>

(1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet, or see the TI website at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                              | ADS8365                              | UNIT |

|--------------------------------------------------------------|--------------------------------------|------|

| Supply voltage, AGND to AV <sub>DD</sub>                     | -0.3 to 6                            | V    |

| Supply voltage, BGND to BV <sub>DD</sub>                     | -0.3 to 6                            | V    |

| Analog input voltage range                                   | AGND – 0.3 to AV <sub>DD</sub> + 0.3 | V    |

| Reference input voltage range                                | AGND – 0.3 to AV <sub>DD</sub> + 0.3 | V    |

| Digital input voltage range                                  | BGND – 0.3 to BV <sub>DD</sub> + 0.3 | V    |

| Ground voltage differences, AGND to BGND                     | ±0.3                                 | V    |

| Voltage differences, BV <sub>DD</sub> to AGND                | -0.3 to 6                            | V    |

| Input current to any pin except supply                       | -20 to 20                            | mA   |

| Power dissipation                                            | See Dissipation Ratings Ta           | ble  |

| Operating virtual junction temperature range, T <sub>J</sub> | -40 to +150                          | ٥°   |

| Operating free-air temperature range, T <sub>A</sub>         | -40 to +85                           | °C   |

| Storage temperature range, T <sub>STG</sub>                  | -65 to +150                          | ٥°   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum rated conditions for extended periods may affect device reliability.

# **DISSIPATION RATINGS**

| BOARD                 | PACKAGE | $R_{	heta JC}$ | $R_{	extsf{	heta}JA}$ | DERATING<br>FACTOR ABOVE<br>T <sub>A</sub> = +25°C | T <sub>A</sub> ≤ +25°C<br>POWER RATING | T <sub>A</sub> = +70°C<br>POWER RATING | T <sub>A</sub> = +85°C<br>POWER RATING |

|-----------------------|---------|----------------|-----------------------|----------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| Low-K <sup>(1)</sup>  | PAG     | 8.6°C/W        | 68.5°C/W              | 14.598mW/°C                                        | 1824mW                                 | 1168mW                                 | 949mW                                  |

| High-K <sup>(2)</sup> | PAG     | 8.6°C/W        | 42.8°C/W              | 23.364mW/°C                                        | 2920mW                                 | 1869mW                                 | 1519mW                                 |

(1) The JEDEC Low K (1s) board design used to derive this data was a 3-inch x 3-inch, two-layer board with 2-ounce copper traces on top of the board.

(2) The JEDEC High K (2s2p) board design used to derive this data was a 3-inch x 3-inch, multilayer board with 1-ounce internal power and ground planes, and 2-ounce copper traces on the top and bottom of the board.

# **RECOMMENDED OPERATING CONDITIONS**

|                                                      |                    | MIN  | NOM | MAX               | UNIT |

|------------------------------------------------------|--------------------|------|-----|-------------------|------|

| Supply voltage, AV <sub>DD</sub> to AGND             |                    | 4.75 | 5   | 5.25              | V    |

|                                                      | Low-voltage levels | 2.7  |     | 3.6               | V    |

| Supply voltage, BV <sub>DD</sub> to BGND             | 5V logic levels    | 4.5  | 5   | 5.5               | V    |

| Reference input voltage                              |                    | 1.5  | 2.5 | 2.6               | V    |

| Operating common-mode signal, -IN                    |                    | 2.2  | 2.5 | 2.8               | V    |

| Analog inputs, +IN – (–IN)                           |                    | 0    |     | ±V <sub>REF</sub> | V    |

| Operating junction temperature range, T <sub>J</sub> |                    | -40  |     | +125              | °C   |

# **ELECTRICAL CHARACTERISTICS: 100kSPS**

Over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $AV_{DD} = 5$ V,  $BV_{DD} = 3$ V,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 2$ MHz, and  $f_{SAMPLE} = 100$ kSPS, unless otherwise noted.

|                                             |                                                           |      | ADS8365            |               |        |

|---------------------------------------------|-----------------------------------------------------------|------|--------------------|---------------|--------|

| PARAMETER                                   | TEST CONDITIONS                                           | MIN  | TYP <sup>(1)</sup> | MAX           | UNIT   |

| ANALOG INPUT                                |                                                           |      |                    | <sup>I</sup>  |        |

| Full-scale range FS                         | R +IN – (–IN)                                             |      |                    | $\pm V_{REF}$ | V      |

| Operating common-mode signal                |                                                           | 2.2  |                    | 2.8           | V      |

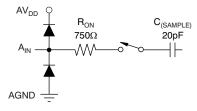

| Input resistance                            | $-IN = V_{REF}$                                           |      | 750                |               | Ω      |

| Input capacitance                           | $-IN = V_{REF}$                                           |      | 25                 |               | pF     |

| Input leakage current                       | $-IN = V_{REF}$                                           |      | ±1                 |               | nA     |

| Differential input resistance               | $-IN = V_{REF}$                                           |      | 1500               |               | Ω      |

| Differential input capacitance              | $-IN = V_{REF}$                                           |      | 15                 |               | pF     |

|                                             | At dc                                                     |      | 84                 |               | dB     |

| Common-mode rejection ratio CMR             | $R = \frac{1.25V_{PP}}{V_{IN}} = \pm 1.25V_{PP}$ at 50kHz |      | 80                 |               | dB     |

| Bandwidth B                                 | V FS sinewave, –3dB                                       |      | 10                 |               | MHz    |

| DC ACCURACY                                 |                                                           |      |                    | <sup>I</sup>  |        |

| Resolution                                  |                                                           |      | 16                 |               | Bits   |

| No missing codes NM                         | c                                                         | 14   |                    |               | Bits   |

| Integral linearity error IN                 | L                                                         |      | ±1.5               | ±4            | LSB    |

| Differential nonlinearity DN                | L                                                         |      | ±1.5               |               | LSB    |

| Bipolar offset error V <sub>C</sub>         | IS                                                        |      | ±1                 | ±2.3          | mV     |

| Bipolar offset error match                  | Only pair-wise matching                                   |      | 0.2                | 1             | mV     |

| Bipolar offset error drift TCV <sub>C</sub> | IS                                                        |      | 0.8                |               | ppm/°C |

| Gain error G <sub>ER</sub>                  | R Referenced to V <sub>REF</sub>                          |      | ±0.05              | ±0.25         | %FSR   |

| Gain error match                            | Only pair-wise matching                                   |      | 0.005              | 0.05          | %FSR   |

| Gain error drift TCG <sub>ER</sub>          | R                                                         |      | 2                  |               | ppm/°C |

| Noise                                       |                                                           |      | 60                 |               | μVrms  |

| Power-supply rejection ratio PSR            | R 4.75V < AV <sub>DD</sub> < 5.25V                        |      | -87                |               | dB     |

| SAMPLING DYNAMICS                           |                                                           |      |                    |               |        |

| Conversion time per ADC t <sub>CON</sub>    | $_{\rm IV}$ 50kHz $\leq$ f <sub>CLK</sub> $\leq$ 5MHz     | 3.2  |                    | 320           | μs     |

| Acquisition time t <sub>A</sub>             | <sub>Q</sub> f <sub>CLK</sub> = 5MHz                      | 800  |                    |               | ns     |

| Aperture delay                              |                                                           |      |                    | 5             | ns     |

| Aperture delay matching                     |                                                           |      | 100                |               | ps     |

| Aperture jitter                             |                                                           |      | 50                 |               | ps     |

| Clock frequency                             |                                                           | 0.05 |                    | 5             | MHz    |

Product Folder Link(s): ADS8365

(1) All typical values are at +25°C.

**NSTRUMENTS**

EXAS

# ELECTRICAL CHARACTERISTICS: 100kSPS (continued)

Over recommended operating free-air temperature range at -40°C to +85°C, AV<sub>DD</sub> = 5V, BV<sub>DD</sub> = 3V, V<sub>REF</sub> = internal +2.5V, f<sub>CLK</sub> = 2MHz, and  $f_{SAMPLE} = 100kSPS$ , unless otherwise noted.

|                                     |                       |                                                          |                     | ADS8365                |              |

|-------------------------------------|-----------------------|----------------------------------------------------------|---------------------|------------------------|--------------|

| PARAMETER                           |                       | TEST CONDITIONS                                          | MIN                 | TYP <sup>(1)</sup> MAX | ( UNIT       |

| AC ACCURACY                         |                       |                                                          |                     |                        |              |

| Total harmonic distortion           | THD                   | $V_{IN} = \pm 2.5 V_{PP}$ at 50kHz                       |                     | -94                    | dB           |

| Spurious-free dynamic range         | SFDR                  | $V_{IN} = \pm 2.5 V_{PP}$ at 50kHz                       |                     | 95                     | dB           |

| Signal-to-noise ratio               | SNR                   | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz                       |                     | 88                     | dB           |

| Signal-to-noise + distortion        | SINAD                 | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz                       |                     | 87                     | dB           |

| Channel-to-channel isolation        |                       |                                                          |                     | 95                     | dB           |

| Effective number of bits            | ENOB                  |                                                          |                     | 14.3                   | Bits         |

| VOLTAGE REFERENCE OUTPUT            |                       |                                                          |                     |                        |              |

| Reference voltage output            | V <sub>OUT</sub>      |                                                          | 2.475               | 2.5 2.52               | 5 V          |

| Initial accuracy                    |                       |                                                          |                     | ±                      | 1 %          |

| Output voltage temperature drift    | dV <sub>OUT</sub> /dT |                                                          |                     | ±20                    | ppm/°C       |

|                                     |                       | f = 0.1Hz to 10Hz, $C_L = 10\mu F$                       |                     | 40                     | $\mu V_{PP}$ |

| Output voltage noise                |                       | f = 10Hz to 10kHz, $C_L = 10\mu F$                       |                     | 8                      | μVrms        |

| Power-supply rejection ratio        | PSRR                  |                                                          |                     | 60                     | dB           |

| Output impedance                    | R <sub>OUT</sub>      |                                                          |                     | 2                      | kΩ           |

| Short-circuit current               | I <sub>SC</sub>       |                                                          |                     | 1.25                   | mA           |

| Turn-on settling time               |                       | to 0.1% at C <sub>L</sub> = 0pF                          |                     | 100                    | μs           |

| VOLTAGE REFERENCE INPUT             |                       |                                                          | 4                   |                        |              |

| Reference voltage input             | V <sub>IN</sub>       |                                                          | 1.5                 | 2.5 2.                 | 6 V          |

| Reference input resistance          |                       |                                                          | 100                 |                        | MΩ           |

| Reference input capacitance         |                       |                                                          |                     | 5                      | pF           |

| Reference input current             |                       |                                                          |                     |                        | 1 µA         |

| DIGITAL INPUTS <sup>(2)</sup>       |                       |                                                          | I                   |                        |              |

| Logic family                        |                       |                                                          |                     | CMOS                   |              |

| High-level input voltage            | V <sub>IH</sub>       |                                                          | $0.7 	imes BV_{DD}$ | BV <sub>DD</sub> + 0.3 | 3 V          |

| Low-level input voltage             | VIL                   |                                                          | -0.3                | $0.3 	imes BV_{D}$     |              |

| Input current                       | I <sub>IN</sub>       | $V_{I} = BV_{DD}$ or GND                                 |                     | ±50                    | ) nA         |

| Input capacitance                   | CI                    |                                                          |                     | 5                      | pF           |

| DIGITAL OUTPUTS <sup>(2)</sup>      |                       |                                                          | I                   |                        |              |

| Logic family                        |                       |                                                          |                     | CMOS                   |              |

| High-level output voltage           | V <sub>OH</sub>       | BV <sub>DD</sub> = 4.5V, I <sub>OH</sub> = -100μA        | 4.44                |                        | V            |

| Low-level output voltage            | V <sub>OL</sub>       | BV <sub>DD</sub> = 4.5V, I <sub>OL</sub> = 100μA         |                     | 0.                     | 5 V          |

| High-impedance state output current | I <sub>OZ</sub>       | $\overline{CS} = BV_{DD}, V_I = BV_{DD} \text{ or } GND$ |                     | ±50                    | ) nA         |

| Output capacitance                  | C <sub>O</sub>        |                                                          |                     | 5                      | pF           |

| Load capacitance                    | CL                    |                                                          |                     | 3                      | ) pF         |

| DIGITAL INPUTS <sup>(3)</sup>       |                       | 1                                                        | I                   |                        |              |

| Logic family                        |                       |                                                          |                     | LVCMOS                 |              |

| High-level input voltage            | V <sub>IH</sub>       | BV <sub>DD</sub> = 3.6V                                  | 2                   | BV <sub>DD</sub> + 0.3 | 3 V          |

| Low-level input voltage             | VIL                   |                                                          | -0.3                | 0.0                    |              |

| Input current                       | I <sub>IN</sub>       | $V_{I} = BV_{DD}$ or GND                                 |                     | ±5                     |              |

| Input capacitance                   | CI                    |                                                          |                     | 5                      | pF           |

SBAS362C-AUGUST 2006-REVISED MARCH 2008

#### www.ti.com

# ELECTRICAL CHARACTERISTICS: 100kSPS (continued)

Over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $AV_{DD} = 5V$ ,  $BV_{DD} = 3V$ ,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 2$ MHz, and  $f_{SAMPLE} = 100$ kSPS, unless otherwise noted.

|                                     |                  |                                                          |           |        | ADS8365            |      |      |

|-------------------------------------|------------------|----------------------------------------------------------|-----------|--------|--------------------|------|------|

| PARAMETER                           | TEST CONDITIONS  |                                                          | МІ        | N      | TYP <sup>(1)</sup> | MAX  | UNIT |

| DIGITAL OUTPUTS <sup>(4)</sup>      |                  |                                                          |           |        |                    |      |      |

| Logic family                        |                  |                                                          |           |        | LVCMOS             |      |      |

| High-level output voltage           | $V_{OH}$         | $BV_{DD} = 2.7V, I_{OH} = -100\mu A$                     | BVDD – 0. | 2      |                    |      | V    |

| Low-level output voltage            | $V_{OL}$         | $BV_{DD} = 2.7V, I_{OL} = 100\mu A$                      |           |        |                    | 0.2  | V    |

| High-impedance state output current | I <sub>OZ</sub>  | $\overline{CS} = BV_{DD}, V_I = BV_{DD} \text{ or } GND$ |           |        |                    | ±50  | nA   |

| Output capacitance                  | $C_{O}$          |                                                          |           |        | 5                  |      | pF   |

| Load capacitance                    | $C_L$            |                                                          |           |        |                    | 30   | pF   |

| DATA FORMAT                         |                  |                                                          |           |        |                    | ·    |      |

|                                     |                  | Bit DB4 = 1                                              | Bi        | nary   | two's complement   |      |      |

| Data format                         |                  | Bit DB4 = 0                                              | :         | Straig | ht binary coding   |      |      |

| POWER SUPPLY                        |                  |                                                          |           |        |                    |      |      |

| Analog supply voltage A             | V <sub>DD</sub>  |                                                          | 4.7       | 5      |                    | 5.25 | V    |

| Buffer I/O supply voltage E         | N/               | Low-voltage levels                                       | 2.        | 7      |                    | 3.6  | V    |

| Builer I/O supply voltage           | SV <sub>DD</sub> | 5V logic levels                                          | 4.        | 5      |                    | 5.5  | V    |

| Analog operating supply current     | Al <sub>dd</sub> |                                                          |           |        | 38                 | 45   | mA   |

| Duffer I/O encroting cumply current | וח               | BV <sub>DD</sub> = 3V                                    |           |        | 60                 | 90   | μΑ   |

| Buffer I/O operating supply current | BI <sub>DD</sub> | BV <sub>DD</sub> = 5V                                    |           |        | 100                | 150  | μΑ   |

|                                     |                  | BV <sub>DD</sub> = 3V                                    |           |        | 190                | 225  | mW   |

| Power dissinction                   |                  | BV <sub>DD</sub> = 5V                                    |           |        | 190                | 225  | mW   |

| Power dissipation                   |                  | Nap mode enabled                                         |           |        |                    | 5    | mW   |

|                                     |                  | Powerdown enabled                                        |           |        |                    | 50   | μW   |

(4) Applies for 3.0V nominal supply:  $BV_{DD}$  (min) = 2.7V and  $BV_{DD}$  (max) = 3.6V.

SBAS362C-AUGUST 2006-REVISED MARCH 2008

#### www.ti.com

# **ELECTRICAL CHARACTERISTICS: 250kSPS**

Over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $AV_{DD} = 5$ V,  $BV_{DD} = 3$ V,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 5$ MHz, and  $f_{SAMPLE} = 250$ kSPS, unless otherwise noted

|                                              |                                     |      | ADS8365            |               |        |

|----------------------------------------------|-------------------------------------|------|--------------------|---------------|--------|

| PARAMETER                                    | TEST CONDITIONS                     | MIN  | TYP <sup>(1)</sup> | MAX           | UNIT   |

| ANALOG INPUT                                 |                                     |      |                    |               |        |

| Full-scale range FSR                         | +IN - (-IN)                         |      |                    | $\pm V_{REF}$ | V      |

| Operating common-mode signal                 |                                     | 2.2  |                    | 2.8           | V      |

| Input resistance                             | $-IN = V_{REF}$                     |      | 750                |               | Ω      |

| Input capacitance                            | $-IN = V_{REF}$                     |      | 25                 |               | pF     |

| Input leakage current                        | $-IN = V_{REF}$                     |      | ±1                 |               | nA     |

| Differential input resistance                | $-IN = V_{REF}$                     |      | 1500               |               | Ω      |

| Differential input capacitance               | $-IN = V_{REF}$                     |      | 15                 |               | pF     |

|                                              | At dc                               |      | 84                 |               | dB     |

| Common-mode rejection ratio CMRR             | $V_{IN} = \pm 1.25 V_{PP}$ at 50kHz |      | 80                 |               | dB     |

| Bandwidth BW                                 | FS sinewave, –3dB                   |      | 10                 |               | MHz    |

| DC ACCURACY                                  | ·                                   |      |                    |               |        |

| Resolution                                   |                                     |      | 16                 |               | Bits   |

| No missing codes NMC                         |                                     | 14   |                    |               | Bits   |

| Integral linearity error INL                 |                                     |      | ±3                 | ±8            | LSB    |

| Differential nonlinearity DNL                | Specified for 14 bit                |      | ±1.5               |               | LSB    |

| Bipolar offset error V <sub>OS</sub>         |                                     |      | ±1                 | ±2.3          | mV     |

| Bipolar offset error match                   | Only pair-wise matching             |      | 0.2                | 1             | mV     |

| Bipolar offset error drift TCV <sub>OS</sub> |                                     |      | 0.8                |               | ppm/°C |

| Gain error G <sub>ERR</sub>                  | Referenced to V <sub>REF</sub>      |      | ±0.05              | ±0.25         | %FSR   |

| Gain error match                             | Only pair-wise matching             |      | 0.005              | 0.05          | %FSR   |

| Gain error drift TCG <sub>ERR</sub>          |                                     |      | 2                  |               | ppm/°C |

| Noise                                        |                                     |      | 60                 |               | μVrms  |

| Power-supply rejection ratio PSRR            | 4.75V < AV <sub>DD</sub> < 5.25V    |      | -87                |               | dB     |

| SAMPLING DYNAMICS                            |                                     |      |                    |               |        |

| Conversion time per ADC t <sub>CONV</sub>    | $50$ kHz $\leq f_{CLK} \leq 5$ MHz  | 3.2  |                    | 320           | μs     |

| Acquisition time t <sub>AQ</sub>             | f <sub>CLK</sub> = 5MHz             | 800  |                    |               | ns     |

| Throughput rate                              |                                     |      |                    | 250           | kSPS   |

| Aperture delay                               |                                     |      |                    | 5             | ns     |

| Aperture delay matching                      |                                     |      | 100                |               | ps     |

| Aperture jitter                              |                                     |      | 50                 |               | ps     |

| Clock frequency                              |                                     | 0.05 |                    | 5             | MHz    |

| AC ACCURACY                                  |                                     |      |                    |               |        |

| Total harmonic distortion THD                | $V_{IN} = \pm 2.5 V_{PP}$ at 50kHz  |      | -94                |               | dB     |

| Spurious-free dynamic range SFDR             | $V_{IN} = \pm 2.5 V_{PP}$ at 50kHz  |      | 95                 |               | dB     |

| Signal-to-noise ratio SNR                    | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz  |      | 88                 |               | dB     |

| Signal-to-noise + distortion SINAD           | $V_{IN} = \pm 2.5 V_{PP}$ at 10kHz  |      | 87                 |               | dB     |

| Channel-to-channel isolation                 |                                     |      | 95                 |               | dB     |

| Effective number of bits ENOB                |                                     |      | 14.3               |               | Bits   |

(1) All typical values are at  $+25^{\circ}$ C.

SBAS362C-AUGUST 2006-REVISED MARCH 2008

# ELECTRICAL CHARACTERISTICS: 250kSPS (continued)

Over recommended operating free-air temperature range at -40°C to +85°C, AV<sub>DD</sub> = 5V, BV<sub>DD</sub> = 3V, V<sub>REF</sub> = internal +2.5V, f<sub>CLK</sub> = 5MHz, and  $f_{SAMPLE} = 250kSPS$ , unless otherwise noted

|                                     |                       |                                                          |                      | ADS8365            |                        |              |

|-------------------------------------|-----------------------|----------------------------------------------------------|----------------------|--------------------|------------------------|--------------|

| PARAMETER                           |                       | TEST CONDITIONS                                          | MIN                  | TYP <sup>(1)</sup> | MAX                    | UNIT         |

| VOLTAGE REFERENCE OUTPUT            |                       |                                                          |                      |                    |                        |              |

| Reference voltage output            | V <sub>OUT</sub>      |                                                          | 2.475                | 2.5                | 2.525                  | V            |

| Initial accuracy                    |                       |                                                          |                      |                    | ±1                     | %            |

| Output voltage temperature drift    | dV <sub>OUT</sub> /dT |                                                          |                      | ±20                |                        | ppm/°C       |

|                                     |                       | $f = 0.1Hz$ to 10Hz, $C_L = 10\mu F$                     |                      | 40                 |                        | $\mu V_{PP}$ |

| Output voltage noise                |                       | $f = 10Hz$ to 10kHz, $C_L = 10\mu F$                     |                      | 8                  |                        | μVrms        |

| Power-supply rejection ratio        | PSRR                  |                                                          |                      | 60                 |                        | dB           |

| Output impedance                    | R <sub>OUT</sub>      |                                                          |                      | 2                  |                        | kΩ           |

| Short-circuit current               | I <sub>SC</sub>       |                                                          |                      | 1.25               |                        | mA           |

| Turn-on settling time               |                       | to 0.1% at C <sub>L</sub> = 0pF                          |                      | 100                |                        | μs           |

| VOLTAGE REFERENCE INPUT             |                       | I                                                        |                      |                    |                        |              |

| Reference voltage input             | V <sub>IN</sub>       |                                                          | 1.5                  | 2.5                | 2.6                    | V            |

| Reference input resistance          |                       |                                                          | 100                  |                    |                        | MΩ           |

| Reference input capacitance         |                       |                                                          |                      | 5                  |                        | pF           |

| Reference input current             |                       |                                                          |                      |                    | 1                      | μA           |

| DIGITAL INPUTS <sup>(2)</sup>       |                       | I                                                        |                      |                    |                        |              |

| Logic family                        |                       |                                                          |                      | CMOS               |                        |              |

| High-level input voltage            | V <sub>IH</sub>       |                                                          | $0.7 \times BV_{DD}$ |                    | BV <sub>DD</sub> + 0.3 | V            |

| Low-level input voltage             | V <sub>IL</sub>       |                                                          | -0.3                 |                    | $0.3 \times BV_{DD}$   | V            |

| Input current                       | I <sub>IN</sub>       | $V_{I} = BV_{DD}$ or GND                                 |                      |                    | ±50                    | nA           |

| Input capacitance                   | Cl                    |                                                          |                      | 5                  |                        | pF           |

| DIGITAL OUTPUTS <sup>(2)</sup>      |                       |                                                          |                      |                    |                        |              |

| Logic family                        |                       |                                                          |                      | CMOS               |                        |              |

| High-level output voltage           | V <sub>OH</sub>       | BV <sub>DD</sub> = 4.5V, I <sub>OH</sub> = -100μA        | 4.44                 |                    |                        | V            |

| Low-level output voltage            |                       | BV <sub>DD</sub> = 4.5V, I <sub>OL</sub> = 100μA         |                      |                    | 0.5                    | V            |

| High-impedance state output current |                       | $\overline{CS} = BV_{DD}, V_I = BV_{DD} \text{ or } GND$ |                      |                    | ±50                    | nA           |

| Output capacitance                  | Co                    |                                                          |                      | 5                  |                        | pF           |

| Load capacitance                    | CL                    |                                                          |                      |                    | 30                     | pF           |

| DIGITAL INPUTS <sup>(3)</sup>       |                       |                                                          |                      |                    |                        |              |

| Logic family                        |                       |                                                          |                      | LVCMOS             |                        |              |

| High-level input voltage            | VIH                   | BV <sub>DD</sub> = 3.6V                                  | 2                    |                    | BV <sub>DD</sub> + 0.3 | V            |

| Low-level input voltage             |                       | BV <sub>DD</sub> = 2.7V                                  | -0.3                 |                    | 0.8                    | V            |

| Input current                       |                       | $V_{I} = BV_{DD}$ or GND                                 |                      |                    | ±50                    | nA           |

| Input capacitance                   | C                     |                                                          |                      | 5                  |                        | pF           |

| DIGITAL OUTPUTS <sup>(3)</sup>      | -1                    | l                                                        | I                    |                    |                        |              |

| Logic family                        |                       |                                                          |                      | LVCMOS             |                        |              |

| High-level output voltage           | V <sub>OH</sub>       | BV <sub>DD</sub> = 2.7V, I <sub>OH</sub> = -100μA        | BVDD - 0.2           |                    |                        | V            |

| Low-level output voltage            |                       | $BV_{DD} = 2.7V, I_{OL} = 100\mu A$                      |                      |                    | 0.2                    | V            |

| High-impedance state output current | I <sub>OZ</sub>       | $\overline{CS} = BV_{DD}, V_I = BV_{DD} \text{ or } GND$ |                      |                    | ±50                    | nA           |

| Output capacitance                  | C <sub>O</sub>        |                                                          |                      | 5                  |                        | pF           |

| Load capacitance                    | C <sub>L</sub>        |                                                          |                      | -                  | 30                     | pF           |

# **ELECTRICAL CHARACTERISTICS: 250kSPS (continued)**

Over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $AV_{DD} = 5$ V,  $BV_{DD} = 3$ V,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 5$ MHz, and  $f_{SAMPLE} = 250$ kSPS, unless otherwise noted

|                                     |                  |                       |           | ADS8365            |      |      |

|-------------------------------------|------------------|-----------------------|-----------|--------------------|------|------|

| PARAMETER                           |                  | TEST CONDITIONS       | MIN       | TYP <sup>(1)</sup> | MAX  | UNIT |

| DATA FORMAT                         |                  |                       |           |                    |      |      |

| Data format                         |                  | Bit DB4 = 1           | Binary ty | wo's complement    |      |      |

| Data format                         |                  | Bit DB4 = 0           | Straigh   | nt binary coding   |      |      |

| POWER SUPPLY                        |                  |                       |           |                    |      |      |

| Analog supply voltage               | $AV_{DD}$        |                       | 4.75      |                    | 5.25 | V    |

|                                     | DV               | Low-voltage levels    | 2.7       |                    | 3.6  | V    |

| Buffer I/O supply voltage           | $BV_{DD}$        | 5V logic levels       | 4.5       |                    | 5.5  | V    |

| Analog operating supply current     | Al <sub>DD</sub> |                       |           | 40                 | 48   | mA   |

| Puffer I/O energing oursely current | Ы                | $BV_{DD} = 3V$        |           | 150                | 225  | μA   |

| Buffer I/O operating supply current | BI <sub>DD</sub> | BV <sub>DD</sub> = 5V |           | 250                | 375  | μΑ   |

|                                     |                  | $BV_{DD} = 3V$        |           | 200                | 240  | mW   |

| Dower dissignation                  |                  | BV <sub>DD</sub> = 5V |           | 201                | 241  | mW   |

| Power dissipation                   |                  | Nap mode enabled      |           |                    | 5    | mW   |

|                                     |                  | Powerdown enabled     |           |                    | 50   | μW   |

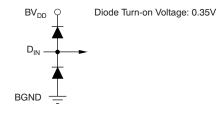

# **EQUIVALENT INPUT CIRCUIT**

Equivalent Analog Input Circuit

Equivalent Digital Input Circuit

#### TEXAS INSTRUMENTS

www.ti.com

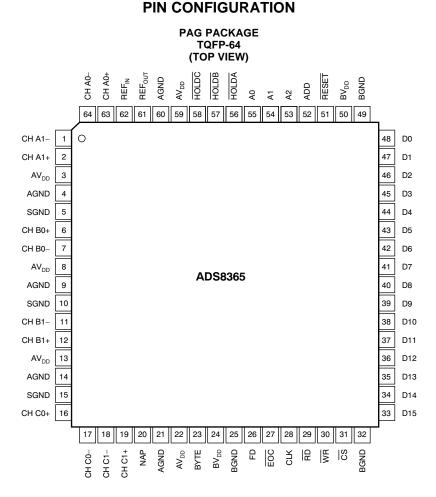

#### **TERMINAL FUNCTIONS**

| TERMINAL         |     |                    |                               |

|------------------|-----|--------------------|-------------------------------|

| NAME             | NO. | I/O <sup>(1)</sup> | DESCRIPTION                   |

| CH A1–           | 1   | AI                 | Inverting input channel A1    |

| CH A1+           | 2   | AI                 | Noninverting input channel A1 |

| AV <sub>DD</sub> | 3   | Р                  | Analog power supply           |

| AGND             | 4   | Р                  | Analog ground                 |

| SGND             | 5   | Р                  | Signal Ground                 |

| CH B0+           | 6   | AI                 | Noninverting input channel B0 |

| CH B0-           | 7   | AI                 | Inverting input channel B0    |

| AV <sub>DD</sub> | 8   | Р                  | Analog power supply           |

| AGND             | 9   | Р                  | Analog ground                 |

| SGND             | 10  | Р                  | Signal ground                 |

| CH B1–           | 11  | AI                 | Inverting input channel B1    |

| CH B1+           | 12  | AI                 | Noninverting input channel B1 |

| AV <sub>DD</sub> | 13  | Р                  | Analog power supply           |

| AGND             | 14  | Р                  | Analog ground                 |

| SGND             | 15  | Р                  | Signal ground                 |

| CH C0+           | 16  | AI                 | Noninverting input channel C0 |

| CH C0-           | 17  | AI                 | Inverting input channel C0    |

| CH C1–           | 18  | AI                 | Inverting input channel C1    |

(1) AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, DIO = Digital Input/Output, and P = Power Supply Connection.

# **TERMINAL FUNCTIONS (continued)**

| TERMINAL         |     |                    |                                                                                                                                |

|------------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                    |

| CH C1+           | 19  | AI                 | Noninverting input channel C1                                                                                                  |

| NAP              | 20  | DI                 | Nap mode.Low level or unconnected = normal operation; high level = Nap mode.                                                   |

| AGND             | 21  | Р                  | Analog ground                                                                                                                  |

| AV <sub>DD</sub> | 22  | Р                  | +5V power supply                                                                                                               |

| BYTE             | 23  | DI                 | 2 x 8 output capability (active high)                                                                                          |

| BV <sub>DD</sub> | 24  | Р                  | Power supply for digital interface from 3V to 5V                                                                               |

| BGND             | 25  | Р                  | Buffer digital ground                                                                                                          |

| FD               | 26  | DO                 | First data (A0 data)                                                                                                           |

| EOC              | 27  | DO                 | End of conversion (active low)                                                                                                 |

| CLK              | 28  | DI                 | An external CMOS compatible clock can be applied to the CLK input to synchronize the conversion process to an external source. |

| RD               | 29  | DI                 | Read (active low)                                                                                                              |

| WR               | 30  | DI                 | Write (active low)                                                                                                             |

| CS               | 31  | DI                 | Chip select (active low)                                                                                                       |

| BGND             | 32  | Р                  | Buffer digital ground                                                                                                          |

| D15              | 33  | DO                 | Data bit 15 (MSB)                                                                                                              |

| D14              | 34  | DO                 | Data bit 14                                                                                                                    |

| D13              | 35  | DO                 | Data bit 13                                                                                                                    |

| D12              | 36  | DO                 | Data bit 12                                                                                                                    |

| D11              | 37  | DO                 | Data bit 11                                                                                                                    |

| D10              | 38  | DO                 | Data bit 10                                                                                                                    |

| D9               | 39  | DO                 | Data bit 9                                                                                                                     |

| D8               | 40  | DO                 | Data bit 8                                                                                                                     |

| D7               | 41  | DIO                | Data bit 7 (software input 7)                                                                                                  |

| D6               | 42  | DIO                | Data bit 6 (software input 6)                                                                                                  |

| D5               | 43  | DIO                | Data bit 5 (software input 5)                                                                                                  |

| D4               | 44  | DIO                | Data bit 4 (software input 4)                                                                                                  |

| D3               | 45  | DIO                | Data bit 3 (software input 3)                                                                                                  |

| D2               | 46  | DIO                | Data bit 2 (software input 2)                                                                                                  |

| D1               | 47  | DIO                | Data bit 1 (software input 1)                                                                                                  |

| D0               | 48  | DIO                | Data bit 0 (software input 0) (LSB)                                                                                            |

| BGND             | 49  | Р                  | Buffer digital ground                                                                                                          |

| BV <sub>DD</sub> | 50  | Р                  | Power supply for digital interface from 3V to 5V                                                                               |

| RESET            | 51  | DI                 | Global reset (active low)                                                                                                      |

| ADD              | 52  | DI                 | Address mode select                                                                                                            |

| A2               | 53  | DI                 | Address line 3                                                                                                                 |

| A1               | 54  | DI                 | Address line 2                                                                                                                 |

| A0               | 55  | DI                 | Address line 1                                                                                                                 |

| HOLDA            | 56  | DI                 | Hold command A (active low)                                                                                                    |

| HOLDB            | 57  | DI                 | Hold command B (active low)                                                                                                    |

| HOLDC            | 58  | DI                 | Hold command C (active low)                                                                                                    |

| AV <sub>DD</sub> | 59  | Р                  | Analog power supply                                                                                                            |

| AGND             | 60  | Р                  | Analog ground                                                                                                                  |

| REFOUT           | 61  | AO                 | Reference output; attach 0.1μF and 10μF capacitors                                                                             |

| REFIN            | 62  | AI                 | Reference input                                                                                                                |

| CH A0+           | 63  | AI                 | Noninverting input channel A0                                                                                                  |

| CH A0-           | 64  | AI                 | Inverting input channel A0                                                                                                     |

TEXAS INSTRUMENTS

www.ti.com

#### SBAS362C-AUGUST 2006-REVISED MARCH 2008

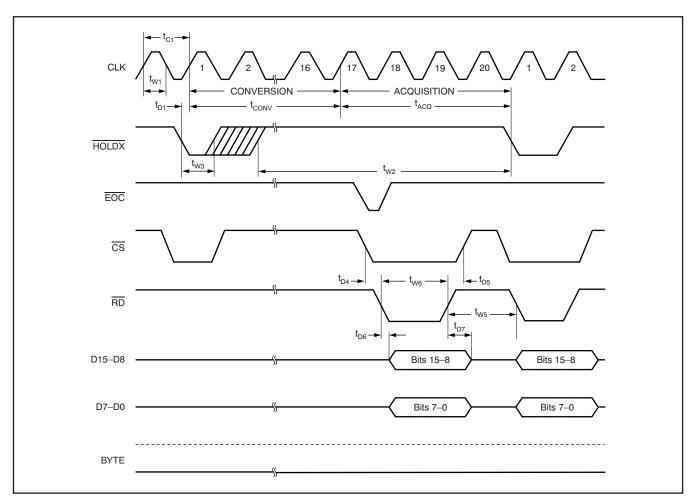

### TIMING INFORMATION

### Figure 1. Read and Convert Timing

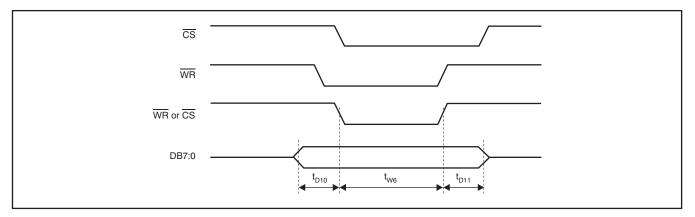

Figure 2. Write Timing

SBAS362C-AUGUST 2006-REVISED MARCH 2008

# TIMING CHARACTERISTICS<sup>(1)(2)(3)(4)</sup>

Over recommended operating free-air temperature range,  $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = 5V$ ,  $REF_{IN} = REF_{OUT}$ ,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 5MHz$ ,  $f_{SAMPLE} = 250kSPS$ , and  $BV_{DD} = 2.7$  to 5V, unless otherwise noted,

| SYMBOL                                                         | DESCRIPTION                                                                                                                                                                        | MIN            | TYP | MAX | UNI |    |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-----|-----|----|

| t <sub>ACQ</sub>                                               | Acquisition time                                                                                                                                                                   |                |     | 0.8 | μs  |    |

| t <sub>CONV</sub>                                              | Conversion time                                                                                                                                                                    |                |     | 3.2 | μs  |    |

| t <sub>C1</sub>                                                | Cycle time of CLK                                                                                                                                                                  | 200            |     |     | ns  |    |

| t <sub>D1</sub> <sup>(5)</sup>                                 | Delay time of rising edge of CLK after falling edge of HOI                                                                                                                         | 10             |     |     | ns  |    |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 20  |     |     | ns |

| t <sub>D2</sub>                                                | Delay time of first hold after RESET                                                                                                                                               | $BV_{DD} = 3V$ | 40  |     |     | ns |

| t <sub>D4</sub>                                                | Delay time of falling edge of $\overline{RD}$ after falling edge of $\overline{CS}$                                                                                                | 0              |     |     | ns  |    |

| t <sub>D5</sub>                                                | Delay time of rising edge of CS after rising edge of RD                                                                                                                            | 0              |     |     | ns  |    |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 40  |     |     | ns |

| ۲ <sub>D6</sub>                                                | D6 Delay time of data valid after falling edge of RD                                                                                                                               |                | 60  |     |     | ns |

|                                                                | Delay time of data valid after falling edge of RD   Delay time of data hold from rising edge of RD   Delay time of RD high after CS low   Delay time of RD low after address setup | $BV_{DD} = 5V$ | 5   |     |     | ns |

| t <sub>D7</sub> Delay time of data hold from rising edge of RD |                                                                                                                                                                                    | $BV_{DD} = 3V$ | 10  |     |     | ns |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 50  |     |     | ns |

| t <sub>D8</sub>                                                | Delay time of RD high after CS low                                                                                                                                                 | $BV_{DD} = 3V$ | 60  |     |     | ns |

| t Do                                                           | Delay time of PD law ofter address actus                                                                                                                                           | $BV_{DD} = 5V$ | 10  |     |     | ns |

| t <sub>D9</sub>                                                | Delay time of RD low after address setup                                                                                                                                           | $BV_{DD} = 3V$ | 20  |     |     | ns |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 10  |     |     | ns |

| t <sub>D10</sub>                                               | Delay time of data valid to WR low                                                                                                                                                 | $BV_{DD} = 3V$ | 20  |     |     | ns |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 10  |     |     | ns |

| t <sub>D11</sub>                                               | Delay time of $\overline{WR}$ or $\overline{CS}$ high to data release                                                                                                              | $BV_{DD} = 3V$ | 20  |     |     | ns |

| t <sub>W1</sub>                                                | Pulse width CLK high time or low time                                                                                                                                              |                | 60  |     |     | ns |

|                                                                | Dulas width of UOLDY kigh time to be recommined again                                                                                                                              | $BV_{DD} = 5V$ | 15  |     |     | ns |

| t <sub>W2</sub>                                                | Pulse width of HOLDX high time to be recognized again                                                                                                                              | $BV_{DD} = 3V$ | 30  |     |     | ns |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 20  |     |     | ns |

| t <sub>W3</sub>                                                | Pulse width of HOLDX low time                                                                                                                                                      | $BV_{DD} = 3V$ | 30  |     |     | ns |

|                                                                |                                                                                                                                                                                    | $BV_{DD} = 5V$ | 20  |     |     | ns |

| t <sub>W4</sub>                                                | Pulse width of RESET                                                                                                                                                               | $BV_{DD} = 3V$ | 40  |     |     | ns |

|                                                                | Dulas width of DD high time                                                                                                                                                        | $BV_{DD} = 5V$ | 30  |     |     | ns |

| t <sub>W5</sub>                                                | Pulse width of RD high time                                                                                                                                                        | $BV_{DD} = 3V$ | 40  |     |     | ns |

|                                                                | Dulas width of DD and CC both law time                                                                                                                                             | $BV_{DD} = 5V$ | 50  |     |     | ns |

| t <sub>W6</sub>                                                | Pulse width of RD and CS both low time                                                                                                                                             | $BV_{DD} = 3V$ | 70  |     |     | ns |

(1) Assured by design.

(2) All input signals are specified with rise time and fall time = 5ns (10% to 90% of  $BV_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2.

(3) See Figure 1.

(4) BYTE is asynchronous; when BYTE is 0, bits 15 to 0 appear at DB15 to DB0. When BYTE is 1, bits 15 to 8 appear on DB7 to DB0. RD may remain LOW between changes in BYTE.

(5) Only important when synchronization to clock is important.

SBAS362C-AUGUST 2006-REVISED MARCH 2008

#### www.ti.com

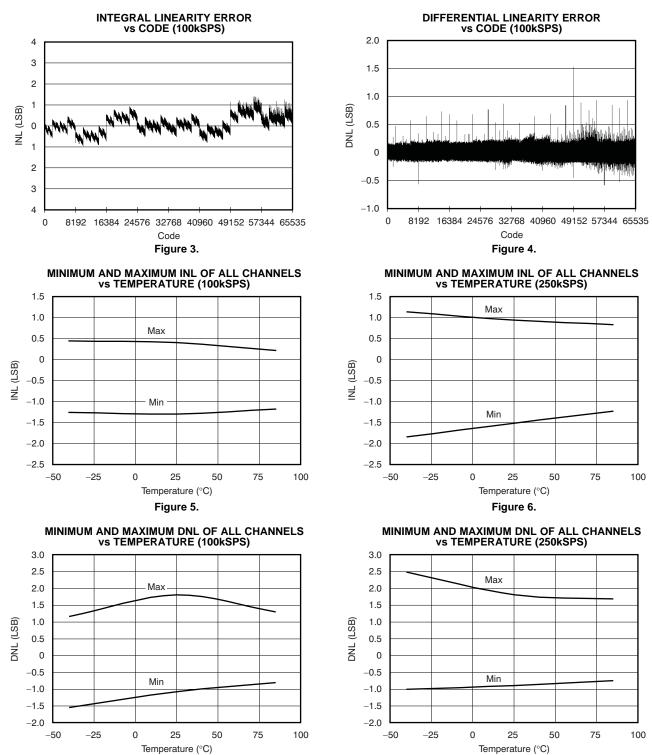

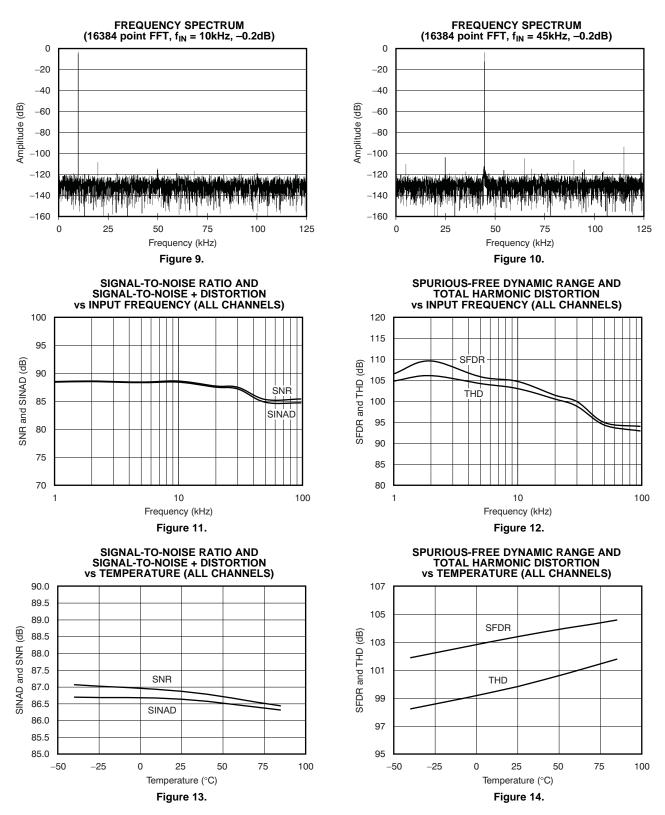

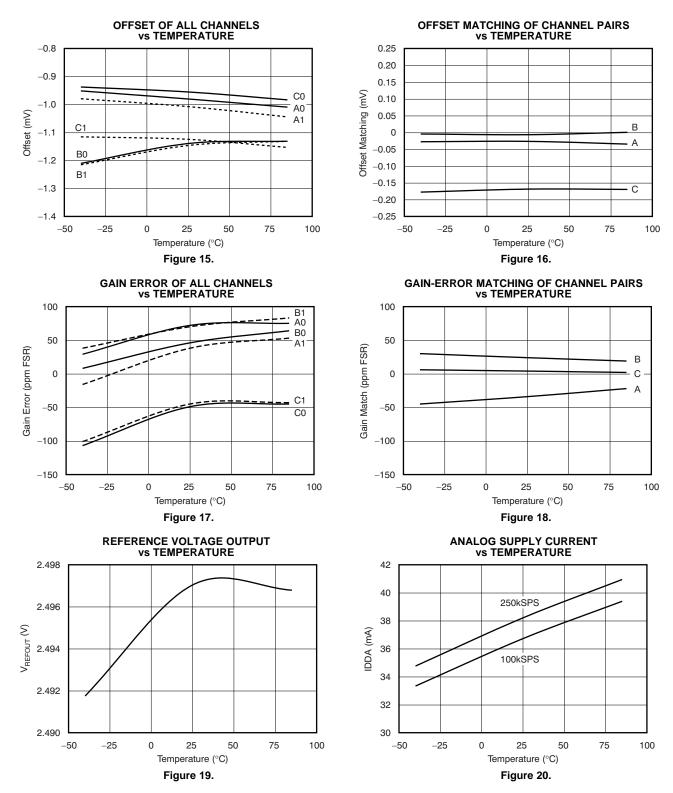

### **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = +5V$ ,  $BV_{DD} = +3V$ ,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 5MHz$ , and  $f_{SAMPLE} = 250kSPS$ , unless otherwise noted.

Figure 8.

SBAS362C-AUGUST 2006-REVISED MARCH 2008

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = +5V$ ,  $BV_{DD} = +3V$ ,  $V_{REF} = internal +2.5V$ ,  $f_{CLK} = 5MHz$ , and  $f_{SAMPLE} = 250kSPS$ , unless otherwise noted.

#### SBAS362C-AUGUST 2006-REVISED MARCH 2008

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = +5V$ ,  $BV_{DD} = +3V$ ,  $V_{REF} =$  internal +2.5V,  $f_{CLK} = 5MHz$ , and  $f_{SAMPLE} = 250kSPS$ , unless otherwise noted.

# INTRODUCTION

ADS8365 high-speed, The is а low-power, six-channel simultaneous sampling and converting, 16-bit ADC that operates from a single +5V supply. The input channels are fully differential with a typical common-mode rejection of 80dB. The ADS8365 contains six 4µs successive approximation ADCs, six differential sample-and-hold amplifiers, an internal +2.5V reference with REFIN and REFOUT pins, and a high-speed parallel interface. There are six analog inputs that are grouped into three channel pairs (A, B, and C). There are six ADCs, one for each input that can be sampled and converted simultaneously, thus preserving the relative phase information of the signals on both analog inputs. Each pair of channels has a hold signal (HOLDA, HOLDB, and HOLDC) to allow simultaneous sampling on each channel pair, on four or on all six channels. The part accepts a differential analog input voltage in the range of -V<sub>REF</sub> to +V<sub>REF</sub>, centered on the common-mode voltage (see the Analog Input section). The ADS8365 also accepts bipolar input ranges when a level shift circuit is used at the front end (see Figure 26).

A conversion is initiated on the ADS8365 by bringing the HOLDX pin low for a minimum of 20ns. HOLDX low places the sample-and-hold amplifiers of the X channels in the hold state simultaneously and the conversion process is started on each channel. The EOC output goes low for half a clock cycle when the conversion is latched into the output register. The data can be read from the parallel output bus following the conversion by bringing both RD and CS low. Conversion time for the ADS8365 is 3.2µs when a 5MHz external clock is used. The corresponding acquisition time is 0.8µs. To achieve the maximum output data rate (250kSPS), the read function can be performed during the next conversion. NOTE: This mode of operation is described in more detail in the Timing and Control section of this data sheet.

# SAMPLE AND HOLD

The sample-and-hold amplifiers on the ADS8365 allow the ADCs to accurately convert an input sine wave of full-scale amplitude to 16-bit resolution. The input bandwidth of the sample-and-hold amplifiers is greater than the Nyquist rate (Nyquist = 1/2 of the sampling rate) of the ADC, even when the ADC is operated at its maximum throughput rate of 250kSPS. typical small-signal bandwidth The of the sample-and-hold amplifiers is 10MHz. Typical aperture delay time (or the time it takes for the ADS8365 to switch from the sample to the hold mode following the negative edge of the HOLDX signal) is

5ns. The average delta of repeated aperture delay values (also known as aperture jitter) is typically 50ps. These specifications reflect the ability of the ADS8365 to capture ac input signals accurately at the exact same moment in time.

# REFERENCE

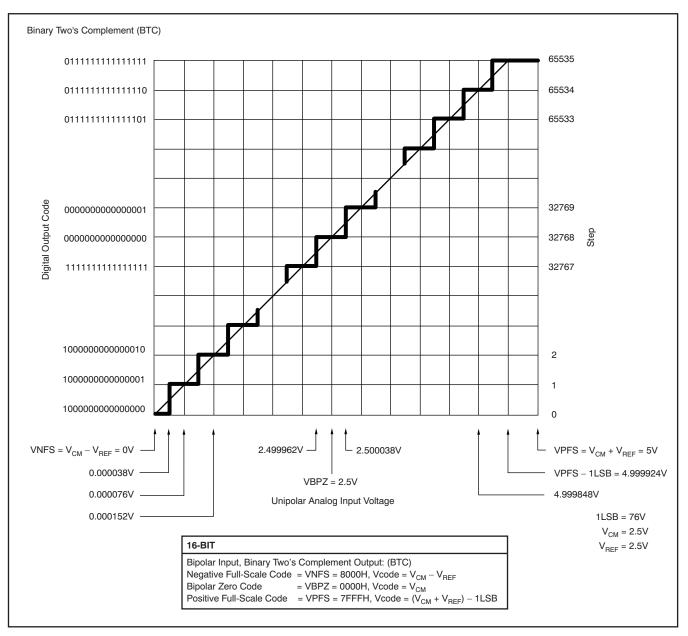

Under normal operation,  $\text{REF}_{\text{OUT}}$  (pin 61) can be directly connected to  $\text{REF}_{\text{IN}}$  (pin 62) to provide an internal +2.5V reference to the ADS8365. The ADS8365 can operate, however, with an external reference in the range of 1.5V to 2.6V, for a corresponding full-scale range of 3.0V to 5.2V, as long as the input does not exceed the AV<sub>DD</sub> + 0.3V limit.

The reference output of the ADS8365 has an impedance of  $2k\Omega$ . The high impedance reference input can be driven directly. For an external resistive load, an additional buffer is required. A load capacitance of  $0.1\mu$ F to  $10\mu$ F should be applied to the reference output to minimize noise. If an external reference is used, the three input buffers provide isolation between the external reference and the CDACs. These buffers are also used to recharge all the capacitors of all CDACs during conversion.

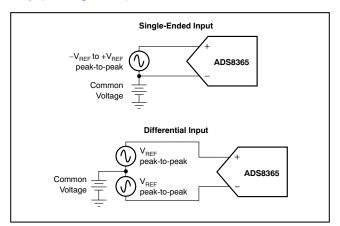

# ANALOG INPUT

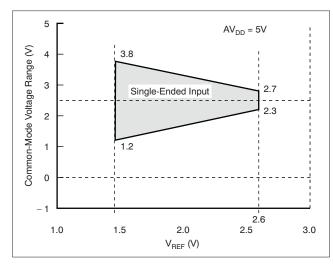

The analog input is bipolar and fully differential. There are two general methods of driving the analog input of the ADS8365: single-ended or differential, as shown in Figure 21 and Figure 22. When the input is single-ended, the –IN input is held at the common-mode voltage. The +IN input swings around the same common voltage and the peak-to-peak amplitude is the (common-mode +  $V_{REF}$ ) and the (common-mode – $V_{REF}$ ). The value of  $V_{REF}$  determines the range over which the common-mode voltage may vary (see Figure 23).

Figure 21. Methods of Driving the ADS8365 Single-Ended or Differential

# ADS8365

www.ti.com

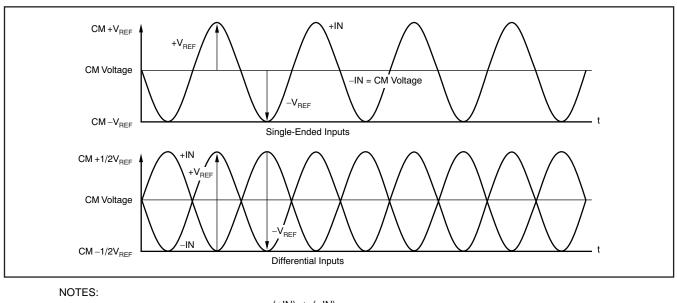

Common-mode voltage (Differential mode) =  $\frac{(+IN) + (-IN)}{2}$ . Common-mode voltage (Single-ended mode) = -IN

The maximum differential voltage between +IN and –IN of the ADS8365 is V<sub>REF</sub>. See Figure 23 and Figure 24 for a further explanation of the common voltage range for single-ended and differential inputs.

Figure 22. Using the ADS8365 in the Single-Ended and Differential Input Modes

#### Figure 23. Single-Ended Input: Common-Mode Voltage Range vs V<sub>REF</sub>

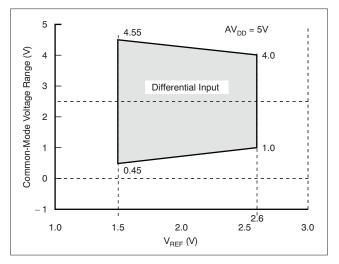

When the input is differential, the amplitude of the input is the difference between the +IN and -IN input, or: (+IN) – (-IN). The peak-to-peak amplitude of each input is  $\pm 1/2V_{REF}$  around this common voltage. However, since the inputs are  $180^{\circ}$  out-of-phase, the peak-to-peak amplitude of the differential voltage is  $+V_{REF}$  to  $-V_{REF}$ . The value of  $V_{REF}$  also determines the range of the voltage that may be common to both inputs, as shown in Figure 24.

#### Figure 24. Differential Input: Common-Mode Voltage Range vs V<sub>REF</sub>

In each case, care should be taken to ensure that the output impedance of the sources driving the +IN and -IN inputs are matched. Often, a small capacitor (20pF) between the positive and negative input helps to match the impedance. Otherwise, a mismatch may result in offset error, which will change with both temperature and input voltage.

The input current on the analog inputs depends on a number of factors, such as sample rate or input

#### SBAS362C-AUGUST 2006-REVISED MARCH 2008

voltage. Essentially, the current into the ADS8365 charges the internal capacitor array during the sampling period. After this capacitance has been fully charged, there is no further input current. The source of the analog input voltage must be able to charge the input capacitance (25pF) to a 16-bit settling level within three clock cycles if the minimum acquisition time is used. When the converter goes into the hold mode, the input impedance is greater than 1G $\Omega$ . Care must be taken regarding the absolute analog input voltage. The +IN and -IN inputs should always remain within the range of AGND – 0.3V to AV<sub>DD</sub> + 0.3V.

The OPA365 is a good choice for driving the analog inputs in a 5V, single-supply application.

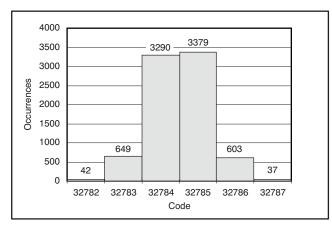

### TRANSITION NOISE

The transition noise of the ADS8365 itself is low, as shown in Figure 25 These histograms were generated by applying a low-noise dc input and initiating 8000 conversions. The digital output of the ADC will vary in output code due to the internal noise of the ADS8365; this feature is true for all 16-bit, successive approximation register (SAR) type ADCs. Using a histogram to plot the output codes, the distribution should appear bell-shaped, with the peak of the bell curve representing the nominal code for the input value. The  $\pm 1\sigma$ ,  $\pm 2\sigma$ , and  $\pm 3\sigma$  distributions represent the 68.3%, 95.5%, and 99.7%, respectively, of all codes. The transition noise can be calculated by dividing the number of codes measured by 6, yielding the  $\pm 3\sigma$  distribution, or 99.7%, of all codes. Statistically, up to three codes could fall outside the distribution when executing 1000 conversions. Remember, in order to achieve this low-noise performance, the peak-to-peak noise of the input signal and reference must be  $< 50 \mu V$ .

Figure 25. 8000 Conversion Histogram of a DC Input

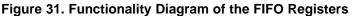

#### **BIPOLAR INPUTS**

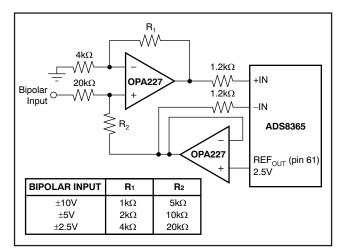

The differential inputs of the ADS8365 were designed to accept bipolar inputs ( $-V_{REF}$  and  $+V_{REF}$ ) around the common-mode voltage (2.5V), which corresponds to a 0V to 5V input range with a 2.5V reference. By using a simple op amp circuit featuring four, high-precision external resistors, the ADS8365 can be configured to accept a bipolar input range. The conventional ±2.5V, ±5V, and ±10V input ranges could be interfaced to the ADS8365 using the resistor values shown in Figure 26.

#### Figure 26. Level Shift Circuit for Bipolar Input Ranges

#### TIMING AND CONTROL

The ADS8365 uses an external clock (CLK, pin 28) that controls the conversion rate of the CDAC. With a 5MHz external clock, the ADC sampling rate is 250kSPS which corresponds to a  $4\mu$ s maximum throughput time. Acquisition and conversion take a total of 20 clock cycles.

TEXAS INSTRUMENTS

www.ti.com

SBAS362C-AUGUST 2006-REVISED MARCH 2008

# THEORY OF OPERATION

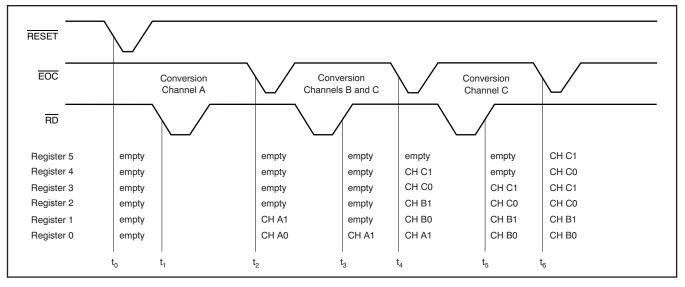

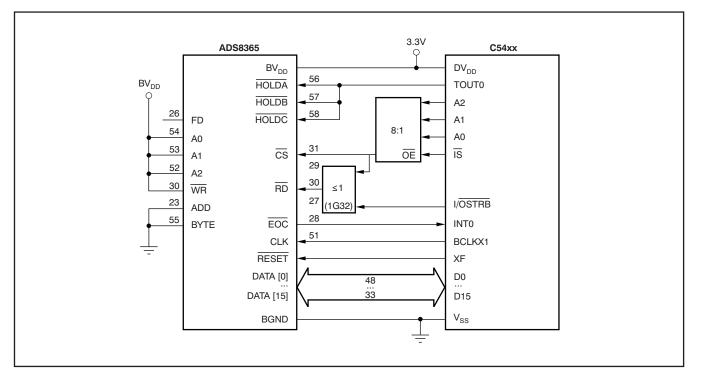

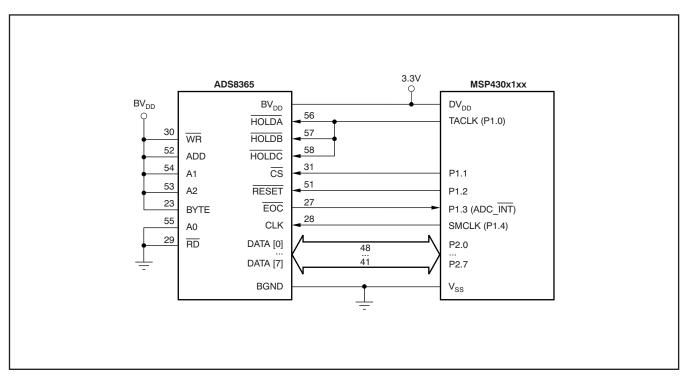

The ADS8365 contains six 16-bit ADCs that can operate simultaneously in pairs. The three hold signals (HOLDA, HOLDB, and HOLDC) initiate the conversion on the specific channels. A simultaneous hold on all six channels can occur with all three hold signals strobed together. The converted values are saved in six registers. For each read operation, the ADS8365 outputs 16 bits of information (16 data or 3 address. valid, channel data and some synchronization information). The address/mode signals (A0, A1, and A2) select how the data are read from the ADS8365. These address/mode signals can define a selection of a single channel, a cycle mode that cycles through all channels, or a FIFO mode that sequences the data determined by the order of the hold signals. The FIFO mode will allow the six registers to be used by a single-channel pair; therefore, three locations for CH X0 and three locations for CH X1 can be updated before they are read from the device.

# EXPLANATION OF CLOCK, RESET, FD, AND EOC PINS

- **Clock** An external clock has to be provided for the ADS8365. The maximum clock frequency is 5MHz. The minimum clock cycle is 200ns (see Figure 1,  $t_{C1}$ ), and the clock has to remain high (Figure 1,  $t_{W1}$ ) or low for at least 60ns.

- **RESET** Bringing the RESET signal low will reset the ADS8365. Resetting clears the control register

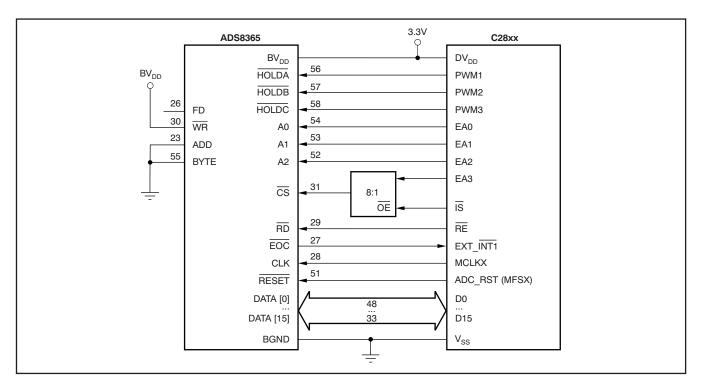

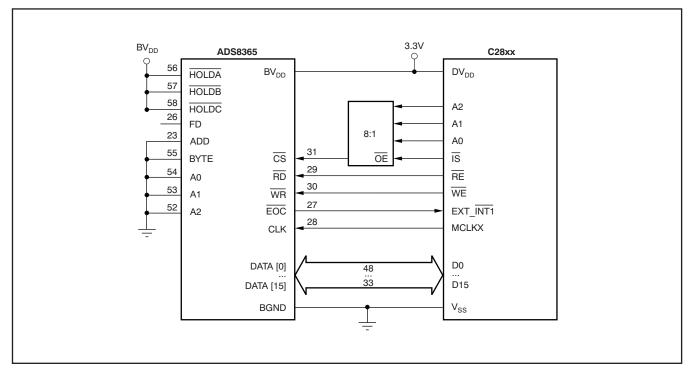

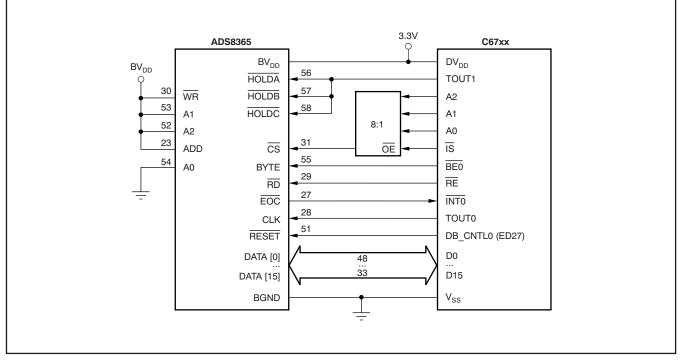

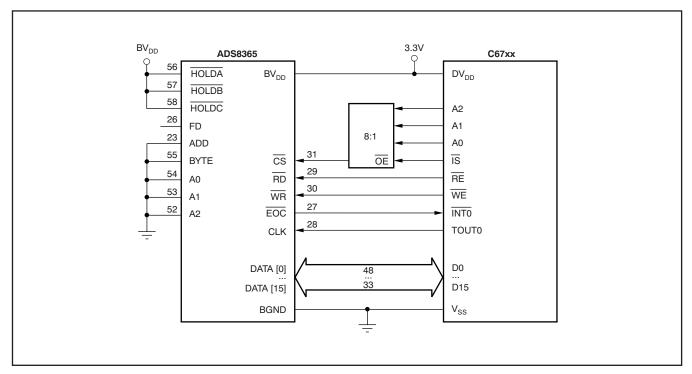

and all the output registers, aborts any conversion in process, and closes the sampling switches. The reset signal must stay low for at least 20ns (see Figure 27,  $t_{W4}$ ). The reset signal should be back high for at least 20ns (Figure 27,  $t_{D2}$ ) before starting the next conversion (negative hold edge).