SBAS249B - DECEMBER 2001 - REVISED NOVEMBER 2007

# 16-Bit, Voltage Output, Serial Input DIGITAL-TO-ANALOG CONVERTER

### **FEATURES**

- LOW POWER: 150mW MAXIMUM

- +10V INTERNAL REFERENCE

- UNIPOLAR OR BIPOLAR OPERATION

- $\bullet$  SETTLING TIME: 5µs to ±0.003% FSR

- 16-BIT MONOTONICITY, -40°C TO +85°C

- ±10V, ±5V, OR +10V CONFIGURABLE VOLTAGE OUTPUT

- RESET TO ZERO OR MID-SCALE

- DOUBLE-BUFFERED DATA INPUT

- DAISY-CHAIN FEATURE FOR MULTIPLE DAC7731s ON A SINGLE BUS

- SMALL SSOP-24 PACKAGE

### APPLICATIONS

- PROCESS CONTROL

- ATE PIN ELECTRONICS

- CLOSED-LOOP SERVO CONTROL

- MOTOR CONTROL

- DATA ACQUISITION SYSTEMS

### DESCRIPTION

The DAC7731 is a 16-bit Digital-to-Analog Converter (DAC) which provides 16 bits of monotonic performance over the specified operating temperature range and offers a +10V internal reference. Designed for automatic test equipment and industrial process control applications, the DAC7731 output swing can be configured in a  $\pm$ 10V,  $\pm$ 5V, or +10V range. The flexibility of the output configuration allows the DAC7731 to provide both unipolar and bipolar operation by pin strapping. The DAC7731 includes a high-speed output amplifier with a maximum settling time of 5µs to  $\pm$ 0.003% FSR for a 20V full-scale change and only consumes 100mW (typical) of power.

The DAC7731 features a standard 3-wire, SPI-compatible serial interface with double buffering to allow asynchronous updates of the analog output as well as a serial data output line for daisy-chaining multiple DAC7731s. A user programmable reset control forces the DAC output to either min-scale  $(0000_h)$  or mid-scale  $(8000_h)$ , overriding both the input and DAC register values. The DAC7731 is available in a SSOP-24 package and three performance grades specified to operate from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| V <sub>CC</sub> to V <sub>SS</sub> | -0.3V to +32V                   |

|------------------------------------|---------------------------------|

| V <sub>CC</sub> to AGND            | –0.3V to +16V                   |

| V <sub>SS</sub> to AGND            | 16V to +0.3V                    |

| AGND to DGND                       |                                 |

| REF <sub>IN</sub> to AGND          | $\dots 0V$ to $V_{CC} - 1.4V$   |

| V <sub>DD</sub> to DGND            | –0.3V to +6V                    |

| Digital Input Voltage to DGND      | 0.3V to V <sub>DD</sub> + 0.3V  |

| Digital Output Voltage to DGND     | –0.3V to V <sub>DD</sub> + 0.3V |

| Operating Temperature Range        | –40°C to +85°C                  |

| Storage Temperature Range          | 65°C to +150°C                  |

| Junction Temperature (TJ Max)      | +150°C                          |

|                                    |                                 |

NOTE: (1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT   | JCT PACKAGE-LEAD PACKAGE |    | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(2)</sup> | TRANSPORT<br>MEDIA, QUANTITY |

|-----------|--------------------------|----|-----------------------------------|--------------------|-----------------------------------|------------------------------|

| DAC7731E  | SSOP-24                  | DB | –40°C to +85°C                    | DAC7731E           | DAC7731E                          | Rails, 60                    |

| "         | "                        | "  | "                                 | "                  | DAC7731E/1K                       | Tape and Reel,1000           |

| DAC7731EB | SSOP-24                  | DB | –40°C to +85°C                    | DAC7731EB          | DAC7731EB                         | Rails, 60                    |

| "         | "                        | "  | "                                 | "                  | DAC7731EB/1K                      | Tape and Reel, 1000          |

| DAC7731EC | SSOP-24                  | DB | –40°C to +85°C                    | DAC7731EC          | DAC7731EC                         | Rails, 60                    |

| "         | "                        | "  | "                                 | "                  | DAC7731EC/1K                      | Tape and Reel, 1000          |

NOTE: (1) For the most current package ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI web site at www.ti.com.

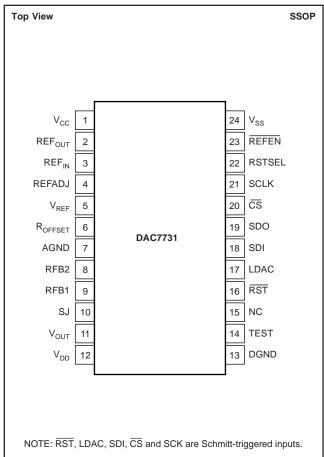

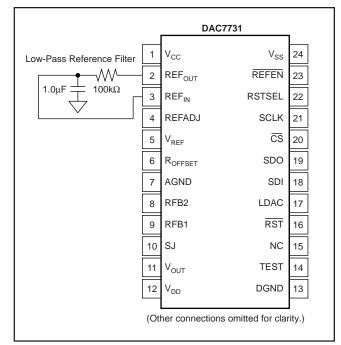

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN | NAME                | DESCRIPTION                                                           |

|-----|---------------------|-----------------------------------------------------------------------|

| 1   | V <sub>cc</sub>     | Positive Analog Power Supply                                          |

| 2   | REFOUT              | Internal Reference Output                                             |

| 3   | REFIN               | Reference Input                                                       |

| 4   | REFADJ              | Internal Reference Trim. (Acts as a gain adjustment                   |

|     |                     | input when the internal reference is used.)                           |

| 5   | V <sub>REF</sub>    | Buffered Output from REF <sub>IN</sub> , can be used to drive         |

|     |                     | external devices. Internally, this pin directly drives the            |

|     |                     | DAC's circuitry                                                       |

| 6   | R <sub>OFFSET</sub> | Offsetting Resistor                                                   |

| 7   | AGND                | Analog ground                                                         |

| 8   | RFB2                | Feedback Resistor 2, used to configure DAC output                     |

|     |                     | range.                                                                |

| 9   | RFB1                | Feedback Resistor 1, used to configure DAC output                     |

|     |                     | range.                                                                |

| 10  | SJ                  | Summing Junction of the Output Amplifier                              |

| 11  | V <sub>OUT</sub>    | DAC Voltage Output                                                    |

| 12  | V <sub>DD</sub>     | Digital Power Supply                                                  |

| 13  | DGND                | Digital Ground                                                        |

| 14  | TEST                | Reserved, Connect to DGND                                             |

| 15  | NC                  | No Connection                                                         |

| 16  | RST                 | V <sub>OUT</sub> reset; active LOW, depending on the state of         |

|     |                     | RSTSEL, the DAC register is either reset to mid-                      |

|     |                     | scale or min-scale.                                                   |

| 17  | LDAC                | DAC register load control, rising dege triggered. Data                |

|     |                     | is loaded from the input register to the DAC register.                |

| 18  | SDI                 | Serial Data Input. Data is latched into the input                     |

|     |                     | register on the rising edge of SCLK.                                  |

| 19  | SDO                 | Serial Data Output, delayed 16 SCLK clock cycles.                     |

| 20  | CS                  | Chip Select, Active LOW                                               |

| 21  | SCLK                | Serial Clock Input                                                    |

| 22  | RSTSEL              | Reset Select; determines the action of RST. If HIGH,                  |

|     |                     | RST will reset the DAC register to mid-scale. If LOW,                 |

| 23  | REFEN               | RST will reset the DAC register to min-scale.                         |

| 23  | REFEN               | Enables internal +10V reference (REF <sub>OUT</sub> ), active<br>LOW. |

| 24  | V <sub>SS</sub>     | LOW.<br>Negative Analog Power Supply                                  |

| 27  | V SS                | regarive / maiog r ower ouppry                                        |

# **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = +15V$ ,  $V_{SS} = -15V$ ,  $V_{DD} = +5V$ , Internal refi/ence enabled, unless otherwise noted.

|                                                                                                                                                               |                                                                                                                                         |                                    | DAC7731                         |                                   | C     | AC7731E       | В             |         | DAC7731E     | с          |                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|-----------------------------------|-------|---------------|---------------|---------|--------------|------------|--------------------------------|

| PARAMETER                                                                                                                                                     | CONDITIONS                                                                                                                              | MIN                                | ТҮР                             | MAX                               | MIN   | ТҮР           | MAX           | MIN     | ТҮР          | MAX        | UNITS                          |

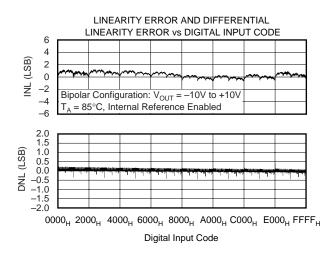

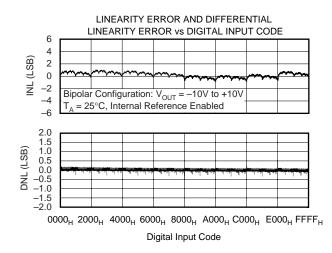

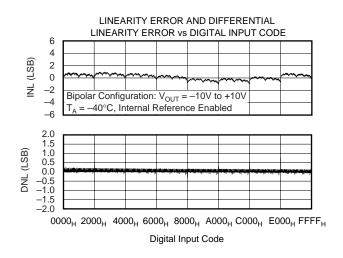

| ACCURACY<br>Linearity Error (INL)                                                                                                                             | T <sub>A</sub> = 25°C                                                                                                                   |                                    |                                 | ±6<br>±5                          |       |               | ±4<br>±3      |         |              | ±3<br>±2   | LSB<br>LSB                     |

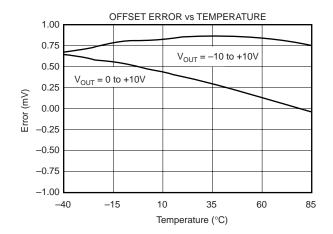

| Differential Linearity Error (DNL)<br>Monotonicity<br>Offset Error                                                                                            |                                                                                                                                         | 14                                 |                                 | ±4<br>±0.1                        | 15    |               | ±2<br>*       | 16      |              | ±1<br>*    | LSB<br>Bits<br>% of FSR        |

| Offset Error Drift<br>Gain Error                                                                                                                              | With Internal REF<br>With External REF                                                                                                  |                                    | ±2                              | ±0.4<br>±0.25                     |       | *             | ±0.25<br>±0.1 |         | *            | ±0.15<br>* | ppm/°C<br>% of FSF<br>% of FSF |

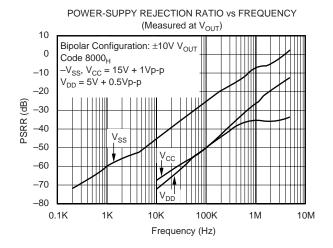

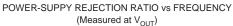

| Gain Error Drift<br>PSRR (V <sub>CC</sub> or V <sub>SS</sub> )                                                                                                | With Internal REF<br>At Full-Scale                                                                                                      |                                    | ±15<br>50                       | 200                               |       | ±10<br>*      | *             |         | ±7<br>*      | *          | ppm/°C<br>ppm/V                |

| ANALOG OUTPUT <sup>(1)</sup><br>Voltage Output <sup>(2)</sup>                                                                                                 | +11.4/–4.75<br>+11.4/–11.4<br>+11.4/–6.4                                                                                                |                                    | 0 to 10<br>±10<br>±5            |                                   |       | * * *         |               |         | *<br>*<br>*  |            | V<br>V<br>V                    |

| Output Current<br>Output Impeadance<br>Maximum Load Capacitance<br>Short-Circuit Current<br>Short-Circuit Duration                                            | AGND                                                                                                                                    | ±5                                 | 0.1<br>200<br>±15<br>Indefinite |                                   | *     | * * *         |               | *       | *<br>*<br>*  |            | mA<br>Ω<br>pF<br>mA            |

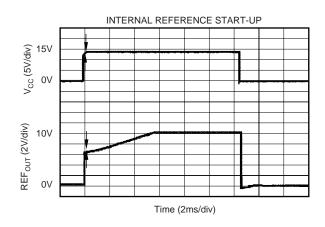

| REFERENCE<br>Reference Output<br>REF <sub>OUT</sub> Impedance<br>REF <sub>OUT</sub> Voltage Drift                                                             |                                                                                                                                         | 9.96                               | 10<br>400<br>±15                | 10.04                             | 9.975 | *<br>*<br>±10 | 10.025        | *       | *<br>*<br>±7 | *          | V<br>Ω<br>ppm/°C               |

| REF <sub>OUT</sub> Voltage Adjustment <sup>(3)</sup><br>REF <sub>IN</sub> Input Range <sup>(4)</sup><br>REF <sub>IN</sub> Input Current<br>REFADJ Input Range | Absolute Max Value that                                                                                                                 | ±25<br>4.75<br>0                   | 10                              | V <sub>CC</sub> - 1.4<br>10       | * *   | *             | *             | * *     | *            | *          | mV<br>V<br>nA<br>V             |

| REFADJ Input Impedance<br>V <sub>REF</sub> Output Current<br>V <sub>REF</sub> Impedance                                                                       | can be applied is $V_{CC}$                                                                                                              | -2                                 | 50<br>1                         | +2                                | *     | *             | *             | *       | *            | *          | kΩ<br>mA<br>Ω                  |

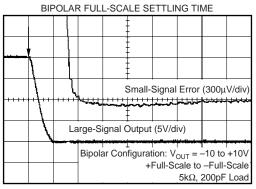

| DYNAMIC PERFORMANCE<br>Settling Time to ±0.003%                                                                                                               | 20V Output Step<br>$R_L = 5k\Omega$ , $C_L = 200pF$ ,<br>with external REF <sub>OUT</sub><br>to REF <sub>IN</sub> filter <sup>(5)</sup> |                                    | 3                               | 5                                 |       | *             | *             |         | *            | *          | μs                             |

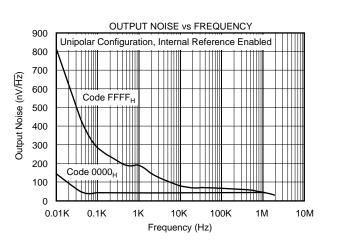

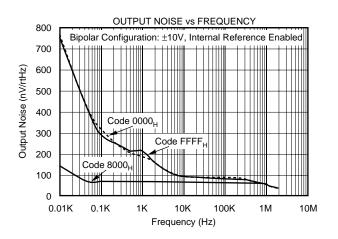

| Digital Feedthrough<br>Output Noise Voltage                                                                                                                   | at 10kHz                                                                                                                                |                                    | 2<br>100                        |                                   |       | *             |               |         | *            |            | nV-s<br>nV/√Hz                 |

| DIGITAL INPUT<br>V <sub>IH</sub><br>V <sub>IL</sub>                                                                                                           | I <sub>H</sub>   < 10μΑ<br> I <sub>L</sub>   < 10μΑ                                                                                     | 0.7 • V <sub>DD</sub>              |                                 | 0.3 • V <sub>DD</sub>             | *     |               | *             | *       |              | *          | V<br>V                         |

| DIGITAL OUTPUT<br>V <sub>OH</sub><br>V <sub>OL</sub>                                                                                                          | I <sub>OH</sub> = -0.8mA<br>I <sub>OL</sub> = 1.6mA                                                                                     | 3.6                                |                                 | 0.4                               | *     |               | *             | *       |              | *          | V<br>V                         |

| POWER SUPPLY                                                                                                                                                  |                                                                                                                                         |                                    |                                 |                                   |       |               |               |         |              |            |                                |

| V <sub>DD</sub><br>V <sub>CC</sub><br>V <sub>SS</sub>                                                                                                         | Bipolar Operation<br>Unipolar Opeation                                                                                                  | +4.75<br>+11.4<br>-15.75<br>-15.75 | +5.0                            | +5.25<br>+15.75<br>-11.4<br>-4.75 | * * * | *             | * * *         | * * * * | *            | * * *      |                                |

| I <sub>DD</sub><br>I <sub>CC</sub><br>I <sub>SS</sub><br>Power                                                                                                | Unloaded<br>Unloaded<br>No Load, Ext. Reference                                                                                         | -4                                 | 100<br>4<br>-2.5<br>85          | 6                                 | *     | * * * *       | *             | *       | * * * *      | *          | μA<br>mA<br>mA<br>mW           |

| TEMPERATURE RANGE<br>Specified Performance                                                                                                                    | No Load, Int. Reference                                                                                                                 | -40                                | 100                             | 150<br>+85                        | *     | *             | *             | *       | *            | *          | mW<br>°C                       |

\* Specifications same as grade to the left.

NOTES: (1) With minimum  $V_{CC}\!/V_{SS}$  requirements, internal reference enabled.

(2) Please refer to the Theory of Operation section for more information with respect to output voltage configurations.

(3) See Figure 11 for gain and offset adjustment connection diagrams when using the internal reference.

(4) The minimum value for REF<sub>IN</sub> must be equal to the greater of V<sub>SS</sub> +14V and +4.75V, where +4.75V is the minimum voltage allowed.

(5) Reference low-pass filter values:  $100k\Omega$ ,  $1.0\mu$ F (see Figure 14).

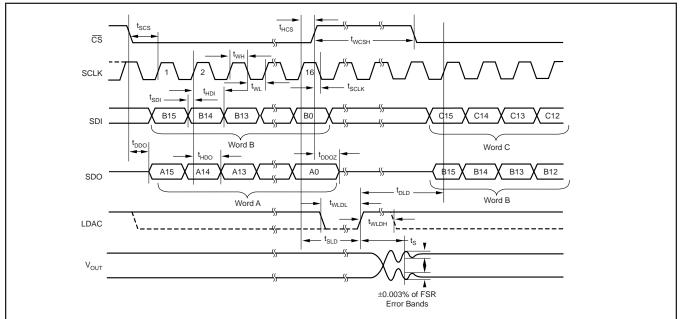

# TIMING CHARACTERISTICS

$V_{CC}$  = +15V,  $V_{SS}$  = -15V,  $V_{DD}$  = 5V;  $R_L$  = 2k $\Omega$  to AGND;  $C_L$  = 200pF to AGND; all specifications -40°C to +85°C, unless otherwise noted.

|                   |                                                                                          |     | DAC7731 |     |       |

|-------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|

| PARAMETER         | DESCRIPTION                                                                              | MIN | ТҮР     | MAX | UNITS |

| t <sub>WH</sub>   | SCLK HIGH Time                                                                           | 25  |         |     | ns    |

| t <sub>WL</sub>   | SCLK LOW Time                                                                            | 25  |         |     | ns    |

| t <sub>SDI</sub>  | Setup Time: Data in valid before rising SCLK                                             | 5   |         |     | ns    |

| t <sub>HDI</sub>  | Hold Time: Data in valid after rising SCLK                                               | 20  |         |     | ns    |

| t <sub>SCS</sub>  | Setup Time: CS falling edge before first rising SCLK                                     | 15  |         |     | ns    |

| t <sub>HSC</sub>  | Hold Time: CS rising edge after 16th rising SCLK                                         | 0   |         |     | ns    |

| t <sub>DDO</sub>  | Delay Time: $\overline{CS}$ Falling Edge to Data Out valid, C <sub>L</sub> = 20pF on SDO | 50  |         |     | ns    |

| t <sub>HDO</sub>  | Hold Time: Data Out valid after SCLK rising edge, CL 20pF on SDO                         | 50  |         |     | ns    |

| t <sub>DDOZ</sub> | Delay Time: CS rising edge to SDO = High Impedance                                       |     |         | 70  | ns    |

| t <sub>WCSH</sub> | CS HIGH Time                                                                             | 50  |         |     | ns    |

| t <sub>WLDL</sub> | LDAC LOW Time                                                                            | 20  |         |     | ns    |

| t <sub>WLDH</sub> | LDAC HIGH Time                                                                           | 20  |         |     | ns    |

| t <sub>SLD</sub>  | Setup Time: 16th Rising SCLK Before LDAC Rising Edge                                     | 15  |         |     | ns    |

| t <sub>DLD</sub>  | Delay Time: LDAC rising edge to first SCLK rising edge of next                           | 15  |         |     | ns    |

|                   | transfer cycle.                                                                          |     |         |     |       |

| t <sub>SCLK</sub> | Setup Time: CS High before falling SCLK edge following 16th                              | 5   |         |     | ns    |

|                   | rising SCLK edge                                                                         |     |         |     |       |

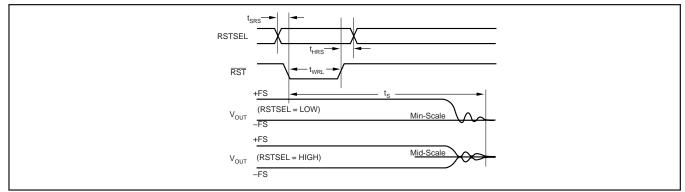

| t <sub>SRS</sub>  | Setup Time: RSTSEL Valid Before RST LOW                                                  | 0   |         |     | ns    |

| t <sub>HRS</sub>  | Hold Time: RSTSEL valid after RST HIGH                                                   | 20  |         |     | ns    |

| t <sub>WRL</sub>  | RST LOW Time                                                                             | 30  |         | -   | ns    |

| ts                | DAC V <sub>OUT</sub> Settling Time                                                       |     |         | 5   | μs    |

#### **INTERFACE TIMING**

#### **RESET TIMING**

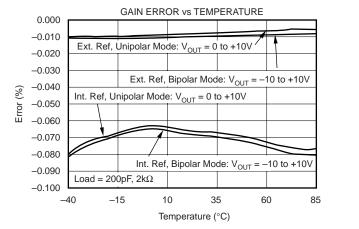

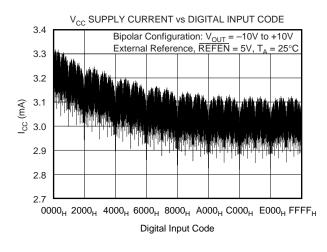

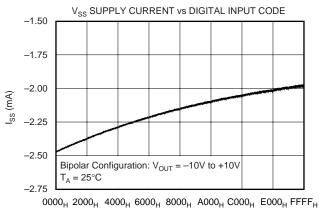

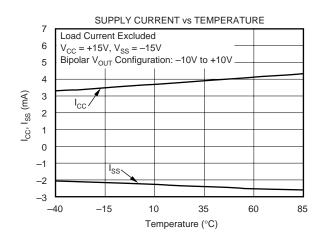

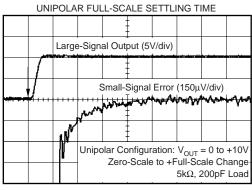

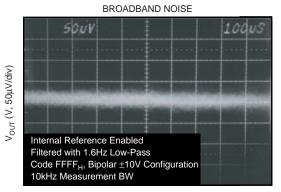

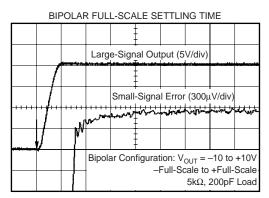

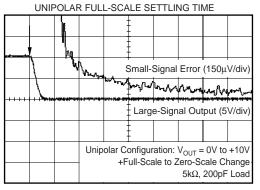

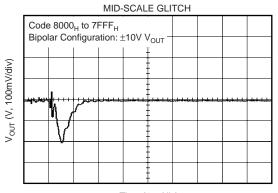

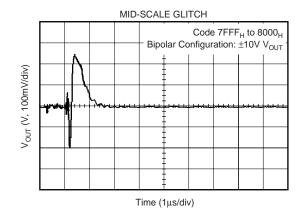

# TYPICAL CHARACTERISTICS

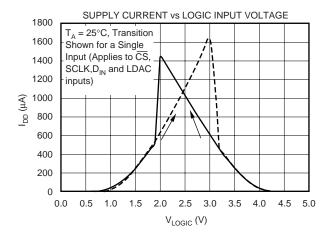

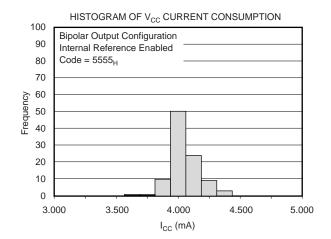

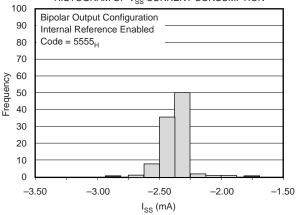

$T_A$  = +25°C (unless otherwise noted).

V<sub>CC</sub> SUPPLY CURRENT vs DIGITAL INPUT CODE 4.4 4.3 4.2 4.1 4.0 4.0 3.9 3.8 3.7 0000<sub>H</sub> 2000<sub>H</sub> 4000<sub>H</sub> 6000<sub>H</sub> 8000<sub>H</sub> A000<sub>H</sub> C000<sub>H</sub> E000<sub>H</sub> FFFF<sub>H</sub> Digital Input Code

$T_A = +25^{\circ}C$  (unless otherwise noted).

Digital Input Code

HISTOGRAM OF V<sub>SS</sub> CURRENT CONSUMPTION

$T_A = +25^{\circ}C$  (unless otherwise noted).

OUTPUT VOLTAGE vs R<sub>LOAD</sub> 12 Source 8 4 V<sub>our</sub> (V) 0 -4 Sink -8 -12 0.0 0.1 10.0 1.0 100.0  $\mathsf{R}_{\mathsf{LOAD}}\left(\mathsf{k}\Omega\right)$

$T_A = +25^{\circ}C$  (unless otherwise noted).

Time (2µs/div)

Time (100µs/div)

Time (2µs/div)

$T_{A}$  = +25°C (unless otherwise noted).

Time (2µs/div)

Time (2µs/div)

Time (1µs/div)

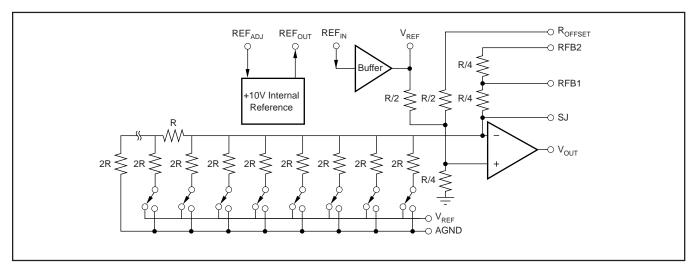

### THEORY OF OPERATION

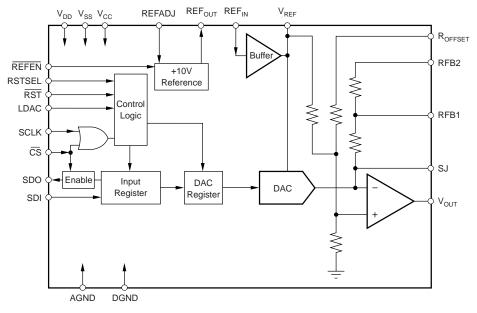

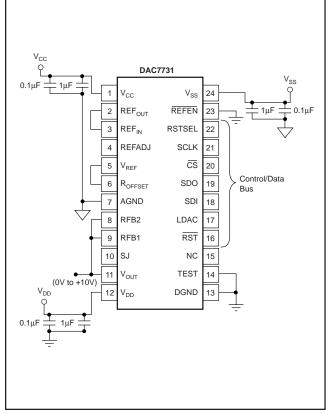

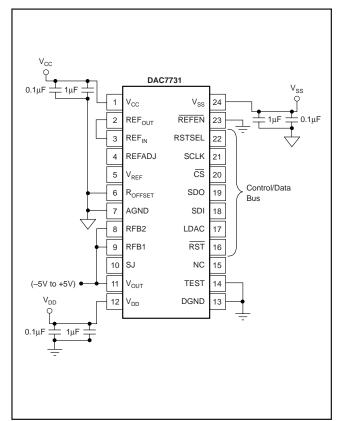

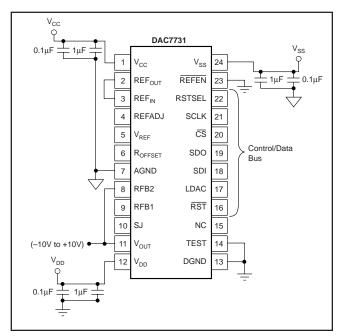

The DAC7731 is a voltage output, 16-bit DAC with a +10V built-in internal reference. The architecture is an R-2R ladder configuration with the three MSBs segmented, followed by an operational amplifier that serves as a buffer, as shown in Figure 1. The output buffer is designed to allow user-configurable output adjustments giving the DAC7731 output voltage ranges of 0V to +10V, -5V to +5V, or -10V to +10V. Please refer to Figures 2, 3, and 4 for pin configuration information.

The digital input is a serial word made up of the DAC code (MSB first) and is loaded into the DAC register using the LDAC input pin. The converter can be powered from  $\pm 12V$  to  $\pm 15V$  dual analog supplies and a  $\pm 5V$  logic supply. The device offers a reset function, which immediately sets the DAC output voltage and DAC register to min-scale (code  $0000_{\text{H}}$ ) or mid-scale (code  $8000_{\text{H}}$ ). The data I/O and reset functions are discussed in more detail in the following sections.

FIGURE 1. DAC7731 Architecture.

FIGURE 2. Basic Operation:  $V_{OUT} = 0V$  to +10V.

FIGURE 3. Basic Operation:  $V_{OUT} = -5V$  to +5V.

FIGURE 4. Basic Operation:  $V_{OUT} = -10V$  to +10V.

#### ANALOG OUTPUTS

The output amplifier can swing to within 1.4V of the supply rails, specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range. This allows for a  $\pm 10$ V DAC voltage output operation from  $\pm 12$ V supplies with a typical 5% tolerance.

When the DAC7731 is configured for a unipolar, 0V to 10V output, a negative voltage supply is required. This is due to internal biasing of the output stage. Please refer to the Electrical Characteristics table (see page 3) for more information.

The minimum and maximum voltage output values are dependent upon the output configuration implemented and reference voltage applied to the DAC7731. Please note that  $V_{SS}$  (the negative power supply) must be in the range of -4.75V to -15.75V for unipolar operation. The voltage on  $V_{SS}$  sets several bias points within the converter and is required in all modes of operation. If  $V_{SS}$  is not in one of these two configurations, the bias values may be in error and proper operation of the device is not ensured.

Supply sequence is important in establishing the correct startup of the DAC. The following supply sequence must be followed:  $V_{SS}$  (device substrate) first, then  $V_{DD}$  followed by  $V_{CC}$ . In addition, each supply must reach the values specified in the Electrical Characteristics table (see page 3) within 100ms of its ramp start.

#### **REFERENCE INPUTS**

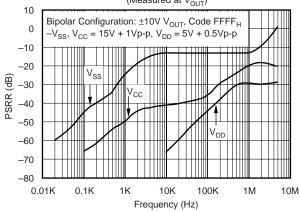

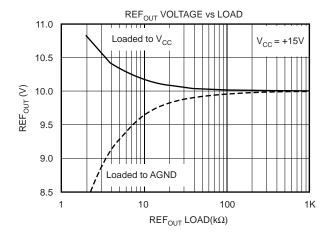

The DAC7731 provides a built-in +10V voltage reference and on-chip buffer to allow external component reference drive. To use the internal reference, REFEN must be LOW, enabling the reference circuitry of the DAC7731 (as shown in Table I) and the REF<sub>OUT</sub> pin must be connected to REF<sub>IN</sub>. This is the input to the on-chip reference buffer. The buffer output is provided at the V<sub>REF</sub> pin. In this configuration, V<sub>REF</sub> is used to setup the

DAC7731 output amplifier into one of three voltage output modes as discussed earlier.  $V_{REF}$  can also be used to drive other system components requiring an external reference.

| REFEN | ACTION                                                              |

|-------|---------------------------------------------------------------------|

| 1     | Internal Reference disabled;<br>REF <sub>OUT</sub> = High Impedance |

| 0     | Internal Reference enabled;<br>REF <sub>OUT</sub> = +10V            |

TABLE I. REFEN Action.

The internal reference of the DAC7731 can be disabled when use of an external reference is desired. When using an external reference, the reference input,  $\text{REF}_{\text{IN}}$ , can be any voltage between 4.75V (or V<sub>SS</sub> + 14V, whichever is greater) and V<sub>CC</sub> - 1.4V.

#### **DIGITAL INTERFACE**

Table II shows the input data format for the DAC7731 and Table III illustrates the basic control logic of the device. The serial interface consists of a chip select input ( $\overline{CS}$ ), serial data clock input (SCLK), serial data input (SDI), serial data output (SDO), and load control input (LDAC). An asynchronous reset input ( $\overline{RST}$ ), which is active LOW, is provided to simplify start-up conditions, periodic resets, or emergency resets to a known state, depending on the status of the reset select (RSTSEL) signal. Please refer to the *DAC Reset* section for additional information regarding the reset operation.

|               | ANALOG                               | OUTPUT                                                  |

|---------------|--------------------------------------|---------------------------------------------------------|

| DIGITAL INPUT | Unipolar Configuration               | Bipolar Configuration                                   |

|               | Unipolar Straight Binary             | Bipolar Offset Binary                                   |

| 0x0000        | Zero (0V)                            | –Full-Scale (–V <sub>REF</sub> or –V <sub>REF</sub> /2) |

| 0x0001        | Zero + 1LSB                          | -Full-Scale + 1LSB                                      |

| :             | :                                    | :                                                       |

| 0x8000        | 1/2 Full-Scale                       | Bipolar Zero                                            |

| 0x8001        | 1/2 Full-Scale + 1LSB                | Bipolar Zero + 1LSB                                     |

| :             | :                                    | :                                                       |

| 0xFFFF        | Full-Scale (V <sub>REF</sub> – 1LSB) | +Full-Scale (+V <sub>REF</sub> – 1LSB                   |

|               |                                      | or +V <sub>REF</sub> /2 – 1LSB)                         |

TABLE II. DAC7731 Data Format.

|                                                                                                                                                                                   | CC        | NTROL S | STATU | S                                                                                               | COMMAND                                                |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| ĊŚ                                                                                                                                                                                | RST       | RSTSEL  | LDAC  | SCLK                                                                                            | ACTION                                                 |  |  |  |  |

| н                                                                                                                                                                                 | н         | Х       | Х     | Х                                                                                               | Shift Register is disabled on the serial bus.          |  |  |  |  |

| L                                                                                                                                                                                 | . н х х х |         | x     | Enable SDO pin from High Impedance;<br>enables shift operation and I/O bus<br>(SCLK, SDI, SDO). |                                                        |  |  |  |  |

| L                                                                                                                                                                                 | н         | Х       | Х     | $\rightarrow$                                                                                   | Serial Data Shifted into Input Register                |  |  |  |  |

| Ŷ                                                                                                                                                                                 | н         | Х       | Х     | L                                                                                               | Serial Data Shifted into Input Register <sup>(1)</sup> |  |  |  |  |

| Х                                                                                                                                                                                 | н         | Х       | Ŷ     | Х                                                                                               | Data in Input Register is Loaded into DAC Register.    |  |  |  |  |

| Х                                                                                                                                                                                 | L         | Н       | Х     | Х                                                                                               | Resets Input and DAC Registers to mid-scale.           |  |  |  |  |

| Х                                                                                                                                                                                 | L         | L       | Х     | Х                                                                                               | Resets Input and DAC Registers to min-scale.           |  |  |  |  |

| NOTE: (1) In order to avoid unwanted shifting of the input register by an additional bit, care must be taken that a rising edge on $\overline{CS}$ only occurs when SCLK is HIGH. |           |         |       |                                                                                                 |                                                        |  |  |  |  |

TABLE III. DAC7731 Logic Truth Table.

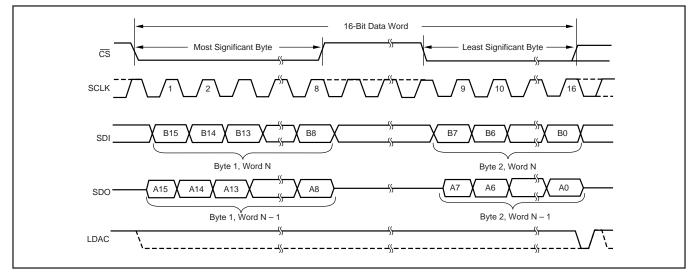

The DAC code is provided via a 16-bit serial interface, as shown in Table II. The digital input word makes up the digital code to be loaded into the data input register of the device. A typical data transfer and DAC output update take place as follows: Once  $\overline{CS}$  is active (LOW), the DAC7731 is enabled on the serial bus and the 16-bit serial data transfer can begin. The serial data is shifted into the device on each rising SCLK edge until all 16 bits are transferred (1 bit per 1 rising SCLK edge). Once received, the data in the input register is loaded into the DAC register upon reception of a rising edge on the LDAC input (load command). This action updates the analog output,  $V_{OUT}$ , to the desired voltage specified by the digital input word. A rising edge on LDAC is completely asynchronous to the serial interface of the device and can occur at any time. Care must be taken to ensure that the entire 16 bits of data are loaded into the input register before issuing a LDAC active edge. Additional load commands will have no effect on the DAC output if the data in the input register is unchanged between rising LDAC edges. When CS is returned HIGH, the rising edge on  $\overline{CS}$  must occur when SCLK is HIGH. Application of a rising  $\overline{CS}$  edge when SCLK is LOW will cause one additional shift in the serial input shift register, corrupting the desired input data.

#### TIMING CONSIDERATIONS

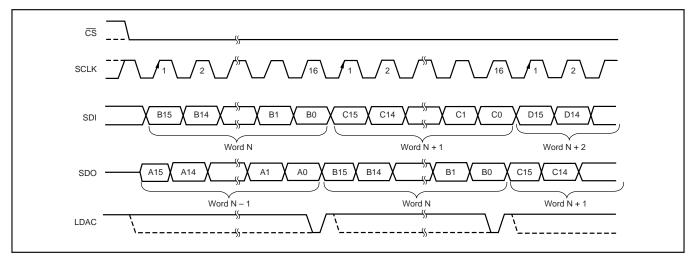

The flexible interface of the DAC7731 can operate under a number of different scenarios as is required by a host controller. Critical timing for a 16-bit data transfer cycle is shown in the Interface Timing section of the Timing Characteristics. While this is the most common method of writing to the DAC7731, the device accepts two additional modes of data transfer from the host. These are byte transfer mode and continuous transfer mode.

Byte transfer mode is especially useful when an 8-bit host is communicating with the DAC. Data transfer can occur without requiring an additional general purpose I/O pin to control the  $\overline{CS}$  input of the DAC in cycles of 16 clocks. A HIGH state on  $\overline{CS}$  stops data from coming into and out of the internal shift register. This provides byte-wide support for 8-bit host processors. Figure 5 is an example of the timing cycle of such a data transfer.

The remaining data transfer mode accepted by the DAC7731 is continuous transfer. The  $\overline{CS}$  of the DAC7731 can be tied LOW or held LOW by the controller for an indefinite number of serial clock cycles. Each clock cycle will transfer data into the

FIGURE 5. Byte-Wide Data Write Cycle.

FIGURE 6. Continuous Transfer Control.

DAC via SDI and out of the DAC on SDO. Care must be taken that the LDAC signal to the DAC(s) is timed correctly so that valid data is transferred into the DAC register on each rising LDAC edge. (*Valid data* refers to the serial data latched on each of the 16 rising SCLK edges prior to the occurrence of a rising LDAC signal.) The rising edge of LDAC must occur before the first rising SCLK edge of the following 16-bit transfer. Figure 6 shows continuous transfer timing.

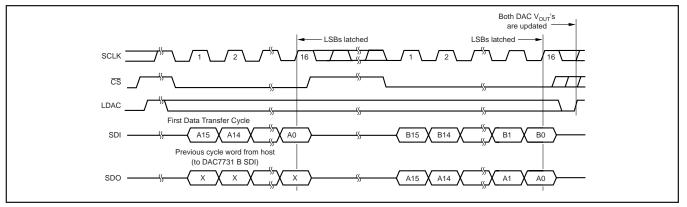

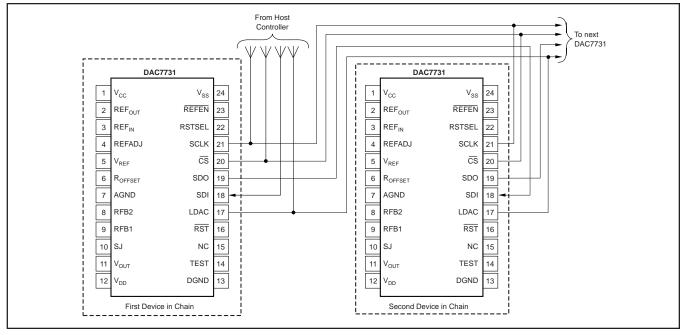

#### DAISY-CHAINING USING SDO

Multiple DAC7731s can be connected to a single serial port by attaching each of their control inputs in parallel and daisychaining the SDO and SDI I/Os of each device. The SDO output of the DAC7731 is active when  $\overline{CS}$  is LOW and can be left unconnected when not required for use in a daisychain configuration.

Once a data transfer cycle begins, new data is shifted into SDI and data currently residing in the shift register (from previous cycle, power-up, or reset command) is presented on SDO, MSB first. One data transfer cycle for each DAC7731 is required to update all devices in the chain. The first data

cycle written into the chain will arrive at the last DAC7731 on the final cycle of the data transfer. Upon completion of the required number of data transfer cycles (one cycle per device), each DAC voltage output is updated with a rising edge on the LDAC inputs. Figure 7 shows the required timing to properly update two DAC7731s in a daisy-chained configuration, as shown in Figure 8.

#### DAC RESET

The  $\overline{\text{RST}}$  and RSTSEL inputs control the reset of the analog output. The reset command is level triggered by a low signal on  $\overline{\text{RST}}$ . Once  $\overline{\text{RST}}$  is LOW, the DAC output will begin settling to the mid-scale or min-scale code depending on the state of the RSTSEL input. A HIGH value on RSTSEL will cause  $V_{OUT}$  to reset to the mid-scale code ( $8000_{\text{H}}$ ) and a LOW value will reset  $V_{OUT}$  to min-scale ( $8000_{\text{H}}$ ). A change in the state of the RSTSEL input while  $\overline{\text{RST}}$  is LOW will cause a corresponding change in the reset command selected internally and consequently change the output value of  $V_{OUT}$  of the DAC. Note that a valid reset signal also resets the input register of the DAC to the value specified by the state of RSTSEL.

FIGURE 7. DAC7731 Daisy-Chain Timing for Figure 7.

FIGURE 8. DAC7731 Daisy-Chain Schematic.

### APPLICATIONS

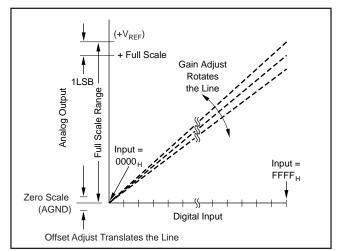

#### GAIN AND OFFSET CALIBRATION

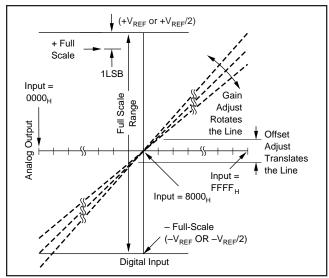

The architecture of the DAC7731 is designed in such a way as to allow for easily configurable offset and gain calibration using a minimum of external components. The DAC7731 has built-in feedback resistors and output amplifier summing points brought out of the package in order to make the absolute calibration possible. Figures 9 and 10 illustrate the relationship of offset and gain adjustments for the DAC7731 in a unipolar configuration and in a bipolar configuration, respectively.

FIGURE 9. Relationship of Offset and Gain Adjustments for  $V_{OUT} = 0V$  to +10V Output Configuration.

FIGURE 10. Relationship of Offset and Gain Adjustments for  $V_{OUT} = -10V$  to +10V Output Configuration. (Same Theory Applies for  $V_{OUT} = -5V$  to +5V.)

When calibrating the DAC output, offset should be adjusted first to avoid first order interaction of adjustments. In unipolar mode, the DAC7731 offset is adjusted from code  $0000_H$  and for either bipolar mode, offset adjustments are made at code  $8000_H$ . Gain adjustment can then be made at code FFFF<sub>H</sub> for each configuration, where the output of the DAC should be

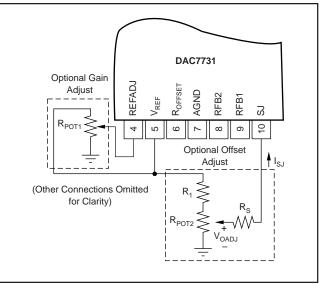

at  $\pm 10V - 1LSB$  for the 0V to  $\pm 10V$  or  $\pm 10V$  output range and  $\pm 5V - 1LSB$  for the  $\pm 5V$  output range. Figure 11 shows the generalized external offset and gain adjustment circuitry using potentiometers.

FIGURE 11. Generalized External Calibration Circuitry for Gain and Symmetrical Offset Adjustment.

#### OFFSET ADJUSTMENT

Offset adjustment is accomplished by introducing a small current into the summing junction (SJ) of the DAC7731. The voltage at SJ, or  $V_{SJ}$ , is dependent on the output configuration of the DAC7731. See Table IV for the required pin strapping for a given configuration and the nominal values of  $V_{SJ}$  for each output range.

| REFERENCE             | OUTPUT                                                                      | PIN                                  | V <sub>SJ</sub> <sup>(1)</sup>                   |                     |                                                                   |

|-----------------------|-----------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------|---------------------|-------------------------------------------------------------------|

| CONFIGURATION         | CONFIGURATION                                                               | ROFFSET                              | RFB1                                             | RFB2                |                                                                   |

| Internal<br>Reference | 0V to +10V<br>-10V to +10V<br>-5V to +5V                                    | to V <sub>REF</sub><br>NC<br>to AGND | to V <sub>OUT</sub><br>NC<br>to V <sub>OUT</sub> | to V <sub>OUT</sub> | +5V<br>+3.333V<br>+1.666V                                         |

| External<br>Reference | 0V to $V_{REF}$<br>- $V_{REF}$ to $V_{REF}$<br>- $V_{REF}/2$ to $V_{REF}/2$ | to V <sub>REF</sub><br>NC<br>to AGND |                                                  | to V <sub>OUT</sub> | V <sub>REF</sub> /2<br>V <sub>REF</sub> /3<br>V <sub>REF</sub> /6 |

NOTE: (1) Voltage measured at  $V_{SJ}$  for a given configuration.

TABLE IV. Nominal  $V_{\text{SJ}}$  versus  $V_{\text{OUT}}$  and Reference Configuration.

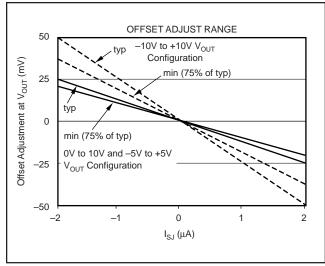

The current level required to adjust the DAC7731's offset can be created by using a potentiometer divider as shown in Figure 11 Another alternative is to use a unipolar DAC in order to apply a voltage,  $V_{OADJ}$ , to the resistor  $R_s$ . A ±2uA current range applied to SJ will ensure offset adjustment coverage of the ±0.1% maximum offset specification of the DAC7731.

When in a unipolar configuration ( $V_{SJ} = 5V$ ), only a single resistor,  $R_S$ , is needed for symmetrical offset adjustment with a 0V to 10V  $V_{OADJ}$  range. When in one of the two bipolar configurations,  $V_{SJ}$  is either +3.333V (±10V range) or +1.666V (±5V range), and circuit values chosen to match those given in Table V will provide symmetrical offset adjust. Please refer to Figure 11 for component configuration.

| OUTPUT<br>CONFIGURATION | R <sub>POT2</sub> | R <sub>1</sub> | R <sub>S</sub> | I <sub>SJ</sub><br>RANGE | NOMINAL<br>OFFSET<br>ADJUSTMENT |

|-------------------------|-------------------|----------------|----------------|--------------------------|---------------------------------|

| 0V to +10V              | 10K               | 0              | 2.5M           | ±2μΑ                     | ±25mV                           |

| -10V to +10V            | 10K               | 5K             | 1.5M           | ±2.2μΑ                   | ±55mV                           |

| -5V to +5V              | 10K               | 20K            | 1M             | ±1.7μΑ                   | ±21mV                           |

TABLE V. Recommended External Component Values for Symmetrical Offset Adjustment ( $V_{REF} = 10V$ ).

Figure 12 illustrates the typical minimum offset adjustment ranges provided by forcing a current at SJ for a given output voltage configuration.

FIGURE 12. Offset Adjustment Transfer Characteristic.

#### GAIN ADJUSTMENT

DAC7731

SBAS249B

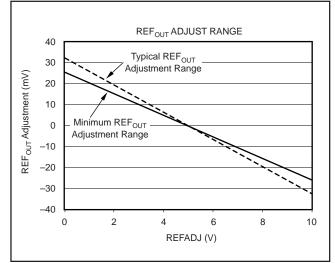

When using the internal reference of the DAC7731, gain adjustment is performed by adjusting the device's internal reference voltage via the reference adjust pin, REFADJ. The effect of a reference voltage change on the gain of the DAC output can be seen in the generic equation (for unipolar configuration):

$$V_{OUT} = V_{REFIN} \bullet (N/65536)$$

Where N is represented in decimal format and ranges from 0 to 65535.

REFADJ can be driven by a low impedance voltage source such as a unipolar, 0V to +10V DAC or a potentiometer (less than 100k $\Omega$ ), see Figure 11. Since the input impedance of REFADJ is typically 50k $\Omega$ , the smaller the resistance of the potentiometer, the more linear the adjustment will be. A 10k $\Omega$  potentiometer is suggested if linearity of the reference adjustment is of concern.

When the DAC7731's internal reference is not used, gain adjustments can be made via trimming the external reference applied to the DAC at  $\text{REF}_{\text{IN}}$ . This can be accomplished through using a potentiometer, unipolar DAC, or other means of precision voltage adjustment to control the voltage presented to the DAC7731 by the external reference. Figure 13 and Table VI summarize the range of adjustment of the internal reference via REFADJ.

FIGURE 13. Internal Reference Adjustment Transfer Characteristic.

| VOLTAGE AT REFADJ                  | REF <sub>OUT</sub> VOLTAGE |

|------------------------------------|----------------------------|

| REFADJ = 0V                        | 10V + 25mV (min)           |

| $REFADJ = 5V \text{ or } NC^{(1)}$ | 10V                        |

| REFADJ = 10V                       | 10V – 25mV (max)           |

| NOTE: NC - Not Connected           |                            |

TABLE VI. Minimum Internal Reference Adjustment Range.

#### NOISE PERFORMANCE

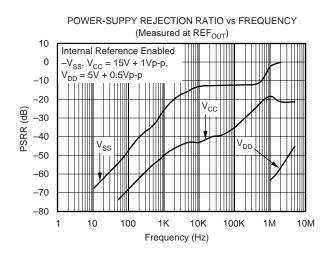

Increased noise performance of the DAC output can be achieved by filtering the voltage reference input to the DAC7731. Figure 14 shows a typical internal reference filter schematic. A low-pass filter applied between the  $\text{REF}_{OUT}$  and  $\text{REF}_{IN}$  pins can increase noise immunity at the DAC and output amplifier. The  $\text{REF}_{OUT}$  pin can source a maximum of 50µA so care should be taken in order to avoid overloading the internal reference output.

FIGURE 14. Filtering the Internal Reference.

# LAYOUT

A precision analog component requires careful layout, adequate bypassing, and clean, well-regulated power supplies. The DAC7731 offers separate digital and analog supplies, as it will often be used in close proximity with digital logic, microcontrollers, microprocessors, and digital signal processors. The more digital logic present in the design and the higher the switching speed, the more important it will become to separate the analog and digital ground and supply planes at the device.

Since the DAC7731 has both analog and digital ground pins, return currents can be better controlled and have less effect on the DAC output error. Ideally, AGND would be connected directly to an analog ground plane and DGND to the digital ground plane. The analog ground plane would be separate from the ground connection for the digital components until they were connected at the power-entry point of the system. The voltages applied to  $V_{CC}$  and  $V_{SS}$  should be well regulated and low noise. Switching power supplies and DC/DC converters will often have high-frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high-frequency spikes as their internal logic switches states. This noise can easily couple into the DAC output voltage through various paths between the power connections and analog output.

In addition, a  $1\mu F$  to  $10\mu F$  bypass capacitor in parallel with a  $0.1\mu F$  bypass capacitor is strongly recommended for each supply input. In some situations, additional bypassing may be required, such as a  $100\mu F$  electrolytic capacitor or even a Pi filter made up of inductors and capacitors–all designed to essentially low-pass filter the analog supplies, removing any high frequency noise components.

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                      |              |                         |         |

| DAC7731E         | ACTIVE        | SSOP         | DB                 | 24   | 60             | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E                | Samples |

| DAC7731E/1K      | ACTIVE        | SSOP         | DB                 | 24   | 1000           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E                | Samples |

| DAC7731EB        | ACTIVE        | SSOP         | DB                 | 24   | 60             | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E<br>B           | Samples |

| DAC7731EB/1K     | ACTIVE        | SSOP         | DB                 | 24   | 1000           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E<br>B           | Samples |

| DAC7731EC        | ACTIVE        | SSOP         | DB                 | 24   | 60             | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E<br>C           | Samples |

| DAC7731EC/1K     | ACTIVE        | SSOP         | DB                 | 24   | 1000           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E<br>C           | Samples |

| DAC7731ECG4      | ACTIVE        | SSOP         | DB                 | 24   | 60             | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR  | -40 to 85    | DAC7731E<br>C           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

www.ti.com

10-Dec-2020

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

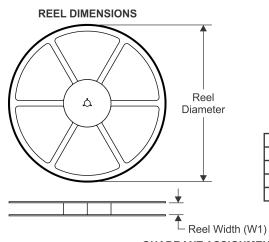

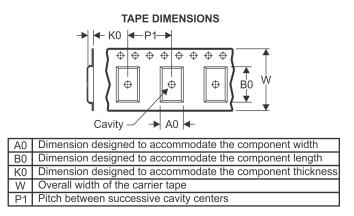

#### TAPE AND REEL INFORMATION

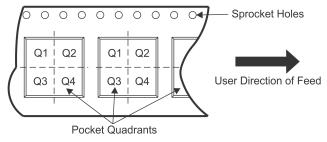

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      |      | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DAC7731E/1K                 | SSOP | DB                 | 24 | 1000 | 330.0                    | 16.4                     | 8.2        | 8.8        | 2.5        | 12.0       | 16.0      | Q1               |

| DAC7731EB/1K                | SSOP | DB                 | 24 | 1000 | 330.0                    | 16.4                     | 8.2        | 8.8        | 2.5        | 12.0       | 16.0      | Q1               |

| DAC7731EC/1K                | SSOP | DB                 | 24 | 1000 | 330.0                    | 16.4                     | 8.2        | 8.8        | 2.5        | 12.0       | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

### PACKAGE MATERIALS INFORMATION

30-Dec-2020

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC7731E/1K  | SSOP         | DB              | 24   | 1000 | 853.0       | 449.0      | 35.0        |

| DAC7731EB/1K | SSOP         | DB              | 24   | 1000 | 853.0       | 449.0      | 35.0        |

| DAC7731EC/1K | SSOP         | DB              | 24   | 1000 | 853.0       | 449.0      | 35.0        |

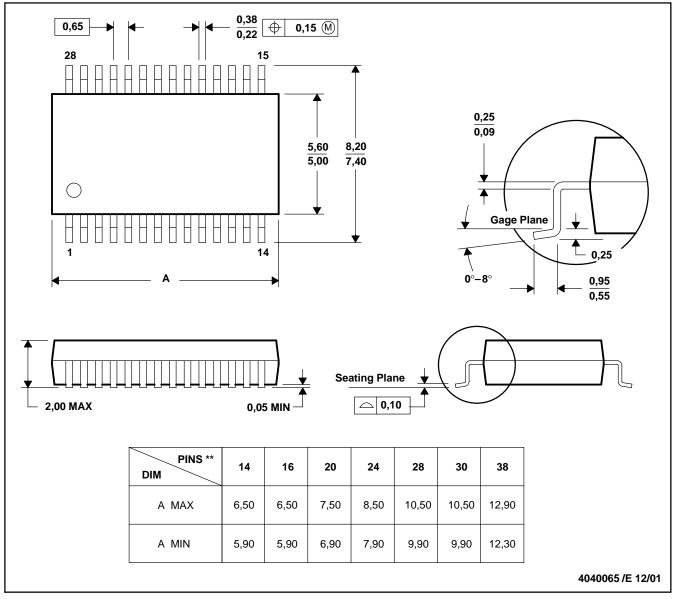

### **MECHANICAL DATA**

MSSO002E - JANUARY 1995 - REVISED DECEMBER 2001

### DB (R-PDSO-G\*\*)

PLASTIC SMALL-OUTLINE

28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-150

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated