Sample &

Buv

## FDC2212, FDC2214, FDC2112, FDC2114

SNOSCZ5A – JUNE 2015 – REVISED JUNE 2015

FDC2x1x EMI-Resistant 28-Bit,12-Bit Capacitance-to-Digital Converter for Proximity and Level Sensing Applications

Technical

Documents

## 1 Features

- EMI-Resistant Architecture

- Maximum Output Rates (one active channel):

- 13.3 ksps (FDC2112, FDC2114)

- 4.08 ksps (FDC2212, FDC2214)

- Maximum Input Capacitance: 250 nF (at 10 kHz with 1 mH inductor)

- Sensor Excitation Frequency: 10 kHz to 10 MHz

- Number of channels: 2, 4

- Resolution: up to 28 bits

- System Noise Floor: 0.3 fF at 100 sps

- Supply Voltage: 2.7 V to 3.6 V

- Power Consumption: Active: 2.1 mA

- Low-Power Sleep Mode: 35 uA

- Shutdown: 200 nA

- Interface: I<sup>2</sup>C

- Temperature range: -40°C to +125°C

## 2 Applications

- Proximity Sensor

- Gesture Recognition

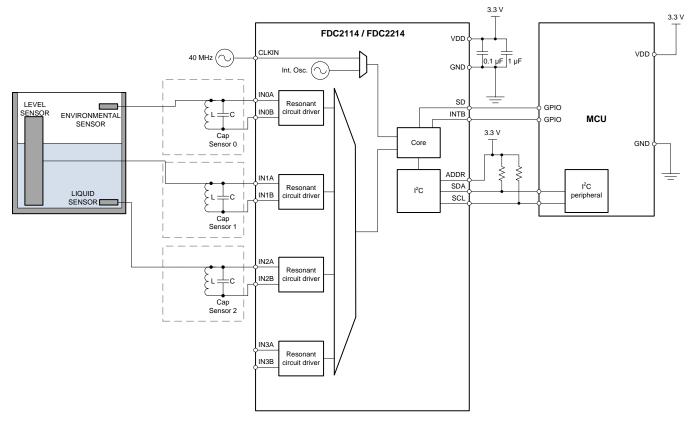

- Level Sensor for Liquids, including Conductive ones such as Detergent, Soap, and Ink

- Collision Avoidance

- Rain, Fog, Ice, Snow Sensor

- Automotive Door and Kick Sensors

- Material Size Detection

## 3 Description

Tools &

Software

Capacitive sensing is a low-power, low-cost, highresolution contactless sensing technique that can be applied to a variety of applications ranging from proximity detection and gesture recognition to remote liquid level sensing. The sensor in a capacitive sensing system is any metal or conductor, allowing for low cost and highly flexible system design.

Support &

Community

20

The main challenge limiting sensitivity in capacitive sensing applications is noise susceptibility of the sensors. With the FDC2x1x innovative EMI resistant architecture, performance can be maintained even in presence of high-noise environments.

The FDC2x1x is a multi-channel family of noise- and EMI-resistant, high-resolution, high-speed capacitance-to-digital converters for implementing capacitive sensing solutions. The devices employ an innovative narrow-band based architecture to offer high rejection of noise and interferers while providing high resolution at high speed. The devices support a wide excitation frequency range, offering flexibility in system design. A wide frequency range is especially useful for reliable sensing of conductive liquids such as detergent, soap, and ink.

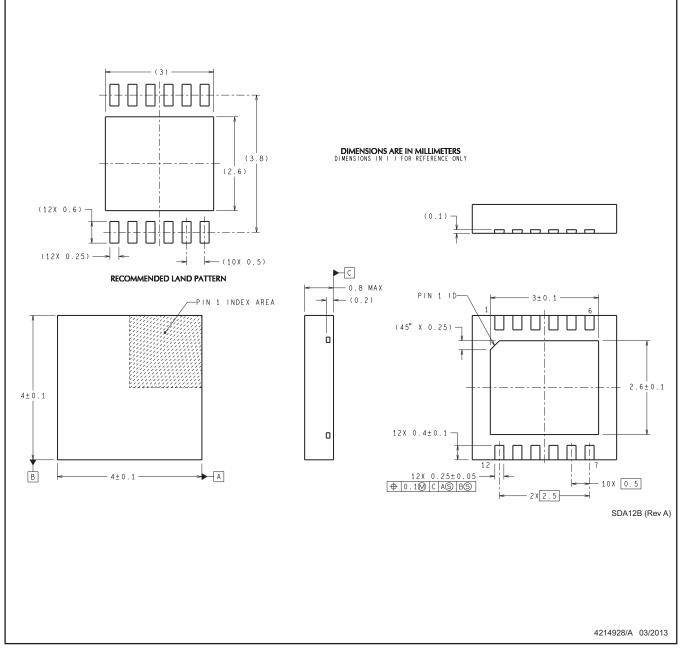

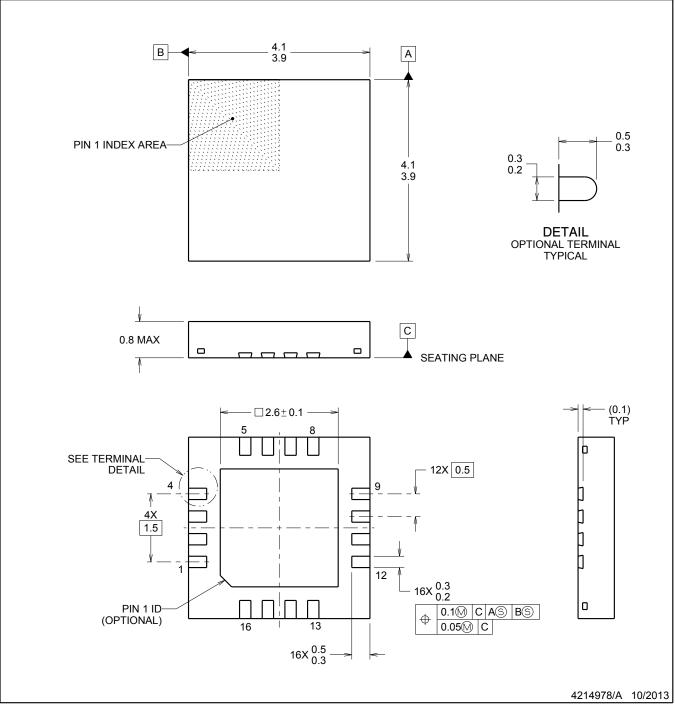

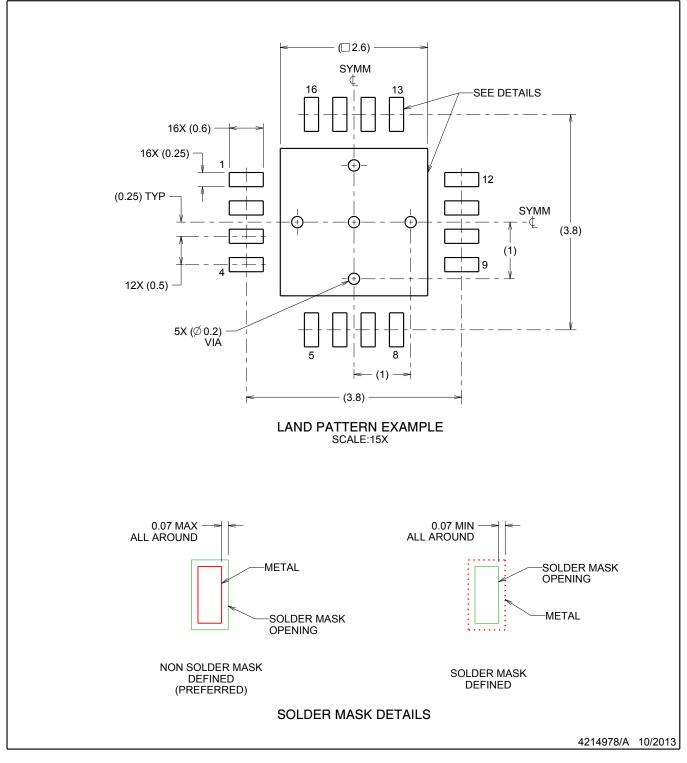

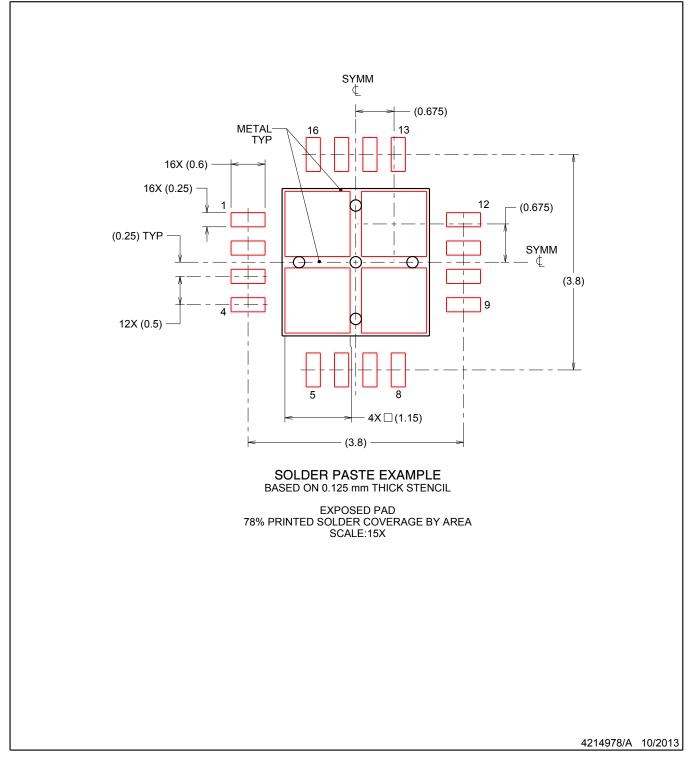

### Device Information<sup>(1)</sup>

| PART NUMBER      | PACKAGE       | BODY SIZE (NOM)   |

|------------------|---------------|-------------------|

| FDC2112, FDC2212 | WSON (DNT 12) | 4.00 mm x 4.00 mm |

| FDC2114, FDC2214 | WQFN (RGH 16) | 4.00 mm x 4.00 mm |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the datasheet.

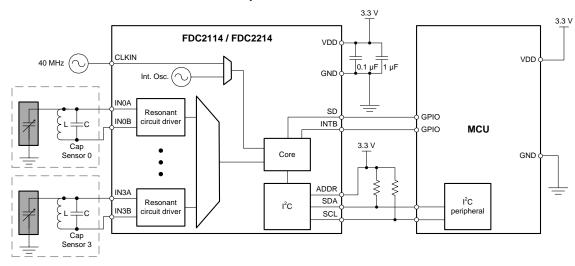

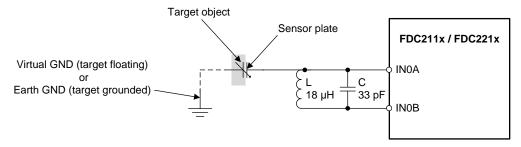

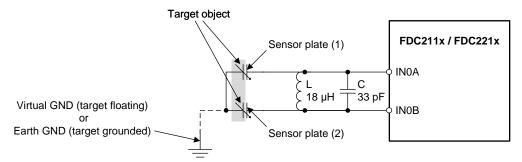

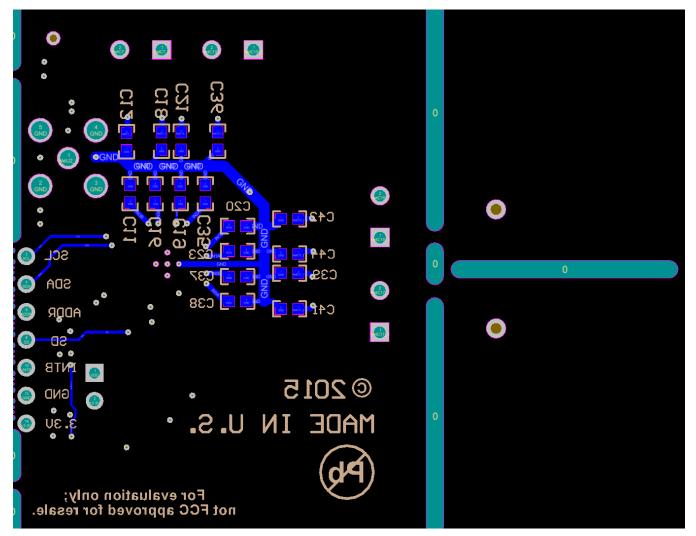

## **Simplified Schematic**

9.4 Device Functional Modes...... 21

Programming...... 21 9.6 Register Maps ..... 22 10.2 Typical Application ...... 40 10.3 Do's and Don'ts...... 46 11 Power Supply Recommendations ...... 46 12.1 Layout Guidelines ..... 46 12.2 Layout Example ..... 46 13 Device and Documentation Support ...... 51

Related Links ...... 51

13.3 Community Resources...... 51 13.4 Trademarks ...... 51 13.5 Electrostatic Discharge Caution ...... 51

Information ...... 51

Mechanical, Packaging, and Orderable

www.ti.com

# **Table of Contents**

9.5

13.1

13.2

14

| 1 | Feat | tures 1                           |

|---|------|-----------------------------------|

| 2 | Арр  | lications 1                       |

| 3 | Des  | cription 1                        |

| 4 | Rev  | ision History 2                   |

| 5 | Des  | cription, continued3              |

| 6 | Dev  | ice Comparison Table 3            |

| 7 | Pin  | Configuration and Functions 4     |

| 8 | Spe  | cifications5                      |

|   | 8.1  | Absolute Maximum Ratings 5        |

|   | 8.2  | ESD Ratings 5                     |

|   | 8.3  | Recommended Operating Conditions5 |

|   | 8.4  | Thermal Information5              |

|   | 8.5  | Electrical Characteristics 6      |

|   | 8.6  | Timing Requirements 7             |

|   | 8.7  | Switching Characteristics - I2C 8 |

|   | 8.8  | Typical Characteristics 9         |

| 9 | Deta | ailed Description 11              |

|   | 9.1  | Overview 11                       |

|   | 9.2  | Functional Block Diagrams 11      |

|   | 9.3  | Feature Description 12            |

|   |      |                                   |

# **4** Revision History

| Cł | hanges from Original (June 2015) to Revision A | Page |

|----|------------------------------------------------|------|

| •  | Added full datasheet.                          | 1    |

2

Copyright © 2015, Texas Instruments Incorporated

### 5 Description, continued

The FDC221x is optimized for high resolution, up to 28 bits, while the FDC211x offers fast sample rate, up to 13.3ksps, for easy implementation of applications that use fast moving targets. The very large maximum input capacitance of 250 nF allows for the use of remote sensors, as well as for tracking environmental changes over time, temperature and humidity.

The FDC2x1x family targets proximity sensing and liquid level sensing applications for any type of liquids. For non-conductive liquid level sensing applications in the presence of interferences such as human hands, the FDC1004 is recommended, which has integrated active shield drivers.

## 6 Device Comparison Table

| PART NUMBER | RESOLUTION | CHANNELS | PACKAGE |

|-------------|------------|----------|---------|

| FDC2112     | 12 bit     | 2        | WSON-12 |

| FDC2114     | 12 bit     | 4        | WQFN-16 |

| FDC2212     | 28 bit     | 2        | WSON-12 |

| FDC2214     | 28 bit     | 4        | WQFN-16 |

TEXAS INSTRUMENTS

www.ti.com

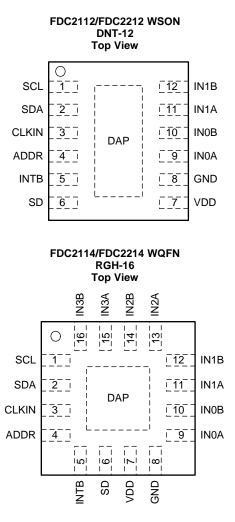

# 7 Pin Configuration and Functions

**Pin Functions**

| P     | IN  | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                 |  |

|-------|-----|---------------------|---------------------------------------------------------------------------------------------|--|

| NAME  | NO. | ITPE''              | DESCRIPTION                                                                                 |  |

| SCL   | 1   | I                   | I2C Clock input                                                                             |  |

| SDA   | 2   | I/O                 | I2C Data input/output                                                                       |  |

| CLKIN | 3   | I                   | Master Clock input. Tie this pin to GND if internal oscillator is selected                  |  |

| ADDR  | 4   | I                   | 2C Address selection pin: when ADDR=L, I2C address = 0x2A, when ADDR=H, I2C address = 0x2B. |  |

| INTB  | 5   | 0                   | Configurable Interrupt output pin                                                           |  |

| SD    | 6   | I                   | Shutdown input                                                                              |  |

| VDD   | 7   | Р                   | Power Supply                                                                                |  |

| GND   | 8   | G                   | Ground                                                                                      |  |

| IN0A  | 9   | A                   | Capacitive sensor input 0                                                                   |  |

| IN0B  | 10  | A                   | Capacitive sensor input 0                                                                   |  |

| IN1A  | 11  | A                   | Capacitive sensor input 1                                                                   |  |

| IN1B  | 12  | A                   | Capacitive sensor input 1                                                                   |  |

| IN2A  | 13  | A                   | Capacitive sensor input 2 (FDC2114 / FDC2214 only)                                          |  |

| IN2B  | 14  | A                   | Capacitive sensor input 2 (FDC2114 / FDC2214 only)                                          |  |

(1) I = Input, O = Output, P=Power, G=Ground, A=Analog

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

### **Pin Functions (continued)**

| PI                 | N   | TYPE <sup>(1)</sup> | DESCRIPTION                                        |  |

|--------------------|-----|---------------------|----------------------------------------------------|--|

| NAME               | NO. | ITPE'/              | DESCRIPTION                                        |  |

| IN3A               | 15  | A                   | Capacitive sensor input 3 (FDC2114 / FDC2214 only) |  |

| IN3B               | 16  | А                   | Capacitive sensor input 3 (FDC2114 / FDC2214 only) |  |

| DAP <sup>(2)</sup> | DAP | N/A                 | Connect to Ground                                  |  |

(2) There is an internal electrical connection between the exposed Die Attach Pad (DAP) and the GND pin of the device. Although the DAP can be left floating, for best performance the DAP should be connected to the same potential as the device's GND pin. Do not use the DAP as the primary ground for the device. The device GND pin must always be connected to ground.

# 8 Specifications

### 8.1 Absolute Maximum Ratings

|                  |                                  | MIN  | MAX       | UNIT |

|------------------|----------------------------------|------|-----------|------|

| VDD              | Supply voltage range             |      | 5         | V    |

| Vi               | Voltage on any pin               | -0.3 | VDD + 0.3 | V    |

| IA               | Input current on any INx pin     | -8   | 8         | mA   |

| ID               | Input current on any digital pin | -5   | 5         | mA   |

| TJ               | Junction temperature             | -55  | 150       | °C   |

| T <sub>stg</sub> | Storage temperature              | -65  | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                                            |                                                                          |                                                                          | VALUE | UNIT |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|-------|------|--|--|--|

| FDC211                                     | FDC2112 / FDC2212 in 12-pin WSON package                                 |                                                                          |       |      |  |  |  |

|                                            |                                                                          | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |  |  |  |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22- $C101^{(2)}$ | ±750                                                                     | V     |      |  |  |  |

| FDC211                                     | 14 / FDC2214 in 16-pin WQF                                               | N package                                                                | •     |      |  |  |  |

|                                            |                                                                          | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |  |  |  |

| V <sub>(ESD)</sub>                         | Electrostatic discharge                                                  | Charged-device model (CDM), per JEDEC specification JESD22- $C101^{(2)}$ | ±750  | V    |  |  |  |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ , VDD = 3.3 V

|                |                       | MIN | NOM MAX | UNIT |

|----------------|-----------------------|-----|---------|------|

| VDD            | Supply voltage        | 2.7 | 3.6     | V    |

| T <sub>A</sub> | Operating temperature | -40 | 125     | °C   |

### 8.4 Thermal Information

|                    |                                       | FDC2112 /         FDC2214 /           FDC2212         FDC2214 |         |      |  |

|--------------------|---------------------------------------|---------------------------------------------------------------|---------|------|--|

|                    | THERMAL METRIC <sup>(1)</sup>         | DNT (WSON) RGH (WQF                                           |         | UNIT |  |

|                    |                                       | 12 PINS                                                       | 16 PINS |      |  |

| R <sub>0JA</sub> J | unction-to-ambient thermal resistance | 50                                                            | 38      | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### FDC2212, FDC2214, FDC2112, FDC2114

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

### 8.5 Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ , VDD = 3.3 V<sup>(1)</sup>

|                           | PARAMETER                                                    | TEST CONDITIONS <sup>(2)</sup>                                                    | MIN <sup>(3)</sup> | TYP <sup>(4)</sup> | MAX <sup>(3)</sup> | UNIT |

|---------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| POWER                     |                                                              |                                                                                   |                    |                    |                    |      |

| V <sub>DD</sub>           | Supply voltage                                               | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$                                  | 2.7                |                    | 3.6                | V    |

| I <sub>DD</sub>           | Supply durrent (not including sensor current) <sup>(5)</sup> | CLKIN = 10MHz <sup>(6)</sup>                                                      |                    | 2.1                |                    | mA   |

| IDDSL                     | Sleep mode supply current <sup>(5)</sup>                     |                                                                                   |                    | 35                 | 60                 | μA   |

| I <sub>SD</sub>           | Shutdown mode supply current <sup>(5)</sup>                  |                                                                                   |                    | 0.2                | 1                  | μA   |

| CAPACITIVE SE             | NSOR                                                         |                                                                                   |                    |                    |                    |      |

| C <sub>SENSORMAX</sub>    | Maximum sensor capacitance                                   | 1mH inductor, 10kHz oscillation                                                   |                    | 250                |                    | nF   |

| C <sub>IN</sub>           | Sensor pin parasitic capacitance                             |                                                                                   |                    | 4                  |                    | pF   |

| N <sub>BITS</sub>         | Number of bits                                               | FDC2112, FDC2114<br>RCOUNT ≥ 0x0400                                               |                    |                    | 12                 | bits |

|                           |                                                              | FDC2212, FDC2214<br>RCOUNT = 0xFFFF                                               |                    |                    | 28                 | bits |

| f <sub>CS</sub>           | Maximum channel sample rate                                  | FDC2112, FDC2114<br>single active channel continuous<br>conversion, SCL = 400 kHz | 13.3               | 13.3               | kSPS               |      |

|                           |                                                              | FDC2212, FDC2214<br>single active channel continuous<br>conversion, SCL= 400 kHz  |                    |                    | 4.08               | kSPS |

| EXCITATION                |                                                              | -                                                                                 |                    |                    |                    |      |

| f <sub>SENSOR</sub>       | Sensor excitation frequency                                  | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$                                  | 0.01               |                    | 10                 | MHz  |

| V <sub>SENSORMIN</sub>    | Minimum sensor oscillation amplitude (pk) <sup>(7)</sup>     |                                                                                   |                    | 1.2                |                    | V    |

| VSENSORMAX                | Maximum sensor oscillation<br>amplitude (pk)                 |                                                                                   |                    | 1.8                |                    | V    |

| ISENSORMAX                | Sensor maximum current drive                                 | HIGH_CURRENT_DRV = b0<br>DRIVE_CURRENT_CH0 =<br>0xF800                            |                    | 1.5                |                    | mA   |

|                           |                                                              | HIGH_CURRENT_DRV = b1<br>DRIVE_CURRENT_CH0 =<br>0xF800<br>Channel 0 only          |                    | 6                  |                    | mA   |

| MASTER CLOCI              | ٢                                                            |                                                                                   |                    |                    |                    |      |

| f <sub>CLKIN</sub>        | External master clock input<br>frequency (CLKIN)             | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$                                  | 2                  |                    | 40                 | MHz  |

| CLKIN <sub>DUTY_MIN</sub> | External master clock minimum acceptable duty cycle (CLKIN)  |                                                                                   |                    | 40%                |                    |      |

| CLKIN <sub>DUTY_MAX</sub> | External master clock maximum acceptable duty cycle (CLKIN)  |                                                                                   |                    | 60%                |                    |      |

| V <sub>CLKIN_LO</sub>     | CLKIN low voltage threshold                                  |                                                                                   |                    |                    | 0.3*VDD            | V    |

- (1) Electrical Characteristics values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ . Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

- (2) Register values are represented as either binary (b is the prefix to the digits), or hexadecimal (0x is the prefix to the digits). Decimal values have no prefix.

- (3) Limits are ensured by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (4) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- (5) I2C read/write communication and pull-up resistors current through SCL, SDA not included.

- (6) Sensor capacitor: 1 layer, 20.9 x 13.9 mm, Bourns CMH322522-180KL sensor inductor with L=18µH and 33pF 1% COG/NP0 Target: Grounded aluminum plate (176 x 123 mm), Channel = Channel 0 (continuous mode) CLKIN = 40 MHz, CHx\_FIN\_SEL = b10, CHx\_FREF\_DIVIDER = b00 0000 0001 CH0\_RCOUNT = 0xFFFF, SETTLECOUNT\_CH0 = 0x0100, DRIVE\_CURRENT\_CH0 = 0x7800.

- (7) Lower V<sub>SENSORMIN</sub> oscillation amplitudes can be used, but will result in lower SNR.

www.ti.com

## **Electrical Characteristics (continued)**

|                       | PARAMETER                                             | TEST CONDITIONS <sup>(2)</sup> | MIN <sup>(3)</sup> | TYP <sup>(4)</sup> | MAX <sup>(3)</sup> | UNIT   |

|-----------------------|-------------------------------------------------------|--------------------------------|--------------------|--------------------|--------------------|--------|

| V <sub>CLKIN_HI</sub> | CLKIN high voltage threshold                          |                                | 0.7*VDD            |                    |                    | V      |

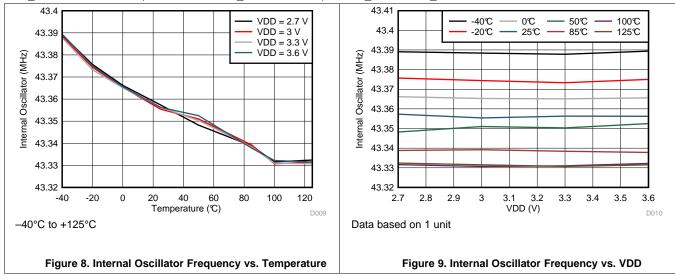

| f <sub>INTCLK</sub>   | Internal master clock frequency<br>range              |                                | 35                 | 43.4               | 55                 | MHz    |

| T <sub>Cf_int_µ</sub> | Internal master clock temperature<br>coefficient mean |                                |                    | -13                |                    | ppm/°C |

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}$ C, VDD = 3.3 V<sup>(1)</sup>

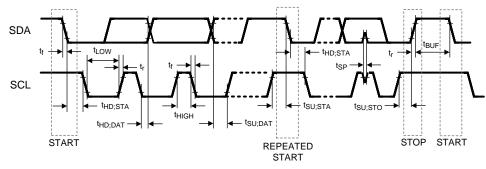

### 8.6 Timing Requirements

|                          |                                                                                             | MIN | NOM | MAX  | UNIT |

|--------------------------|---------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>SDWAKEUP</sub>    | Wake-up time from SD high-low transition to I2C readback                                    |     |     | 2    | ms   |

| t <sub>SLEEPWAKEUP</sub> | Wake-up time from sleep mode                                                                |     |     | 0.05 | ms   |

| t <sub>WD-TIMEOUT</sub>  | Sensor recovery time (after watchdog timeout)                                               |     | 5.2 |      | ms   |

| I2C TIMING C             | HARACTERISTICS                                                                              |     |     |      |      |

| f <sub>SCL</sub>         | Clock frequency                                                                             | 10  |     | 400  | kHz  |

| t <sub>LOW</sub>         | Clock low time                                                                              | 1.3 |     |      | μs   |

| t <sub>HIGH</sub>        | Clock high time                                                                             | 0.6 |     |      | μs   |

| t <sub>HD;STA</sub>      | Hold time (repeated) START condition: after this period, the first clock pulse is generated | 0.6 |     |      | μs   |

| t <sub>SU;STA</sub>      | Setup time for a repeated START condition                                                   | 0.6 |     |      | μs   |

| t <sub>HD;DAT</sub>      | Data hold time                                                                              | 0   |     |      | μs   |

| t <sub>SU;DAT</sub>      | Data setup time                                                                             | 100 |     |      | ns   |

| t <sub>SU;STO</sub>      | Setup time for STOP condition                                                               | 0.6 |     |      | μs   |

| t <sub>BUF</sub>         | Bus free time between a STOP and START condition                                            | 1.3 |     |      | μs   |

| t <sub>VD;DAT</sub>      | Data valid time                                                                             |     |     | 0.9  | μs   |

| t <sub>VD;ACK</sub>      | Data valid acknowledge time                                                                 |     |     | 0.9  | μs   |

| t <sub>SP</sub>          | Pulse width of spikes that must be suppressed by the input $\operatorname{filter}^{(1)}$    |     |     | 50   | ns   |

(1) This parameter is specified by design and/or characterization and is not tested in production.

Figure 1. I2C Timing

SNOSCZ5A – JUNE 2015 – REVISED JUNE 2015

www.ti.com

## 8.7 Switching Characteristics - I2C

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ , VDD = 3.3 V

|                 | PARAMETER                                 | TEST CONDITIONS | MIN     | TYP     | MAX     | UNIT |  |

|-----------------|-------------------------------------------|-----------------|---------|---------|---------|------|--|

| VOLTAGE LEVELS  |                                           |                 |         |         |         |      |  |

| V <sub>IH</sub> | Input high voltage                        |                 | 0.7×VDD |         |         | V    |  |

| V <sub>IL</sub> | Input low voltage                         |                 |         |         | 0.3×VDD | V    |  |

| V <sub>OL</sub> | Output low voltage (3 mA sink<br>current) |                 |         |         | 0.4     | V    |  |

| HYS             | Hysteresis                                |                 |         | 0.1×VDD |         | V    |  |

Copyright © 2015, Texas Instruments Incorporated

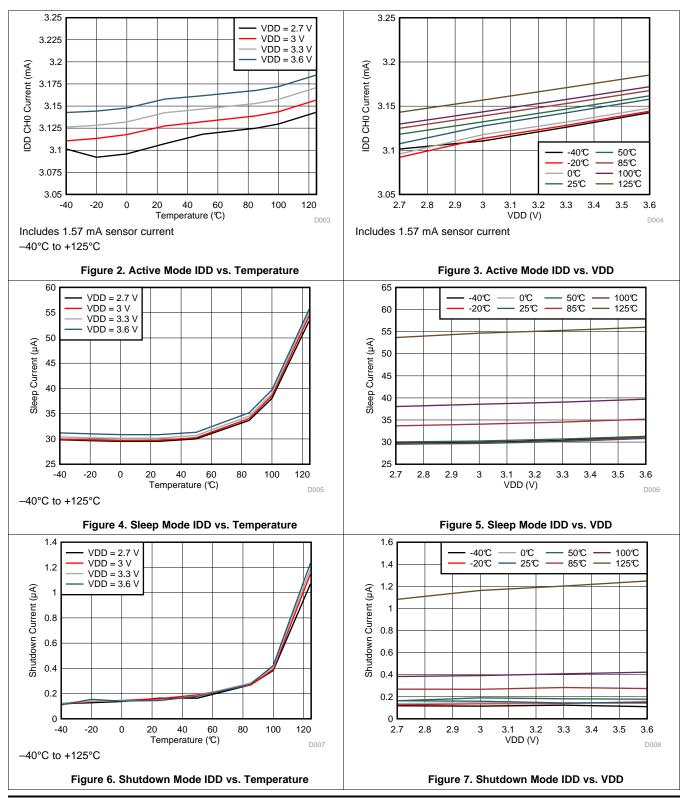

### 8.8 Typical Characteristics

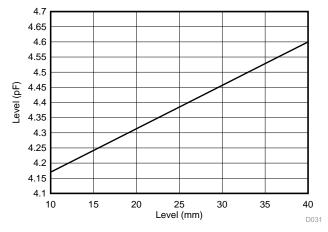

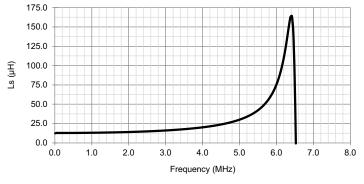

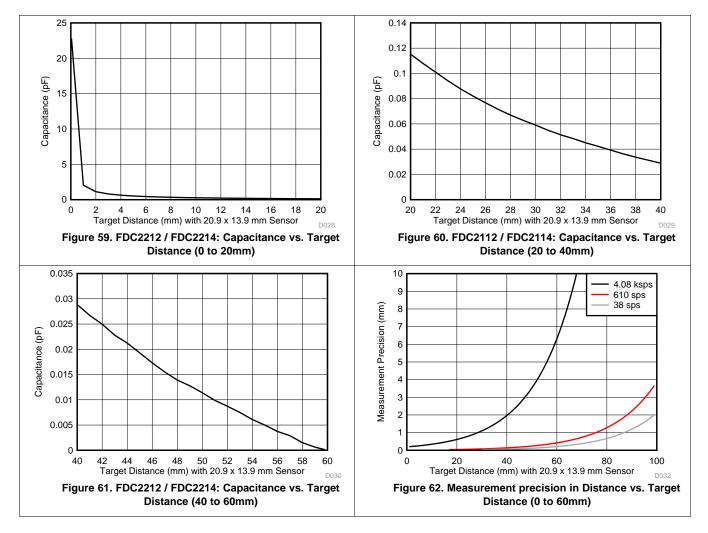

Common test conditions (unless specified otherwise): Sensor capacitor: 1 layer, 20.9 x 13.9 mm, Bourns CMH322522-180KL sensor inductor with L=18 µH and 33 pF 1% COG/NP0 Target: Grounded aluminum plate (176 x 123 mm), Channel = Channel 0 (continuous mode) CLKIN = 40 MHz, CHx\_FIN\_SEL = b01, CHx\_FREF\_DIVIDER = b00 0000 0001 CH0\_RCOUNT = 0xFFFF, SETTLECOUNT\_CH0 = 0x0100, DRIVE\_CURRENT\_CH0 = 0x7800.

Copyright © 2015, Texas Instruments Incorporated

Submit Documentation Feedback

9

Product Folder Links: FDC2212 FDC2214 FDC2112 FDC2114

## FDC2212, FDC2214, FDC2112, FDC2114

SNOSCZ5A – JUNE 2015 – REVISED JUNE 2015

www.ti.com

## **Typical Characteristics (continued)**

Common test conditions (unless specified otherwise): Sensor capacitor: 1 layer, 20.9 x 13.9 mm, Bourns CMH322522-180KL sensor inductor with L=18 µH and 33 pF 1% COG/NP0 Target: Grounded aluminum plate (176 x 123 mm), Channel = Channel 0 (continuous mode) CLKIN = 40 MHz, CHx\_FIN\_SEL = b01, CHx\_FREF\_DIVIDER = b00 0000 0001 CH0\_RCOUNT = 0xFFFF, SETTLECOUNT\_CH0 = 0x0100, DRIVE\_CURRENT\_CH0 = 0x7800.

Copyright © 2015, Texas Instruments Incorporated

## 9 Detailed Description

### 9.1 Overview

The FDC2112, FDC2114, FDC2212, and FDC2214 are high-resolution, multichannel capacitance-to-digital converters for implementing capacitive sensing solutions. In contrast to traditional switched-capacitance architectures, the FDC2112, FDC2114, FDC2212, and FDC2214 employ an L-C resonator, also known as L-C tank, as a sensor. The narrow-band architecture allows unprecedented EMI immunity and greatly reduced noise floor when compared to other capacitive sensing solutions.

Using this approach, a change in capacitance of the L-C tank can be observed as a shift in the resonant frequency. Using this principle, the FDC is a capacitance-to-digital converter (FDC) that measures the oscillation frequency of an LC resonator. The device outputs a digital value that is proportional to frequency. This frequency measurement can be converted to an equivalent capacitance

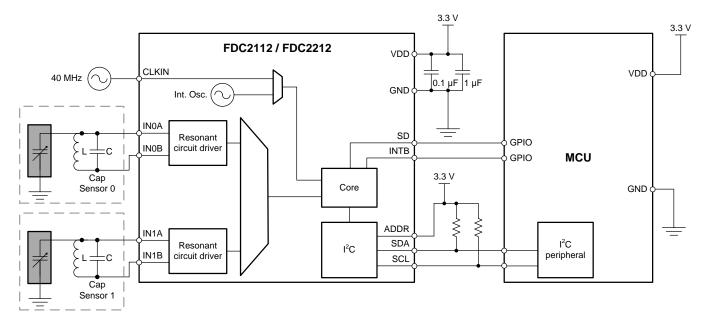

### 9.2 Functional Block Diagrams

Figure 10. Block Diagram for the FDC2112 and FDC2212

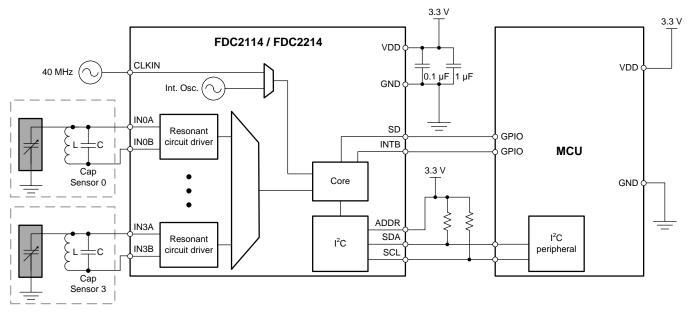

## **Functional Block Diagrams (continued)**

Figure 11. Block Diagrams for the FDC2114 and FDC2214

The FDC is composed of front-end resonant circuit drivers, followed by a multiplexer that sequences through the active channels, connecting them to the core that measures and digitizes the sensor frequency ( $f_{SENSOR}$ ). The core uses a reference frequency ( $f_{REF}$ ) to measure the sensor frequency.  $f_{REF}$  is derived from either an internal reference clock (oscillator), or an externally supplied clock. The digitized output for each channel is proportional to the ratio of  $f_{SENSOR}/f_{REF}$ . The I2C interface is used to support device configuration and to transmit the digitized frequency values to a host processor. The FDC can be placed in shutdown mode, saving current, using the SD pin. The INTB pin may be configured to notify the host of changes in system status.

### 9.3 Feature Description

### 9.3.1 Clocking Architecture

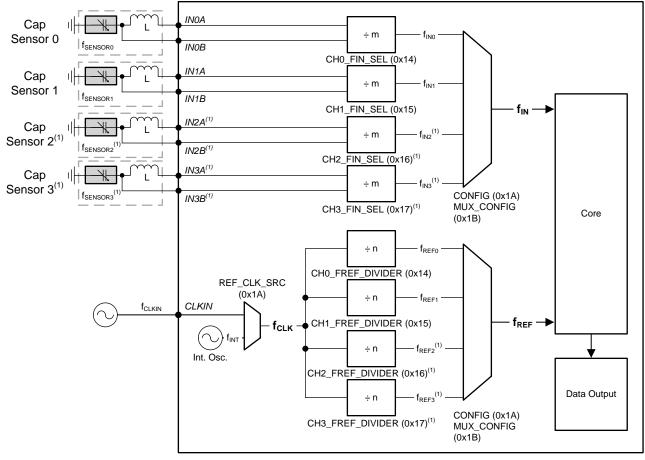

Figure 12 shows the clock dividers and multiplexers of the FDC.

### Feature Description (continued)

(1) FDC2114 / FDC2214 only

Figure 12. Clocking Diagram

In Figure 12, the key clocks are  $f_{IN}$ ,  $f_{REF}$ , and  $f_{CLK}$ .  $f_{CLK}$  is selected from either the internal clock source or external clock source (CLKIN). The frequency measurement reference clock,  $f_{REF}$ , is derived from the  $f_{CLK}$  source. It is recommended that precision applications use an external master clock that offers the stability and accuracy requirements needed for the application. The internal oscillator may be used in applications that require low cost and do not require high precision. The  $f_{INx}$  clock is derived from sensor frequency for a channel x,  $f_{SENSORx}$ .  $f_{REFx}$  and  $f_{INx}$  must meet the requirements listed in Table 1, depending on whether  $f_{CLK}$  (master clock) is the internal or external clock.

## Feature Description (continued)

| MODE <sup>(1)</sup> | CLKIN SOURCE                   | VALID f <sub>REFx</sub><br>RANGE (MHz) | VALID f <sub>INx</sub><br>RANGE | SET CHx_FIN_SEL to <sup>(2)</sup>                                                                                                              | SET<br>CHx_SETTLECO<br>UNT to | SET<br>CHx_RCOUNT to |

|---------------------|--------------------------------|----------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|

| Multi-channel       | Internal                       | f <sub>REFx</sub> ≤ 55                 |                                 | Differential sensor                                                                                                                            |                               |                      |

|                     | External                       | f <sub>REFx</sub> ≤ 40                 |                                 | configuration:<br>b01: 0.01MHz to                                                                                                              |                               |                      |

| Single-channel      | Either external or<br>internal | f <sub>REFx</sub> ≤ 35                 | < f <sub>REFx</sub> /4          | 8.75MHz (divide by 1)<br>b10: 5MHz to 10MHz<br>(divide by 2)<br>Single-ended sensor<br>configuration<br>b10: 0.01MHz to<br>10MHz (divide by 2) | > 3                           | > 8                  |

### Table 1. Clock Configuration Requirements

(1) Channels 2 and 3 are only available for FDC2114 and FDC2214.

(2) Refer to Sensor Configuration for information on differential and single-ended sensor configurations.

Table 2 shows the clock configuration registers for all channels.

| CHANNEL <sup>(1)</sup> | CLOCK                                     | REGISTER                          | FIELD [ BIT(S) ]       | VALUE                                                                                                                |

|------------------------|-------------------------------------------|-----------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------|

| All                    | f <sub>CLK</sub> = Master<br>Clock Source | CONFIG, addr<br>0x1A              | REF_CLK_SRC [9]        | b0 = internal oscillator is used as the<br>master clock<br>b1 = external clock source is used as the<br>master clock |

| 0                      | f <sub>REF0</sub>                         | CLOCK_DIVIDER<br>S_CH0, addr 0x14 | CH0_FREF_DIVIDER [9:0] | $f_{REF0} = f_{CLK} / CH0_FREF_DIVIDER$                                                                              |

| 1                      | f <sub>REF1</sub>                         | CLOCK_DIVIDER<br>S_CH1, addr 0x15 | CH1_FREF_DIVIDER [9:0] | $f_{REF1} = f_{CLK} / CH1_FREF_DIVIDER$                                                                              |

| 2                      | f <sub>REF2</sub>                         | CLOCK_DIVIDER<br>S_CH2, addr 0x16 | CH2_FREF_DIVIDER [9:0] | $f_{REF2} = f_{CLK} / CH2_FREF_DIVIDER$                                                                              |

| 3                      | f <sub>REF3</sub>                         | CLOCK_DIVIDER<br>S_CH3, addr 0x17 | CH3_FREF_DIVIDER [9:0] | $f_{REF3} = f_{CLK} / CH3_FREF_DIVIDER$                                                                              |

| 0                      | f <sub>INO</sub>                          | CLOCK_DIVIDER<br>S_CH0, addr 0x14 | CH0_FIN_SEL [13:12]    | $f_{IN0} = f_{SENSOR0} / CH0_FIN_SEL$                                                                                |

| 1                      | f <sub>IN1</sub>                          | CLOCK_DIVIDER<br>S_CH1, addr 0x15 | CH1_FIN_SEL [13:12]    | $f_{IN1} = f_{SENSOR1} / CH1_FIN_SEL$                                                                                |

| 2                      | f <sub>IN2</sub>                          | CLOCK_DIVIDER<br>S_CH2, addr 0x16 | CH2_FIN_SEL [13:12]    | $f_{IN2} = f_{SENSOR2} / CH2_FIN_SEL$                                                                                |

| 3                      | f <sub>IN3</sub>                          | CLOCK_DIVIDER<br>S_CH3, addr 0x17 | CH3_FIN_SEL [13:12]    | $f_{IN3} = f_{SENSOR3} / CH3_FIN_SEL$                                                                                |

### **Table 2. Clock Configuration Registers**

(1) Channels 2 and 3 are only available for FDC2114 and FDC2214

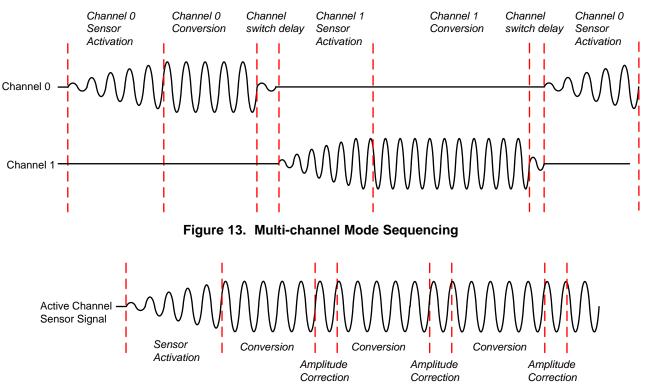

### 9.3.2 Multi-Channel and Single-Channel Operation

The multi-channel package of the FDC enables the user to save board space and support flexible system design. For example, temperature drift can often cause a shift in component values, resulting in a shift in resonant frequency of the sensor. Using a second sensor as a reference provides the capability to cancel out a temperature shift. When operated in multi-channel mode, the FDC sequentially samples the active channels. In single-channel mode, the FDC samples a single channel, which is selectable. Table 3 shows the registers and values that are used to configure either multi-channel or single-channel modes.

#### FDC2212, FDC2214, FDC2112, FDC2114

SNOSCZ5A – JUNE 2015 – REVISED JUNE 2015

#### www.ti.com

| MODE           | REGISTER             | FIELD [ BIT(S) ]    | VALUE                                                   |

|----------------|----------------------|---------------------|---------------------------------------------------------|

|                |                      |                     | 00 = chan 0                                             |

|                | CONFIC addr 0v1A     | ACTIVE CHAN [15:14] | 01 = chan 1                                             |

| Single channel | CONFIG, addr 0x1A    | ACTIVE_CHAN [15.14] | 10 = chan 2                                             |

|                |                      |                     | 11 = chan 3                                             |

|                | MUX_CONFIG addr 0x1B | AUTOSCAN_EN [15]    | 0 = continuous conversion on a single channel (default) |

|                | MUX_CONFIG addr 0x1B | AUTOSCAN_EN [15]    | 1 = continuous conversion on<br>multiple channels       |

| Multi-channel  | inel                 |                     | 00 = Ch0, Ch 1                                          |

|                | MUX_CONFIG addr 0x1B |                     | 01 = Ch0, Ch 1, Ch 2                                    |

|                |                      |                     | 10 = Ch0, CH1, Ch2, Ch3                                 |

The digitized sensor measurement for each channel (DATAx) represents the ratio of the sensor frequency to the reference frequency.

The data output (DATAx) of the FDC2112 and FDC2114 is expressed as the 12 MSBs of a 16-bit result:

$$\mathsf{DATA}_{\mathsf{X}} = \frac{f_{\mathsf{SENSORx}} * 2^{12}}{f_{\mathsf{REFx}}} \tag{1}$$

The data output (DATAx) of the FDC2212 and FDC2214 is expressed as:

$$\mathsf{DATA}_{\mathsf{x}} = \frac{f_{\mathsf{SENSORx}} * 2^{28}}{f_{\mathsf{REFx}}}$$

(2)

Table 4 illustrates the registers that contain the fixed point sample values for each channel.

#### Table 4. Sample Data Registers

| CHANNEL <sup>(1)</sup> | REGISTER <sup>(2)</sup> | FIELD NAME [ BITS(S) ] AND<br>VALUE (FDC2112, FDC2114)                                      | FIELD NAME [ BITS(S) ] AND VALUE<br>(FDC2212, FDC2214) <sup>(3)(4)</sup> |

|------------------------|-------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 0                      | DATA_CH0, addr 0x00     | DATA0 [11:0]:<br>12 bits of the 16 bit result.<br>0x000 = under range<br>0xfff = over range | DATA0 [27:16]:<br>12 MSBs of the 28 bit result                           |

|                        | DATA_LSB_CH0, addr 0x01 | Not applicable                                                                              | DATA0 [15:0]:<br>16 LSBs of the 28 bit conversion result                 |

| 1                      | DATA_CH1, addr 0x02     | DATA1 [11:0]:<br>12 bits of the 16 bit result.<br>0x000 = under range<br>0xfff = over range | DATA1 [27:16]:<br>12 MSBs of the 28 bit result                           |

|                        | DATA_LSB_CH1, addr 0x03 | Not applicable                                                                              | DATA1 [15:0]:<br>16 LSBs of the 28 bit conversion result                 |

| 2                      | DATA_CH2, addr 0x04     | DATA2 [11:0]:<br>12 bits of the 16 bit result.<br>0x000 = under range<br>0xfff = over range | DATA2 [27:16]:<br>12 MSBs of the 28 bit result                           |

|                        | DATA_LSB_CH2, addr 0x05 | Not applicable                                                                              | DATA2 [15:0]:<br>16 LSBs of the 28 bit conversion result                 |

(1) Channels 2 and 3 are only available for FDC2114 and FDC2214.

- (2) The DATA\_CHx.DATAx register must always be read first, followed by the DATA\_LSB\_ CHx.DATAx register of the same channel to ensure data coherency.

- (3) A DATA value of 0x0000000 = under range for FDC2212/FDC2214.

- (4) A DATA value of 0xFFFFFF = over range for FDC2212/FDC2214.

Copyright © 2015, Texas Instruments Incorporated

SNOSCZ5A – JUNE 2015 – REVISED JUNE 2015

| CHANNEL <sup>(1)</sup> | REGISTER <sup>(2)</sup> | FIELD NAME [ BITS(S) ] AND<br>VALUE (FDC2112, FDC2114)                                      | FIELD NAME [ BITS(S) ] AND VALUE<br>(FDC2212, FDC2214) <sup>(3)(4)</sup> |

|------------------------|-------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 3                      | DATA_CH3, addr 0x06     | DATA3 [11:0]:<br>12 bits of the 16 bit result.<br>0x000 = under range<br>0xfff = over range | DATA3 [27:16]:<br>12 MSBs of the 28 bit result                           |

|                        | DATA_LSB_CH3, addr 0x07 | Not applicable                                                                              | DATA3 [15:0]:<br>16 LSBs of the 28 bit conversion result                 |

### Table 4. Sample Data Registers (continued)

When the FDC sequences through the channels in multi-channel mode, the dwell time interval for each channel is the sum of three parts:

- 1. sensor activation time

- 2. conversion time

- 3. channel switch delay

The sensor activation time is the amount of settling time required for the sensor oscillation to stabilize, as shown in Figure 13. The settling wait time is programmable and should be set to a value that is long enough to allow stable oscillation. The settling wait time for channel x is given by:

$t_{Sx} = (CHX\_SETTLECOUNT \times 16)/f_{REFx}$

Table 5 illustrates the registers and values for configuring the settling time for each channel.

Figure 14. Single-channel Mode Sequencing

TEXAS INSTRUMENTS

www.ti.com

(3)

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

#### **Table 5. Settling Time Register Configuration**

| CHANNEL <sup>(1)</sup> | REGISTER                   | FIELD                  | CONVERSION TIME <sup>(2)</sup>         |

|------------------------|----------------------------|------------------------|----------------------------------------|

| 0                      | SETTLECOUNT_CH0, addr 0x10 | CH0_SETTLECOUNT [15:0] | (CH0_SETTLECOUNT*16)/f <sub>REF0</sub> |

| 1                      | SETTLECOUNT_CH1, addr 0x11 | CH1_SETTLECOUNT [15:0] | (CH1_SETTLECOUNT*16)/f <sub>REF1</sub> |

| 2                      | SETTLECOUNT_CH2, addr 0x12 | CH2_SETTLECOUNT [15:0] | (CH2_SETTLECOUNT*16)/f <sub>REF2</sub> |

| 3                      | SETTLECOUNT_CH3, addr 0x13 | CH3_SETTLECOUNT [15:0] | (CH3_SETTLECOUNT*16)/f <sub>REF3</sub> |

(1) Channels 2 and 3 are available only in the FDC2114 and FDC2214.

(2) f<sub>REFx</sub> is the reference frequency configured for the channel.

#### The SETTLECOUNT for any channel x must satisfy:

CHx\_SETTLECOUNT >  $V_{Dk} \times f_{REFx} \times C \times \pi^2 / (32 \times IDRIVE_X)$

where

- V<sub>pk</sub> = Peak oscillation amplitude at the programmed IDRIVE setting

- f<sub>REFx</sub> = Reference frequency for Channel x

- C = sensor capacitance including parasitic PCB capacitance

- IDRIVE<sub>X</sub> = setting programmed into the IDRIVE register in amps

(4)

Round the result to the next highest integer (for example, if Equation 4 recommends a minimum value of 6.08, program the register to 7 or higher).

The conversion time represents the number of reference clock cycles used to measure the sensor frequency. It is set by the CHx\_RCOUNT register for the channel. The conversion time for any channel x is:

```

t_{Cx} = (CHx_RCOUNT \times 16 + 4) / f_{REFx}

```

(5)

The reference count value must be chosen to support the required number of effective bits (ENOB). For example, if an ENOB of 13 bits is required, then a minimum conversion time of  $2^{13}$  = 8192 clock cycles is required. 8192 clock cycles correspond to a CHx\_RCOUNT value of 0x0200.

| CHANNEL | REGISTER              | FIELD [ BIT(S) ]  | CONVERSION TIME                   |

|---------|-----------------------|-------------------|-----------------------------------|

| 0       | RCOUNT_CH0, addr 0x08 | CH0_RCOUNT [15:0] | (CH0_RCOUNT*16)/f <sub>REF0</sub> |

| 1       | RCOUNT_CH1, addr 0x09 | CH1_RCOUNT [15:0] | (CH1_RCOUNT*16)/f <sub>REF1</sub> |

| 2       | RCOUNT_CH2, addr 0x0A | CH2_RCOUNT [15:0] | (CH2_RCOUNT*16)/f <sub>REF2</sub> |

| 3       | RCOUNT_CH3, addr 0x0B | CH3_RCOUNT [15:0] | (CH3_RCOUNT*16)/f <sub>REF3</sub> |

(1) Channels 2 and 3 are available only for FDC2114 and FDC2214.

The typical channel switch delay time between the end of conversion and the beginning of sensor activation of the subsequent channel is:

Channel Switch Delay = 692 ns + 5 /  $f_{ref}$

(6)

The deterministic conversion time of the FDC allows data polling at a fixed interval. For example, if the programmed RCOUNT setting is 512  $F_{REF}$  cycles and SETTLECOUNT is 128  $F_{REF}$  cycles, then one conversion takes 1.8ms (sensor-activation time) + 3.2ms (conversion time) + 0.75ms (channel-switch delay) = 16.75ms per channel. If the FDC is configured for dual-channel operation by setting AUTOSCAN\_EN = 1 and RR\_SEQUENCE = 00, then one full set of conversion results will be available from the data registers every 33.5ms.

A data ready flag (DRDY) is also available for interrupt driven system designs (see the STATUS register description in *Register Maps*).

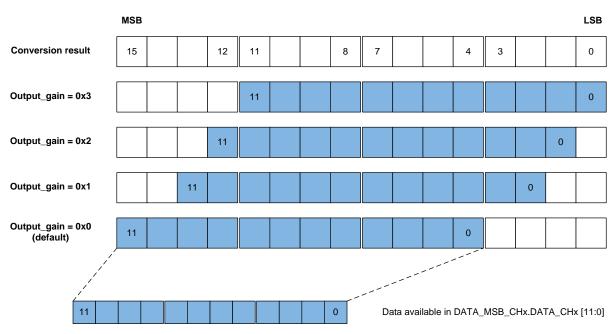

#### 9.3.2.1 Gain and Offset (FDC2112, FDC2114 only)

The FDC2112 and FDC2114 have internal 16-bit data converters, but the standard conversion output word width is only 12 bits; therefore only 12 of the 16 bits are available from the data registers. By default, the gain feature is disabled and the DATA registers contain the 12 MSBs of the 16-bit word. However, it is possible to shift the data output by up to 4 bits. Figure 15 illustrates the segment of the 16-bit sample that is reported for each possible gain setting.

Copyright © 2015, Texas Instruments Incorporated

#### TEXAS INSTRUMENTS

www.ti.com

### FDC2212, FDC2214, FDC2112, FDC2114

SNOSCZ5A – JUNE 2015 – REVISED JUNE 2015

Figure 15. Conversion Data Output Gain

For systems in which the sensor signal variation is less than 25% of the full-scale range, the FDC can report conversion results with higher resolution by setting the Output Gain. The Output Gain is applied to all device channels. An output gain can be used to apply a 2-bit, 3-bit, or 4-bit shift to the output code for all channels, allowing access to the 4 LSBs of the original 16-bit result. The MSBs of the sample are shifted out when a gain is applied. Do not use the output gain if the MSBs of any active channel are toggling, as the MSBs for that channel will be lost when gain is applied.

**Example**: If the conversion result for a channel is 0x07A3, with OUTPUT\_GAIN=0x0, the reported output code is 0x07A. If OUTPUT\_GAIN is set to 0x3 in the same condition, then the reported output code is 0x7A3. The original 4 MSBs (0x0) are no longer accessible.

| CHANNEL <sup>(1)</sup> | REGISTER        | FIELD [ BIT(S) ] | VALUES                               | EFFECTIVE<br>RESOLUTION (BITS) | OUTPUT RANGE     |

|------------------------|-----------------|------------------|--------------------------------------|--------------------------------|------------------|

|                        | RESET_DEV, addr | OUTPUT_GAIN [    | 00 (default): Gain =1 (0 bits shift) | 12                             | 100% full scale  |

| All                    |                 |                  | 01: Gain = 4 (2 bits left shift)     | 14                             | 25% full scale   |

| All                    | 0x1C            | 10:9 ]           | 10: Gain = 8 (3 bits left shift)     | 15                             | 12.5% full scale |

|                        |                 |                  | 11 : Gain = 16 (4 bits left shift)   | 16                             | 6.25% full scale |

#### Table 7. Output Gain Register (FDC2112 and FDC2114 only)

(1) Channels 2 and 3 are available for FDC2114 only.

An offset value may be subtracted from each DATA value to compensate for a frequency offset or maximize the dynamic range of the sample data. The offset values should be <  $f_{SENSORx_MIN}$  /  $f_{REFx}$ . Otherwise, the offset might be so large that it masks the LSBs which are changing.

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

(7)

(9)

#### Table 8. Frequency Offset Registers

| CHANNEL(<br>1) | REGISTER              | FIELD [ BIT(S) ]    | VALUE                                                                     |

|----------------|-----------------------|---------------------|---------------------------------------------------------------------------|

| 0              | OFFSET_CH0, addr 0x0C | CH0_OFFSET [ 15:0 ] | $f_{OFFSET0} = CH0_OFFSET * (f_{REF0}/2^{16})$                            |

| 1              | OFFSET_CH1, addr 0x0D | CH1_OFFSET [ 15:0 ] | $f_{OFFSET1} = CH1_OFFSET * (f_{REF1}/2^{16})$                            |

| 2              | OFFSET_CH2, addr 0x0E | CH2_OFFSET [ 15:0 ] | $f_{OFFSET2} = CH2_OFFSET * (f_{REF2}/2^{16})$                            |

| 3              | OFFSET_CH3, addr 0x0F | CH3_OFFSET [ 15:0 ] | f <sub>OFFSET3</sub> = CH3_OFFSET * (f <sub>REF3</sub> /2 <sup>16</sup> ) |

(1) Channels 2 and 3 are only available for FDC2114 and FDC2214.

The sensor capacitance  $C_{\text{SENSE}}$  of a differential sensor configuration can be determined by:

$$C_{\text{SENSOR}} = \frac{1}{L * (2\pi * f_{\text{SENSORx}})^2} - C$$

where

• C = parallel sensor capacitance (see Figure 55)

The FDC2112 and FDC2114 sensor frequency f<sub>SENSORx</sub> can be determined by:

$$f_{\text{SENSORx}} = \text{CHx}_{\text{FIN}}\text{SEL} * f_{\text{REFx}} * \left(\frac{\text{DATAx}}{2^{(12+\text{OUTPUT}_{GAIN})}} + \frac{\text{CHx}_{\text{OFFSET}}}{2^{16}}\right)$$

where

- DATAx = Conversion result from the DATA\_CHx register

- CHx\_OFFSET = Offset value set in the OFFSET\_CHx register

- OUTPUT\_GAIN = output multiplication factor set in the RESET\_DEVICE.OUTPUT\_GAIN register (8)

The FDC2212 and FDC2214 sensor frequency f<sub>SENSORx</sub> can be determined by:

$f_{\text{SENSORx}} = \frac{2^{28}}{2^{28}}$  (FDC2212, FDC2214)

where

• DATAx = Conversion result from the DATA\_CHx register

#### 9.3.3 Current Drive Control Registers

The registers listed in Table 9 are used to control the sensor drive current. The recommendations listed in the last column of the table should be followed.

|                        |                              | _                        |                                                                                                                                                                 |

|------------------------|------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANNEL <sup>(1)</sup> | REGISTER                     | FIELD [ BIT(S) ]         | VALUE                                                                                                                                                           |

| All                    | CONFIG, addr 0x1A            | SENSOR_ACTIVATE_SEL [11] | Sets current drive for sensor activation.<br>Recommended value is b0 (Full Current<br>mode).                                                                    |

| 0                      | CONFIG, addr 0x1A            | HIGH_CURRENT_DRV [6]     | b0 = normal current drive (1.5 mA)<br>b1 = Increased current drive (> 1.5 mA)<br>for Ch 0 in single channel mode only.<br>Cannot be used in multi-channel mode. |

| 0                      | DRIVE_CURRENT_CH0, addr 0x1E | CH0_IDRIVE [15:11]       | Drive current used during the settling and conversion time for Ch. 0. Set such that 1.2V ≤ sensor oscillation amplitude (pk) ≤ 1.8V                             |

| 1                      | DRIVE_CURRENT_CH1, addr 0x1F | CH1_IDRIVE [15:11]       | Drive current used during the settling and conversion time for Ch. 1. Set such that 1.2V ≤ sensor oscillation amplitude (pk) ≤ 1.8V                             |

#### **Table 9. Current Drive Control Registers**

<sup>(1)</sup> Channels 2 and 3 are available for FDC2114 and FDC2214 only.

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

www.ti.com

| CHANNEL <sup>(1)</sup> | REGISTER                     | FIELD [ BIT(S) ]   | VALUE                                                                                                                                          |  |  |  |  |  |

|------------------------|------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2                      | DRIVE_CURRENT_CH2, addr 0x20 | CH2_IDRIVE [15:11] | Drive current used during the settling and conversion time for Ch. 2. Set such that $1.2V \le$ sensor oscillation amplitude (pk) $\le$ $1.8V$  |  |  |  |  |  |

| 3                      | DRIVE_CURRENT_CH3, addr 0x21 | CH3_IDRIVE [15:11] | Drive current used during the settling and conversion time for Ch. 3 . Set such that $1.2V \le$ sensor oscillation amplitude (pk) $\le$ $1.8V$ |  |  |  |  |  |

## Table 9. Current Drive Control Registers (continued)

The CHx\_IDRIVE field should be programmed such that the sensor oscillates at an amplitude between 1.2Vpk ( $V_{SENSORMIN}$ ) and 1.8Vpk ( $V_{SENSORMAX}$ ). An IDRIVE value of 00000 corresponds to 16  $\mu$ A, and IDRIVE = b11111 corresponds to 1563  $\mu$ A.

A high sensor current drive mode can be enabled to drive sensor coils with > 1.5mA on channel 0, only in single channel mode. This feature can be used when the sensor minimum recommended oscillation amplitude of 1.2V cannot be achieved with the highest IDRIVE setting. Set the HIGH\_CURRENT\_DRV register bit to b1 to enable this mode.

### 9.3.4 Device Status Registers

The registers listed in Table 10 may be used to read device status.

### Table 10. Status Registers

| CHANNEL <sup>(1)</sup> | REGISTER                 | FIELDS [ BIT(S) ]                                                                  | VALUES                                                                                             |

|------------------------|--------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| All                    | STATUS, addr 0x18        | 12 fields are available that contain various status bits [ 15:0 ]                  | Refer to Register Maps section<br>for a description of the individual<br>status bits.              |

| All                    | STATUS_CONFIG, addr 0x19 | 12 fields are available that are<br>used to configure status reporting<br>[ 15:0 ] | Refer to Register Maps section<br>for a description of the individual<br>error configuration bits. |

(1) Channels 2 and 3 are available for FDC2114 and FDC2114 only.

See the STATUS and STATUS\_CONFIG register description in the Register Map section. These registers can be configured to trigger an interrupt on the INTB pin for certain events. The following conditions must be met:

- 1. The error or status register must be unmasked by enabling the appropriate register bit in the STATUS\_CONFIG register

- 2. The INTB function must be enabled by setting CONFIG.INTB\_DIS to 0

When a bit field in the STATUS register is set, the entire STATUS register content is held until read or until the DATA\_CHx register is read. Reading also de-asserts INTB.

Interrupts are cleared by one of the following events:

- 1. Entering Sleep Mode

- 2. Power-on reset (POR)

- 3. Device enters Shutdown Mode (SD is asserted)

- 4. S/W reset

- 5. I2C read of the STATUS register: Reading the STATUS register will clear any error status bit set in STATUS along with the ERR\_CHAN field and de-assert INTB

Setting register CONFIG.INTB\_DIS to b1 disables the INTB function and holds the INTB pin high.

### 9.3.5 Input Deglitch Filter

The input deglitch filter suppresses EMI and ringing above the sensor frequency. It does not impact the conversion result as long as its bandwidth is configured to be above the maximum sensor frequency. The input deglitch filter can be configured in MUX\_CONFIG.DEGLITCH register field as shown in Table 11. For optimal performance, it is recommended to select the lowest setting that exceeds the sensor oscillation frequency. For example, if the maximum sensor frequency is 2.0 MHz, choose MUX\_CONFIG.DEGLITCH = b100 (3.3 MHz).

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

#### Table 11. Input Deglitch Filter Register

| CHANNEL <sup>(1)</sup> | MUX_CONFIG.DEGLITCH (addr 0x1B) REGISTER<br>VALUE | DEGLITCH FREQUENCY |

|------------------------|---------------------------------------------------|--------------------|

| ALL                    | 001                                               | 1 MHz              |

| ALL                    | 100                                               | 3.3 MHz            |

| ALL                    | 101                                               | 10 MHz             |

| ALL                    | 011                                               | 33 MHz             |

(1) Channels 2 and 3 are available for FDC2114 / FDC2214 only.

### 9.4 Device Functional Modes

#### 9.4.1 Start-up Mode

When the FDC powers up, it enters into Sleep Mode and will wait for configuration. Once the device is configured, exit Sleep Mode by setting CONFIG.SLEEP\_MODE\_EN to b0.

It is recommended to configure the FDC while in Sleep Mode. If a setting on the FDC needs to be changed, return the device to Sleep Mode, change the appropriate register, and then exit Sleep Mode.

#### 9.4.2 Normal (Conversion) Mode

When operating in the normal (conversion) mode, the FDC is periodically sampling the frequency of the sensor(s) and generating sample outputs for the active channel(s).

#### 9.4.3 Sleep Mode

Sleep Mode is entered by setting the CONFIG.SLEEP\_MODE\_EN register field to 1. While in this mode, the register contents are maintained. To exit Sleep Mode, set the CONFIG.SLEEP\_MODE\_EN register field to 0. After setting CONFIG.SLEEP\_MODE\_EN to b0, sensor activation for the first conversion will begin after 16,384  $f_{\rm INT}$  clock cycles. While in Sleep Mode the I2C interface is functional so that register reads and writes can be performed. While in Sleep Mode, no conversions are performed. In addition, entering Sleep Mode will clear any error condition and de-assert the INTB pin.

#### 9.4.4 Shutdown Mode

When the SD pin is set to high, the FDC will enter Shutdown Mode. Shutdown Mode is the lowest power state. To exit Shutdown Mode, set the SD pin to low. Entering Shutdown Mode will return all registers to their default state.

While in Shutdown Mode, no conversions are performed. In addition, entering Shutdown Mode will clear any error condition and de-assert the INTB pin. While the device is in Shutdown Mode, is not possible to read to or write from the device via the I2C interface.

#### 9.4.4.1 Reset

The FDC can be reset by writing to RESET\_DEV.RESET\_DEV. Conversion will stop and all register values will return to their default value. This register bit will always return 0b when read.

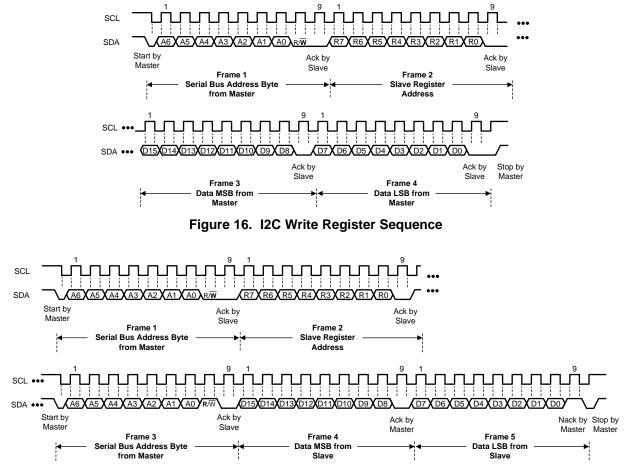

#### 9.5 Programming

The FDC device uses an I2C interface to access control and data registers.

#### 9.5.1 I2C Interface Specifications

The FDC uses an extended start sequence with I2C for register access. The maximum speed of the I2C interface is 400 kbit/s. This sequence follows the standard I2C 7-bit slave address followed by an 8-bit pointer register byte to set the register address. When the ADDR pin is set low, the FDC I2C address is 0x2A; when the ADDR pin is set high, the FDC I2C address is 0x2B. The ADDR pin must not change state after the FDC exits Shutdown Mode.

#### Copyright © 2015, Texas Instruments Incorporated

Submit Documentation Feedback 21

## **Programming (continued)**

Figure 17. I2C Read Register Sequence

## 9.6 Register Maps

#### 9.6.1 Register List

Fields indicated with Reserved must be written only with indicated values. Improper device operation may occur otherwise. The R/W column indicates the Read-Write status of the corresponding field. A 'R/W' entry indicates read and write capability, a 'R' indicates read-only, and a 'W' indicates write-only.

| ADDRESS | NAME         | DEFAULT VALUE | DESCRIPTION                                                                                        |

|---------|--------------|---------------|----------------------------------------------------------------------------------------------------|

| 0x00    | DATA_CH0     | 0x0000        | Channel 0 Conversion Result and status (FDC2112 / FDC2114 only)                                    |

|         |              | 0x0000        | Channel 0 MSB Conversion Result and status (FDC2212 / FDC2214 only)                                |

| 0x01    | DATA_LSB_CH0 | 0x0000        | Channel 0 LSB Conversion Result. Must be read after Register address 0x00 (FDC2212 / FDC2214 only) |

| 0x02    | DATA_CH1     | 0x0000        | Channel 1 Conversion Result and status (FDC2112 / FDC2114 only)                                    |

|         |              | 0x0000        | Channel 1 MSB Conversion Result and status (FDC2212 / FDC2214 only)                                |

| 0x03    | DATA_LSB_CH1 | 0x0000        | Channel 1 LSB Conversion Result. Must be read after Register address 0x02 (FDC2212 / FDC2214 only) |

| 0x04    | DATA_CH2     | 0x0000        | Channel 2 Conversion Result and status (FDC2114 only)                                              |

|         |              | 0x0000        | Channel 2 MSB Conversion Result and status (FDC2214 only)                                          |

| 0x05    | DATA_LSB_CH2 | 0x0000        | Channel 2 LSB Conversion Result. Must be read after Register address 0x04 (FDC2214 only)           |

| Figure 18. Register List |

|--------------------------|

|--------------------------|

Copyright © 2015, Texas Instruments Incorporated

#### FDC2212, FDC2214, FDC2112, FDC2114

SNOSCZ5A-JUNE 2015-REVISED JUNE 2015

| ADDRESS | NAME               | DEFAULT VALUE | DESCRIPTION                                                                              |

|---------|--------------------|---------------|------------------------------------------------------------------------------------------|

| 0x06    | DATA_CH3           | 0x0000        | Channel 3 Conversion Result and status (FDC2114 only)                                    |

|         |                    | 0x0000        | Channel 3 MSB Conversion Result and status (FDC2214 only)                                |

| 0x07    | DATA_LSB_CH3       | 0x0000        | Channel 3 LSB Conversion Result. Must be read after Register address 0x06 (FDC2214 only) |

| 0x08    | RCOUNT_CH0         | 0x0080        | Reference Count setting for Channel 0                                                    |

| 0x09    | RCOUNT_CH1         | 0x0080        | Reference Count setting for Channel 1                                                    |

| 0x0A    | RCOUNT_CH2         | 0x0080        | Reference Count setting for Channel 2 (FDC2114 / FDC2214 only)                           |

| 0x0B    | RCOUNT_CH3         | 0x0080        | Reference Count setting for Channel 3 (FDC2114 / FDC2214 only)                           |

| 0x0C    | OFFSET_CH0         | 0x0000        | Offset value for Channel 0 (FDC2112 / FDC2114 only)                                      |

| 0x0D    | OFFSET_CH1         | 0x0000        | Offset value for Channel 1 (FDC2112 / FDC2114 only)                                      |

| 0x0E    | OFFSET_CH2         | 0x0000        | Offset value for Channel 2 (FDC2114 only)                                                |

| 0x0F    | OFFSET_CH3         | 0x0000        | Offset value for Channel 3 (FDC2114 only)                                                |

| 0x10    | SETTLECOUNT_CH0    | 0x0000        | Channel 0 Settling Reference Count                                                       |

| 0x11    | SETTLECOUNT_CH1    | 0x0000        | Channel 1 Settling Reference Count                                                       |

| 0x12    | SETTLECOUNT_CH2    | 0x0000        | Channel 2 Settling Reference Count (FDC2114 / FDC2214 only)                              |

| 0x13    | SETTLECOUNT_CH3    | 0x0000        | Channel 3 Settling Reference Count (FDC2114 / FDC2214 only)                              |

| 0x14    | CLOCK_DIVIDERS_CH0 | 0x0000        | Reference divider settings for Channel 0                                                 |

| 0x15    | CLOCK_DIVIDERS_CH1 | 0x0000        | Reference divider settings for Channel 1                                                 |

| 0x16    | CLOCK_DIVIDERS_CH2 | 0x0000        | Reference divider settings for Channel 2 (FDC2114 / FDC2214 only)                        |

| 0x17    | CLOCK_DIVIDERS_CH3 | 0x0000        | Reference divider settings for Channel 3 (FDC2114 / FDC2214 only)                        |

| 0x18    | STATUS             | 0x0000        | Device Status Reporting                                                                  |

| 0x19    | STATUS_CONFIG      | 0x0000        | Device Status Reporting Configuration                                                    |

| 0x1A    | CONFIG             | 0x2801        | Conversion Configuration                                                                 |

| 0x1B    | MUX_CONFIG         | 0x020F        | Channel Multiplexing Configuration                                                       |

| 0x1C    | RESET_DEV          | 0x0000        | Reset Device                                                                             |

| 0x1E    | DRIVE_CURRENT_CH0  | 0x0000        | Channel 0 sensor current drive configuration                                             |

| 0x1F    | DRIVE_CURRENT_CH1  | 0x0000        | Channel 1 sensor current drive configuration                                             |

| 0x20    | DRIVE_CURRENT_CH2  | 0x0000        | Channel 2 sensor current drive configuration (FDC2114 / FDC2214 only)                    |

| 0x21    | DRIVE_CURRENT_CH3  | 0x0000        | Channel 3 sensor current drive configuration (FDC2114 / FDC2214 only)                    |

| 0x7E    | MANUFACTURER_ID    | 0x5449        | Manufacturer ID                                                                          |

| 0x7F    | DEVICE_ID          | 0x3054        | Device ID (FDC2112, FDC2114 only)                                                        |

|         |                    | 0x3055        | Device ID (FDC2212, FDC2214 only)                                                        |

### 9.6.2 Address 0x00, DATA\_CH0

### Figure 19. Address 0x00, DATA\_CH0

| 15       | 14      | 13 12      |            | 11 | 10  | 9  | 8 |

|----------|---------|------------|------------|----|-----|----|---|

| RESERVED |         | CH0_ERR_WD | CH0_ERR_AW |    | DAT | A0 |   |

| 7        | 7 6 5 4 |            | 3          | 2  | 1   | 0  |   |

| DATA0    |         |            |            |    |     |    |   |

### Table 12. Address 0x00, DATA\_CH0 Field Descriptions

| Bit   | Field                                    | Туре | Reset | Description                                                                   |

|-------|------------------------------------------|------|-------|-------------------------------------------------------------------------------|

| 15:14 | RESERVED                                 | R    | 00    | Reserved.                                                                     |

| 13    | CH0_ERR_WD                               | R    | 0     | Channel 0 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12    | CH0_ERR_AW                               | R    | 0     | Channel 0 Amplitude Warning. Cleared by reading the bit.                      |

| 11:0  | DATA0 (FDC2112 / FDC2114 only)           |      |       | Channel 0 Conversion Result                                                   |

|       | DATA0[27:16] (FDC2212 /<br>FDC2214 only) |      | 0000  |                                                                               |

Copyright © 2015, Texas Instruments Incorporated

Submit Documentation Feedback 23

### 9.6.3 Address 0x01, DATA\_LSB\_CH0 (FDC2212 / FDC2214 only)

#### Figure 20. Address 0x01, DATA\_LSB\_CH0

| 15              | 14 | 13 | 12  | 11  | 10 | 9 | 8 |

|-----------------|----|----|-----|-----|----|---|---|

|                 |    |    | DAT | TA0 |    |   |   |

| 7 6 5 4 3 2 1 0 |    |    |     |     |    | 0 |   |

| DATAO           |    |    |     |     |    |   |   |

#### Table 13. Address 0x01, DATA\_CH0 Field Descriptions

| Bit  | Field       | Туре | Reset             | Description                 |

|------|-------------|------|-------------------|-----------------------------|

| 15:0 | DATA0[15:0] | R    | 0000 0000<br>0000 | Channel 0 Conversion Result |

#### 9.6.4 Address 0x02, DATA\_CH1

### Figure 21. Address 0x02, DATA\_CH1

| 15    | 14   | 13         | 12         | 11    | 10 | 9 | 8 |  |

|-------|------|------------|------------|-------|----|---|---|--|

| RESER | RVED | CH1_ERR_WD | CH1_ERR_AW | DATA1 |    |   |   |  |

| 7     | 6    | 5          | 4          | 3     | 2  | 1 | 0 |  |

| DATA1 |      |            |            |       |    |   |   |  |

#### Table 14. Address 0x02, DATA\_CH1 Field Descriptions

| Bit   | Field                                    | Туре | Reset | Description                                                                   |

|-------|------------------------------------------|------|-------|-------------------------------------------------------------------------------|

| 15:14 | RESERVED                                 | R    | 00    | Reserved.                                                                     |

| 13    | CH1_ERR_WD                               | R    | 0     | Channel 1 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12    | CH1_ERR_AW                               | R    | 0     | Channel 1 Amplitude Warning. Cleared by reading the bit.                      |

| 11:0  | DATA1 (FDC2112 / FDC2114 only)           | R    |       | Channel 1 Conversion Result                                                   |

|       | DATA1[27:16] (FDC2212 /<br>FDC2214 only) |      | 0000  |                                                                               |

### 9.6.5 Address 0x03, DATA\_LSB\_CH1 (FDC2212 / FDC2214 only)

### Figure 22. Address 0x03, DATA\_LSB\_CH1

| 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 |

|----|----|----|-----|-----|----|---|---|

|    |    |    | DAT | TA1 |    |   |   |

| 7  | 6  | 5  | 4   | 3   | 2  | 1 | 0 |

|    |    |    | DAT | TA1 |    |   |   |

#### Table 15. Address 0x03, DATA\_CH1 Field Descriptions

| Bit  | Field       | Туре | Reset             | Description                 |

|------|-------------|------|-------------------|-----------------------------|

| 15:0 | DATA1[15:0] | R    | 0000 0000<br>0000 | Channel 1 Conversion Result |

### 9.6.6 Address 0x04, DATA\_CH2 (FDC2114, FDC2214 only)

### Figure 23. Address 0x04, DATA\_CH2

| 15    | 14   | 13         | 12         | 11 | 10  | 9   | 8 |

|-------|------|------------|------------|----|-----|-----|---|

| RESER | RVED | CH2_ERR_WD | CH2_ERR_AW |    | DAT | -A2 |   |

| 7     | 6    | 5          | 4          | 3  | 2   | 1   | 0 |

|       |      |            | DAT        | Ā2 |     |     |   |

|       |      |            |            |    |     |     |   |

### Table 16. Address 0x04, DATA\_CH2 Field Descriptions

| Bit   | Field                                    | Туре | Reset | Description                                                                   |

|-------|------------------------------------------|------|-------|-------------------------------------------------------------------------------|

| 15:14 | RESERVED                                 | R    | 00    | Reserved.                                                                     |

| 13    | CH2_ERR_WD                               | R    | 0     | Channel 2 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12    | CH2_ERR_AW                               | R    | 0     | Channel 2 Amplitude Warning. Cleared by reading the bit.                      |

| 11:0  | DATA2 (FDC2112 / FDC2114 only)           | R    |       | Channel 2 Conversion Result                                                   |

|       | DATA2[27:16] (FDC2212 /<br>FDC2214 only) |      | 0000  |                                                                               |

### 9.6.7 Address 0x05, DATA\_LSB\_CH2 (FDC2214 only)

### Figure 24. Address 0x05, DATA\_LSB\_CH2

| 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 |

|----|----|----|-----|-----|----|---|---|

|    |    |    | DAT | ΓA2 |    |   |   |

| 7  | 6  | 5  | 4   | 3   | 2  | 1 | 0 |

|    |    |    | DAT | ΓA2 |    |   |   |

### Table 17. Address 0x05, DATA\_CH2 Field Descriptions

| Bit  | Field       | Туре | Reset             | Description                 |

|------|-------------|------|-------------------|-----------------------------|

| 15:0 | DATA2[15:0] | R    | 0000 0000<br>0000 | Channel 2 Conversion Result |

### 9.6.8 Address 0x06, DATA\_CH3 (FDC2114, FDC2214 only)

### Figure 25. Address 0x06, DATA\_CH3

| 15   | 14   | 13         | 12         | 11 | 10  | 9  | 8 |

|------|------|------------|------------|----|-----|----|---|

| RESE | RVED | CH3_ERR_WD | CH3_ERR_AW |    | DAT | A3 |   |

| 7    | 6    | 5          | Λ          | 2  | 2   | 1  | 0 |

| 1    | 0    | J          | 4          | 3  | 2   |    | 0 |

|      |      |            | DAT        | A3 |     |    |   |

#### Table 18. Address 0x06, DATA\_CH3 Field Descriptions

| Bit   | Field                                    | Туре | Reset     | Description                                                                   |

|-------|------------------------------------------|------|-----------|-------------------------------------------------------------------------------|

| 15:14 | RESERVED                                 | R    | 00        | Reserved.                                                                     |

| 13    | CH3_ERR_WD                               | R    | 0         | Channel 3 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12    | CH3_ERR_AW                               | R    | 0         | Channel 3 Amplitude Warning. Cleared by reading the bit.                      |

| 11:0  | DATA3 (FDC2112 / FDC2114 only)           | R    | 0000 0000 | Channel 3 Conversion Result                                                   |

|       | DATA3[27:16] (FDC2212 /<br>FDC2214 only) |      | 0000      |                                                                               |

### 9.6.9 Address 0x07, DATA\_LSB\_CH3 (FDC2214 only)

### Figure 26. Address 0x07, DATA\_LSB\_CH3

| 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 |

|----|----|----|-----|-----|----|---|---|

|    |    |    | DAT | ГАЗ |    |   |   |

| 7  | 6  | 5  | 4   | 3   | 2  | 1 | 0 |

|    |    |    | DAT | TA3 |    |   |   |

#### Table 19. Address 0x07, DATA\_CH3 Field Descriptions

| Bit  | Field       | Туре | Reset             | Description                 |

|------|-------------|------|-------------------|-----------------------------|

| 15:0 | DATA3[15:0] | R    | 0000 0000<br>0000 | Channel 3 Conversion Result |

### 9.6.10 Address 0x08, RCOUNT\_CH0

### Figure 27. Address 0x08, RCOUNT\_CH0

| 15 | 14         | 13 | 12     | 11    | 10 | 9 | 8 |

|----|------------|----|--------|-------|----|---|---|