SNVS896B-AUGUST 2013-REVISED NOVEMBER 2014

LM27403

# LM27403 Synchronous Buck Controller With Temperature-Compensated, Inductor-DCR-**Based Overcurrent Protection and Programmable Thermal Shutdown**

#### **Features**

- Up to 97% Efficiency and 93% Duty Cycle

- Wide Input Voltage Range of 3 V to 20 V

- Switching Frequency From 200 kHz to 1.2 MHz

- Inductor-DCR-Based Overcurrent Protection With Thermal Compensation

- 0.6-V Reference With 1% Feedback Accuracy

- 30-ns Min On-Time for Low VOUT

- Integrated High-Current MOSFET Drivers

- Adaptive Deadtime Control

- Ultrafast Line and Load Transient Response

- High GBW Error Amplifier

- PWM Line Feedforward

- Integrated VDD Bias Supply LDO Subregulator

- Programmable System-Level OTP

- Precision Enable With Hysteresis

- Frequency Synchronization

- Monotonic Prebiased Start-up

- Programmable Soft-Start With Tracking

- Output Remote Sense

- Open-Drain Power Good Indicator

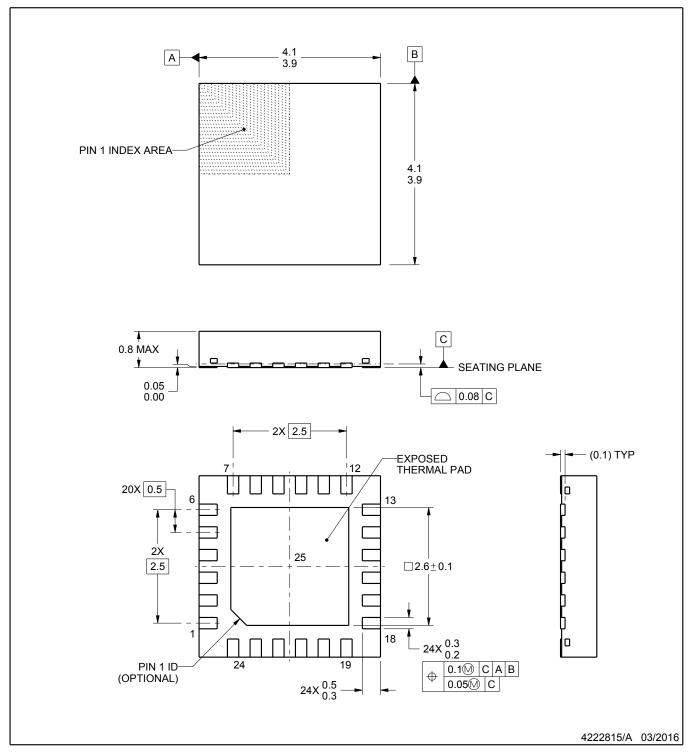

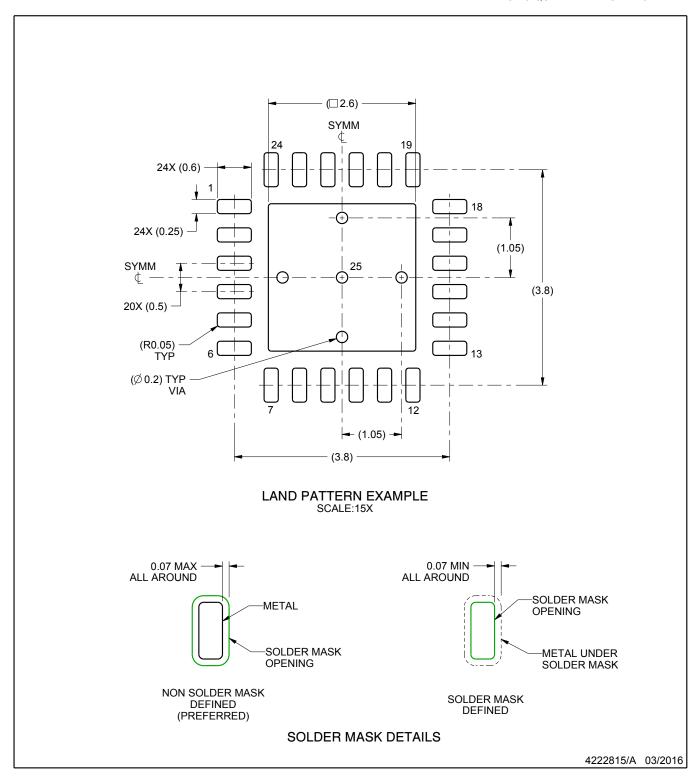

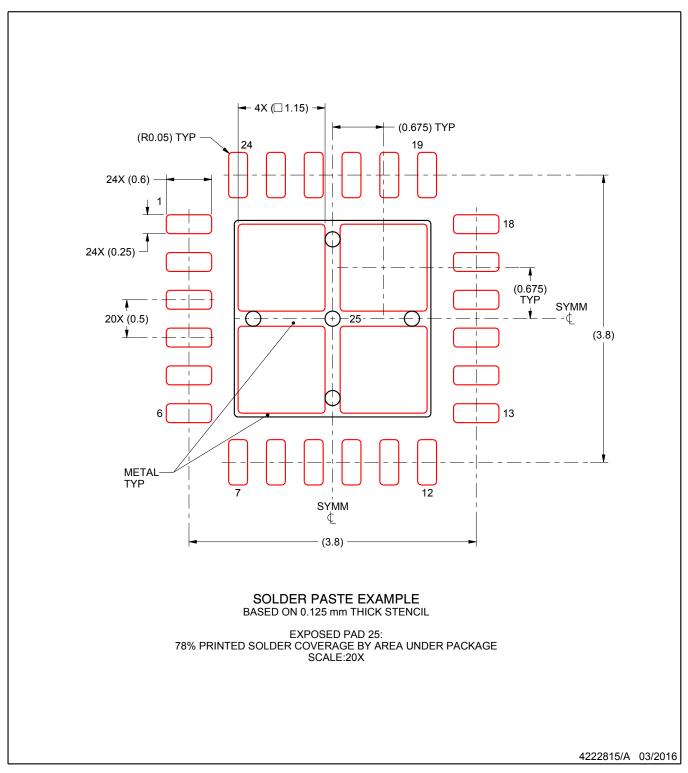

- 4-mm x 4-mm WQFN-24 PowerPAD™ Package

# 2 Applications

- DC-DC Converters and POL Modules

- Telecommunications Infrastructure

- Embedded Computing, Servers, Storage

# 3 Description

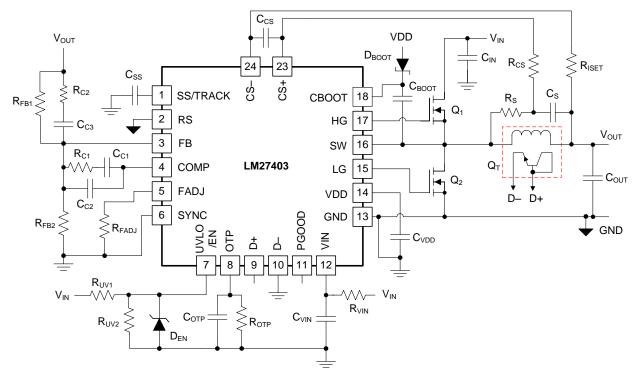

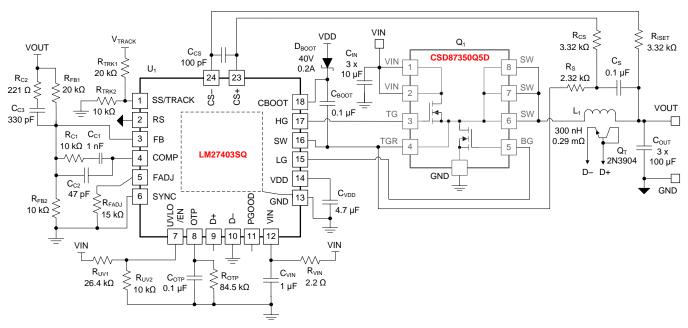

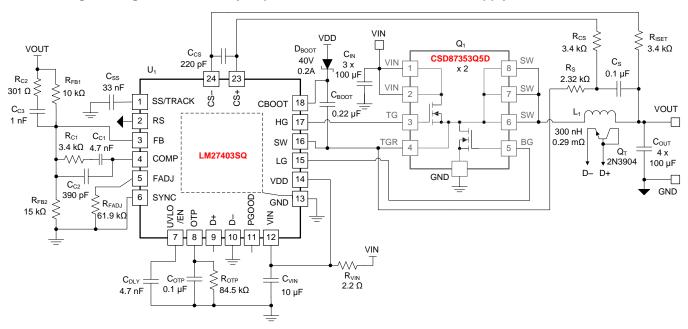

The LM27403 is a feature-rich, easy-to-use, synchronous buck controller offering exceptional levels of integration and performance for superior efficiency in high power density, point-of-load (POL) DC-DC regulator solutions. The resistorprogrammable switching frequency from 200 kHz to 1.2 MHz and integrated, high-current MOSFET gate drivers with adaptive deadtime offer flexibility to optimize solution size and maximize conversion efficiency.

High precision and low output voltage are easily obtained with a 0.6-V, 1% accurate voltage reference together with a 30-ns high-side MOSFET minimum controllable on-time. Using lossless inductor dc resistance (DCR) current sensing and an inexpensive 2N3904 BJT to sense temperature remotely at the inductor, the LM27403 supports accurate and thermally compensated overcurrent protection (OCP).

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LM27403     | WQFN (24) | 4.00 mm x 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

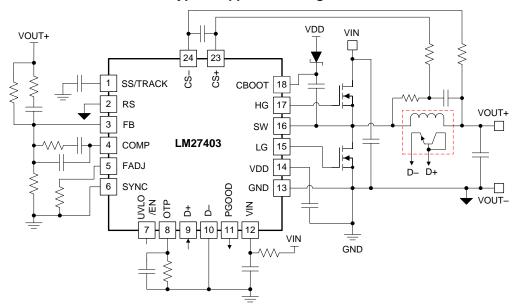

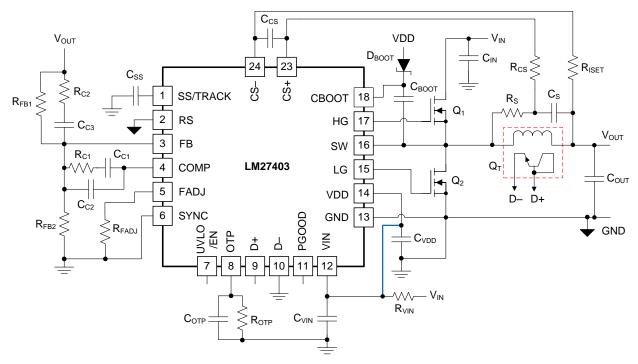

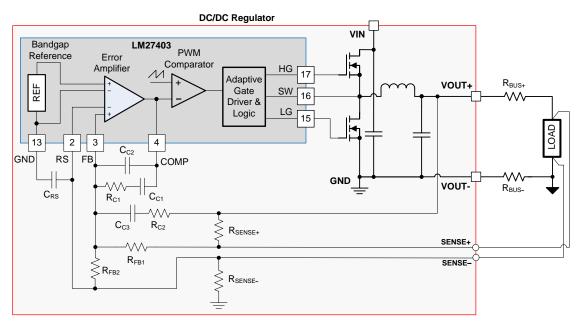

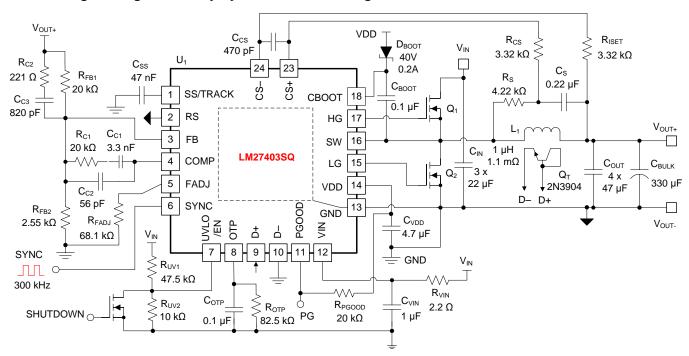

### Typical Application Diagram

# **Table of Contents**

| 1 | Features 1                                                          |    | 8.3 Feature Description                          | 14 |

|---|---------------------------------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                                                      |    | 8.4 Device Functional Modes                      | 28 |

| 3 | Description 1                                                       | 9  | Application and Implementation                   | 30 |

| 4 | Revision History2                                                   |    | 9.1 Application Information                      |    |

| 5 | Description (Continued)3                                            |    | 9.2 Typical Applications                         | 37 |

| 6 | Pin Configuration and Functions                                     | 10 | Power Supply Recommendations                     | 44 |

| 7 | Specifications5                                                     | 11 | Layout                                           | 44 |

| • | 7.1 Absolute Maximum Ratings                                        |    | 11.1 Layout Guidelines                           | 44 |

|   | 7.1 Absolute Maximum Ratings                                        |    | 11.2 Layout Example                              | 47 |

|   | 7.3 Recommended Operating Conditions                                | 12 | Device and Documentation Support                 |    |

|   | 7.4 Thermal Information                                             |    | 12.1 Device Support                              |    |

|   | 7.5 Electrical Characteristics 6                                    |    | 12.2 Documentation Support                       | 48 |

|   | 7.6 Typical Characteristics 9                                       |    | 12.3 Trademarks                                  | 48 |

| 8 | Detailed Description                                                |    | 12.4 Electrostatic Discharge Caution             | 48 |

| 0 |                                                                     |    | 12.5 Glossary                                    |    |

|   | 8.1 Overview       13         8.2 Functional Block Diagram       14 | 13 | Mechanical, Packaging, and Orderable Information |    |

# 4 Revision History

### Changes from Revision A (September 2013) to Revision B

**Page**

Added Pin Configuration and Functions section, Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section \_\_\_\_\_\_1

# 5 Description (Continued)

The LM27403 has a conventional voltage-mode control loop with high gain-bandwidth error amplifier and PWM input voltage feedforward to simplify compensation design and enable excellent transient response throughout the full line voltage and load current ranges. Forced-PWM (FPWM) operation eliminates frequency variation to minimize EMI in sensitive applications. An open-drain Power Good circuit provides power-rail sequencing and fault reporting. Other features include programmable system-level thermal shutdown with automatic recovery, output voltage remote sense, configurable soft-start, monotonic start-up into prebiased loads, an integrated bias supply low-dropout (LDO) regulator, external power supply tracking, precision enable with customizable hysteresis for programmable line undervoltage lockout (UVLO), and synchronization capability for beat frequency sensitive and multiregulator applications. The LM27403 is offered in a 4-mm x 4-mm thermally enhanced WQFN-24 package with 0.5-mm pitch.

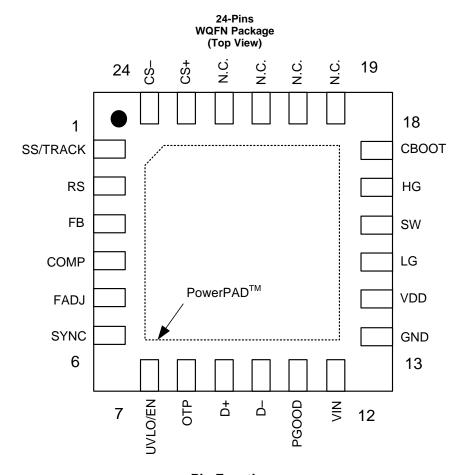

# 6 Pin Configuration and Functions

**Pin Functions**

| PII   | N   | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                |

|-------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | I/O/F ( )            | DESCRIPTION                                                                                                                                                                                                |

| СВООТ | 18  | Р                    | High-side bootstrap connection. This pin is the high-side N-FET gate driver power supply. Connect a 100-nF ceramic capacitor between CBOOT and SW.                                                         |

| COMP  | 4   | 0                    | Compensation node output. This pin is an output voltage control-loop error amplifier output. COMP is connected to the FB pin through a compensation network to ensure stability.                           |

| CS-   | 24  | 1                    | Current-sense negative input. This pin is the inverting input to the current-sense comparator. 9.9 $\mu$ A of nominal offset current at room temperature is provided to adjust the current limit setpoint. |

| CS+   | 23  | I                    | Current-sense positive input. This pin is the noninverting input to the current-sense comparator.                                                                                                          |

(1) I=Input, O=Output, P=Power, G=Ground

# Pin Functions (continued)

| PII      | PIN   |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------|-------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.   | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D-       | 10    | ı                    | External temperature sense return. This pin is the return current path for the external NPN transistor configured as a thermal diode. This trace should be routed as a differential pair with the D+ trace back to the LM27403 to avoid excessive coupling from external noise sources. Connect D- to GND.                                                                                                                                                                                                                                                                              |  |  |  |

| D+       | 9     | I                    | External temperature sense. A 2N3904-type NPN transistor configured as a remote thermal diode with the base and collector shorted should be connected to this pin to sense the inductor temperature. The sensed temperature is used to compensate for the inductor DCR drift over temperature and to implement system-level thermal shutdown protection.                                                                                                                                                                                                                                |  |  |  |

| UVLO/EN  | 7     | I                    | Precision UVLO/enable input. To implement a VIN UVLO function, connect UVLO/EN to the tap of a voltage divider between VIN and GND. UVLO/EN is initially pulled up by an internal 1.8- $\mu$ A pullup current source. UVLO/EN has both a 165-mV voltage hysteresis and an 8.7- $\mu$ A pullup current hysteresis. Thus, when a rising UVLO/EN voltage exceeds the 1.15-V enable threshold, the internal pullup current becomes 10.5 $\mu$ A and the falling threshold voltage is 0.985 V. Therefore, the effective total hysteresis can be customized to suit the specific application. |  |  |  |

| EP       | _     | Р                    | Exposed die attach pad. Connect this pad to the printed circuit board (PCB) ground plane using multiple thermal vias.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| FADJ     | 5     | I                    | Frequency adjust input. The switching frequency is programmable between 200 kHz and 1.2 MHz by virtue of the size of resistor connected to this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| FB       | 3     | ı                    | Feedback input. This pin is a voltage-mode control-loop error amplifier inverting input to set the output voltage. In closed-loop (output in regulation) operation, FB is at 0.6 V ±1%.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| GND      | 13    | G                    | Common ground connection. This pin provides the power and signal return connections for analog functions, including low-side MOSFET gate return, soft-start capacitor, OTP resistor, and frequency adjust resistor.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| HG       | 17    | 0                    | High-side MOSFET gate drive output. This pin is the high-side N-FET gate connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| LG       | 15    | 0                    | Low-side MOSFET gate drive output. This pin is the low-side N-FET gate connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| NC       | 19-22 | G                    | No connection. Connect directly to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| ОТР      | 8     | I                    | Overtemperature protection (OTP) output. A resistor and 0.1-µF capacitor from this pin to GND sets the overtemperature protection setpoint for the DC-DC power supply solution using the temperature sensed at a remotely connected thermal diode. Connect this pin to GND if the system level OTP function is not required.                                                                                                                                                                                                                                                            |  |  |  |

| PGOOD    | 11    | 0                    | Power Good monitor output. This open-drain output goes low during overcurrent, short-circuit, UVLO, output overvoltage and undervoltage, overtemperature, or when the output is not regulated (such as an output prebias). An external pullup resistor to VDD or to an external rail is required. Included is a 20-µs deglitch filter. The PGOOD voltage should not exceed 5.5 V.                                                                                                                                                                                                       |  |  |  |

| RS       | 2     | I                    | Negative remote sense input. This pin eliminates the voltage drop between GND and the local ground adjacent to the load. In particularly noisy environments, connect an RC filter between RS and GND. Connect RS to GND at the IC if not used.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SS/TRACK | 1     | I/O                  | Soft-start or tracking input. This pin allows a predetermined startup rate to be defined with the use of a capacitor to GND. A 3-µA current source charges the capacitor until the reference reaches 0.6 V. SS/TRACK can also be controlled with an external voltage source for tracking applications.                                                                                                                                                                                                                                                                                  |  |  |  |

| SW       | 16    | Р                    | Power stage switch-node connection. This pin is the high-side N-FET gate driver return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SYNC     | 6     | I                    | Synchronization input. This pin enables PLL synchronization to an external clock frequency. If a SYNC signal is not present, the switching frequency defaults to the frequency set by the FADJ pin. This pin should be tied to GND if not used.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VDD      | 14    | Р                    | Bias supply rail. This pin is a subregulated 4.7-V internal and gate drive bias supply rail. VDD also supplies the current to CBOOT to facilitate high-side switching. Decouple VDD to GND locally with a 10-µF ceramic capacitor. VDD should not be used to drive auxiliary system loads because of gate drive loading possibility.                                                                                                                                                                                                                                                    |  |  |  |

| VIN      | 12    | Р                    | Input voltage rail. This input is used to provide the feedforward modulation for output voltage control and for generating the internal bias supply voltage. Decouple VIN to GND locally with a 1-µF ceramic capacitor. For better noise rejection, connect to the power stage input rail with an RC filter.                                                                                                                                                                                                                                                                            |  |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>.

|                        |                                                | MIN  | MAX                      | UNIT |

|------------------------|------------------------------------------------|------|--------------------------|------|

| Voltage <sup>(2)</sup> | VIN, CS+, CS-, SW <sup>(3)(4)</sup>            | -0.3 | 22                       | V    |

|                        | VDD, PGOOD                                     | -0.3 | 6                        | V    |

|                        | SS/TRACK, SYNC, FADJ, COMP, FB, RS             | -0.3 | $V_{VDD} + 0.3$          | V    |

|                        | UVLO/EN                                        | -0.3 | min $(V_{VIN} + 0.3, 6)$ | V    |

| voltage                | CBOOT <sup>(5)</sup>                           | -0.3 | 24                       | V    |

|                        | CBOOT to SW                                    | -0.3 | 6                        | V    |

|                        | CS+ to CS-                                     | -1   | 1                        | V    |

|                        | OTP, D+, D-                                    | -0.3 | $V_{VDD}$                | V    |

| Thermal                | Operating junction temperature, T <sub>J</sub> | -40  | 150                      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those included under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

(2) All voltages are with respect to the network ground pin unless otherwise noted.

(3) The SW pin can tolerate negative voltage spikes as low as -10 V and as high as 30 V for a duration up to 10 ns.

(5) The CBOOT pin can tolerate positive voltage spikes as high as 35 V for a duration up to 10 ns.

# 7.2 Handling Ratings

|                    |                           |                                                                               | MIN  | MAX | UNIT |

|--------------------|---------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>   | Storage temperature range |                                                                               | -65  | 150 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | -2   | 2   | kV   |

|                    |                           | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -500 | 500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>.

|                |                                |                 | MIN  | NOM | MAX                          | UNIT |

|----------------|--------------------------------|-----------------|------|-----|------------------------------|------|

| VIN            | Input voltage (2)              | VIN tied to VDD | 3.0  |     | 5.5                          | V    |

| VIIN           | input voitage -                | VIN             | 3.0  |     | 20                           | V    |

| SW             | SW pin voltage                 |                 | -0.3 |     | 20                           | V    |

| VDD            | VDD pin voltage                |                 | 2.6  | 4.7 | 5.5                          | V    |

| PGOOD          | PGOOD pin voltage              |                 | 0    |     | 5.5                          | V    |

| UVLO/EN        | UVLO/EN pin voltage            |                 | 0    | r   | nin (V <sub>VIN</sub> , 5.5) | V    |

| SS/TRACK       | SS/TRACK pin voltage           |                 | 0    |     | $V_{VDD}$                    | V    |

| SYNC           | SYNC pin voltage               |                 | 0    |     | 5.5                          | V    |

| RS             | RS pin voltage                 |                 | -0.1 |     | 0.1                          | V    |

| $T_J$          | Operating junction temperature |                 | -40  |     | +125                         | °C   |

| T <sub>A</sub> | Operating free-air temperature |                 | -40  |     | +125                         | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which operation of the device is intended to be functional but does not guarantee performance limits.

<sup>(4)</sup> Body diode of the low-side MOSFET notwithstanding, parasitic inductance in a real application may result in the SW voltage ringing negative.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> VDD is the output of the internal linear regulator bias supply. Under normal operating conditions, where VIN is greater than 5.5 V, VDD must not be tied to any external voltage source. In an application where VIN is between 3.0 V and 5.5 V, connecting VIN to VDD maximizes the bias supply rail voltage.

#### 7.4 Thermal Information

|                         |                                              | LM27403 |       |

|-------------------------|----------------------------------------------|---------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                | RTW     | UNIT  |

|                         |                                              | 24 PINS |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 32.7    |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 31.2    |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 11.2    | °C/W  |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.2     | *C/VV |

| ΨЈВ                     | Junction-to-board characterization parameter | 11.2    |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 1.4     |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Electrical Characteristics

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over -40°C to +125°C junction temperature range unless otherwise stated<sup>(1)</sup>, <sup>(2)</sup>.  $V_{VIN}$  = 12 V and all parameters at zero power dissipation (unless otherwise noted).

|                        | PARAMETER                               | TEST CONDITIONS                                    | MIN    | TYP  | MAX  | UNIT |

|------------------------|-----------------------------------------|----------------------------------------------------|--------|------|------|------|

| OPERATION              | NAL SPECIFICATIONS                      |                                                    |        |      | '    |      |

| IQ                     | Quiescent current                       | V <sub>FB</sub> = 0.6 V (not switching)            |        | 3.5  | 5.0  | mA   |

| $I_{Q-SD}$             | Shutdown quiescent current              | V <sub>UVLO/EN</sub> = 0 V                         |        | 25   | 45   | μΑ   |

| REFERENC               | E                                       |                                                    |        |      |      |      |

| $V_{FB}$               | FB pin voltage accuracy                 |                                                    | 594    | 600  | 606  | mV   |

| $I_{FB}$               | FB pin bias current                     | V <sub>FB</sub> = 0.65 V                           | -165   | 0    | 165  | nA   |

| INTERNAL I             | UVLO                                    |                                                    |        |      |      |      |

| UVLO                   | Input undervoltage lockout              | V <sub>VIN</sub> rising, V <sub>VDD</sub> rising   | 2.6    | 2.7  | 2.8  | V    |

| UVLO_hys               | UVLO hysteresis                         | V <sub>VIN</sub> falling, V <sub>VDD</sub> falling |        | 250  |      | mV   |

| SWITCHING              | i                                       |                                                    | ,<br>, |      | ·    |      |

|                        |                                         | $R_{FADJ} = 4.12 \text{ k}\Omega$                  | 925    | 1050 | 1150 | kHz  |

| $F_{SW}$               | Switching frequency                     | $R_{FADJ} = 20 \text{ k}\Omega$                    | 435    | 500  | 555  | kHz  |

|                        |                                         | $R_{FADJ} = 95.3 \text{ k}\Omega$                  | 185    | 215  | 250  | kHz  |

| D <sub>MAX</sub>       | Maximum duty cycle                      | F <sub>SW</sub> = 500 kHz                          | 90%    | 93%  |      |      |

| T <sub>OFF-MIN</sub>   | Minimum off-time                        | $V_{FB} = 0.5 \text{ V}, F_{SW} = 500 \text{ kHz}$ | 110    | 150  | 190  | ns   |

| T <sub>ON-MIN</sub>    | Minimum controllable on-time            | V <sub>FB</sub> = 0.7 V, F <sub>SW</sub> = 500 kHz |        | 30   |      | ns   |

| VDD SUBRE              | GULATOR AND BOOT                        |                                                    |        |      |      |      |

| $V_{DD}$               | Subregulator output voltage             | I <sub>VDD</sub> = 25 mA                           | 4.2    | 4.7  | 5.3  | V    |

| $VDD_{VDO}$            | Dropout voltage                         | $I_{VDD} = 15 \text{ mA}, V_{VIN} = 3.0 \text{ V}$ |        | 150  |      | mV   |

| $VDD_{CL}$             | VDD current limit                       | V <sub>VDD</sub> = 4.0 V                           |        | 106  |      | mA   |

| I <sub>QBOOT</sub>     | CBOOT pin leakage current               | $V_{CBOOT} - V_{SW} = 4.5 \text{ V}$               |        | 0.5  |      | nA   |

| ERROR AM               | PLIFIER                                 |                                                    |        |      |      |      |

| BW <sub>-3dB</sub>     | Error amplifier open-loop bandwidth     |                                                    |        | 6    |      | MHz  |

| A <sub>VOL</sub>       | Error amplifier dc gain                 |                                                    |        | 70   |      | dB   |

| I <sub>SOURCE</sub>    | COMP source current                     | V <sub>FB</sub> = 0.5 V                            |        | 1    |      | mA   |

| I <sub>SINK</sub>      | COMP sink current                       | V <sub>FB</sub> = 0.7 V                            |        | 100  |      | μΑ   |

| V <sub>COMP-MAX</sub>  | Maximum COMP voltage                    | V <sub>FB</sub> = 0.5 V                            |        | 3.9  |      | V    |

| V <sub>COMP-MIN</sub>  | Minimum COMP voltage                    | V <sub>FB</sub> = 0.7 V                            |        | 0.5  |      | V    |

| OVERCURR               | ENT PROTECTION                          |                                                    |        |      |      |      |

| V <sub>CS_OFFSET</sub> | Current limit comparator offset voltage |                                                    | -3.5   | 0    | 3.5  | mV   |

<sup>(1)</sup> All hot and cold limits are specified by correlating the electrical characteristic to process and temperature variations and applying statistical process control.

<sup>(2)</sup> The junction temperature ( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$  in Watts) as follows:  $T_J = T_A + (P_D \times \theta_{JA})$  where (°C/W) is the package thermal impedance provided in the Thermal Information section.

# **Electrical Characteristics (continued)**

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over -40°C to +125°C junction temperature range unless otherwise stated<sup>(1)</sup>,<sup>(2)</sup>.  $V_{VIN}$  = 12 V and all parameters at zero power dissipation (unless otherwise noted).

|                          | PARAMETER                               |                                                     | NDITIONS                             | MIN  | TYP    | MAX  | UNIT   |

|--------------------------|-----------------------------------------|-----------------------------------------------------|--------------------------------------|------|--------|------|--------|

|                          | TAKAMETEK                               | $V_{CS-} = 3 \text{ V}, \Delta V_{BE} = 59.4$       |                                      | 9.3  | 9.9    | 10.5 |        |

| I <sub>CS</sub>          | Current limit offset current            |                                                     |                                      |      |        |      | μA<br> |

|                          |                                         | V <sub>CS</sub> <sub>-</sub> = 3 V, D+ shorted      | 10 D-                                | 3.4  | 5.0    | 6.6  | μA     |

| I <sub>CS-CV1</sub>      | I <sub>CS</sub> compliance voltage      | $V_{VIN} - V_{CS-}$ , $\Delta I_{CS} < 5\%$         | V <sub>VIN</sub> = 12 V              |      |        | 800  | mV     |

| I <sub>CS-CV2</sub>      |                                         |                                                     | V <sub>VIN</sub> = 3 V               |      |        | 800  | mV     |

| I <sub>CS-TC</sub>       | I <sub>CS</sub> temperature coefficient | Referenced to ΔV <sub>BE</sub> <sup>(4)</sup>       |                                      | 160  | 187    | 212  | nA/mV  |

| T <sub>CL-DELAY</sub>    | Current limit hiccup delay              |                                                     |                                      |      | 5      |      | ms     |

| GATE DRIVI               | ERS<br>⊤                                | T                                                   |                                      |      |        |      |        |

| R <sub>DS(ON)1</sub>     | High-side MOSFET driver on-state        | $V_{CBOOT} - V_{SW} = 4.5 \text{ V}$                | I <sub>HG</sub> = 0.1 A (pullup)     |      | 1.5    |      | Ω      |

| R <sub>DS(ON)2</sub>     | resistance                              | OBOOT OW                                            | $I_{HG} = -0.1 \text{ A (pulldown)}$ |      | 1.0    |      | Ω      |

| I <sub>DRV-HG-SRC</sub>  | High-side MOSFET driver peak            | C <sub>LOAD</sub> = 3 nF                            | Source current (pullup)              |      | 1.5    |      | Α      |

| I <sub>DRV-HG-SINK</sub> | current                                 | -LOAD                                               | Sink current (pulldown)              |      | 2.0    |      | Α      |

| R <sub>DS(ON)3</sub>     | Low-side MOSFET driver on-state         | V <sub>DD</sub> = 4.5 V                             | I <sub>LG</sub> = 0.1 A (pullup)     |      | 1.5    |      | Ω      |

| R <sub>DS(ON)4</sub>     | resistance                              | V DD = 4.0 V                                        | $I_{LG} = -0.1 \text{ A (pulldown)}$ |      | 0.9    |      | Ω      |

| I <sub>DRV-LG-SRC</sub>  | Low-side MOSFET driver peak             | C <sub>LOAD</sub> = 3 nF                            | Source current (pullup)              |      | 1.5    |      | Α      |

| I <sub>DRV-LG-SINK</sub> | current                                 | OLOAD = 3 III                                       | Sink current (pulldown)              |      | 2.0    |      | Α      |

| $T_DEAD$                 | Adaptive dead-time                      |                                                     |                                      |      | 15     |      | ns     |

| SOFT-STAR                | т                                       |                                                     |                                      |      |        |      |        |

| I <sub>SS</sub>          | Soft-start source current               | V <sub>SS/TRACK</sub> = 0 V                         |                                      | 1.0  | 3.0    | 5.0  | μΑ     |

| I <sub>SS-PD</sub>       | Soft-start pulldown resistance          | V <sub>SS/TRACK</sub> = 0.6 V                       |                                      |      | 330    |      | Ω      |

| T <sub>SS-INT</sub>      | Internal soft-start timeout             |                                                     |                                      |      | 1.28   |      | ms     |

| POWER GO                 | OD                                      |                                                     | ,                                    |      |        |      |        |

| I <sub>PGS</sub>         | PGOOD low sink current                  | $V_{PGOOD} = 0.2 \text{ V}, V_{FB} = 0.2 \text{ V}$ | ).75 V                               | 70   | 100    |      | μA     |

| I <sub>PGL</sub>         | PGOOD leakage current                   | V <sub>PGOOD</sub> = 5 V                            |                                      |      | 1      | 10   | μA     |

| OVT                      | Overvoltage threshold                   | V <sub>FB</sub> rising, RS tied to GI               | ND                                   | 111% | 116.5% | 123% |        |

| OVT <sub>HYS</sub>       | OVT hysteresis                          | V <sub>FB</sub> falling, RS tied to G               | ND                                   |      | 3.5%   |      |        |

| UVT                      | Undervoltage threshold                  | V <sub>FB</sub> rising, RS tied to GI               | ND                                   | 86%  | 91%    | 97%  |        |

| UVT <sub>HYS</sub>       | UVT hysteresis                          | V <sub>FB</sub> falling, RS tied to G               | ND                                   |      | 4%     |      |        |

| t <sub>deglitch</sub>    | Deglitch time                           | V <sub>PGOOD</sub> rising and falling               |                                      |      | 20     |      | μs     |

| UVLO/ENAB                |                                         |                                                     |                                      |      |        |      |        |

| V <sub>UVLO1</sub>       | Logic low threshold                     | V <sub>UVLO/EN</sub> falling                        |                                      | 0.94 | 0.985  | 1.03 | V      |

| V <sub>UVLO2</sub>       | Logic high threshold                    | V <sub>UVLO/EN</sub> rising                         |                                      | 1.11 | 1.15   | 1.18 | V      |

| V <sub>UVLO-HYS</sub>    | UVLO/EN voltage hysteresis              | V <sub>UVLO/EN</sub> falling                        |                                      | 139  | 165    | 190  | mV     |

| I <sub>UVLO1</sub>       | UVLO/EN pullup current, disabled        | $V_{\text{UVLO/EN}} = 0 \text{ V}$                  |                                      | 0.8  | 1.8    | 2.7  | μA     |

| I <sub>UVLO2</sub>       | UVLO/EN pullup current, enabled         | $V_{UVLO/EN} = 3.25 \text{ V}$                      |                                      | 5.5  | 10.5   | 15.5 | μA     |

|                          | ICHRONIZATION                           | UVLO/EIN                                            |                                      |      |        |      | E, ,   |

| V <sub>IH-SYNC</sub>     | SYNC pin V <sub>IH</sub>                |                                                     |                                      | 2    |        |      | V      |

| V <sub>IL-SYNC</sub>     | SYNC pin V <sub>IL</sub>                |                                                     |                                      |      |        | 0.8  | V      |

| SYNC <sub>FSW-L</sub>    | Minimum clock sync frequency            |                                                     |                                      | 200  |        | 0.0  | kHz    |

| SYNC <sub>FSW-H</sub>    |                                         |                                                     |                                      | 200  |        | 1.2  | MHz    |

| SYNC <sub>I</sub>        | SYNC pin input current                  |                                                     |                                      |      | 1      | 1.2  |        |

|                          | TEMPERATURE SENSE AND THER              | MAI SHITDOWN                                        |                                      |      | ı      |      | μA     |

|                          |                                         | IVIAL SHUTDUVIN                                     | 1                                    |      | 10     |      | ^      |

| I <sub>D+1</sub>         | D+ pin state 1 current                  |                                                     |                                      |      | 10     |      | μA     |

| I <sub>D+2</sub>         | D+ pin state 2 current                  |                                                     |                                      |      | 100    |      | μΑ     |

<sup>(3)</sup> The specified parameter is calculated based on a 2N3904 transistor at 25°C.

<sup>(4)</sup> Multiply by 19.9 to scale from nA/mV to ppm/°C (assumes 2N3904 BJT temperature sensor with ideality factor η =1.004).

# **Electrical Characteristics (continued)**

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over -40°C to +125°C junction temperature range unless otherwise stated<sup>(1)</sup>, <sup>(2)</sup>.  $V_{VIN}$  = 12 V and all parameters at zero power dissipation (unless otherwise noted).

|                       | PARAMETER                                      | TEST CONDITIONS                                                                                                | MIN  | TYP  | MAX  | UNIT  |

|-----------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>OTP</sub>      | Remote thermal current                         | $\Delta V_{BE} = 79.3 \text{ mV}^{(5)}$                                                                        | 13.5 | 14.6 | 15.5 | μΑ    |

| I <sub>OTP-TC</sub>   | I <sub>OTP</sub> temperature coefficient       | Referenced to ΔV <sub>BE</sub> <sup>(4)</sup>                                                                  | 158  | 187  | 213  | nA/mV |

| $V_{TRIP}$            | Remote thermal trip point                      |                                                                                                                |      | 1.15 |      | ٧     |

| V <sub>TRIP-HYS</sub> | Remote thermal trip point hysteresis           |                                                                                                                |      | 80   |      | mV    |

| R <sub>OTP</sub>      | OTP resistance, thermal shutdown               | $R_{OTP(nom)} = 80.7 \text{ k}\Omega, \ \Delta V_{BE} = 79.3 \text{ mV}^{(5)}, \ T_{J} = 125 ^{\circ}\text{C}$ | -5%  |      | 5%   |       |

| T <sub>SHD</sub>      | Internal thermal shutdown threshold            | Rising                                                                                                         |      | 150  |      | ŝ     |

| T <sub>SHD-HYS</sub>  | Internal thermal shutdown threshold hysteresis |                                                                                                                |      | 20   |      | °C    |

<sup>(5)</sup> The specified parameter is calculated based on a 2N3904 transistor at 125°C.

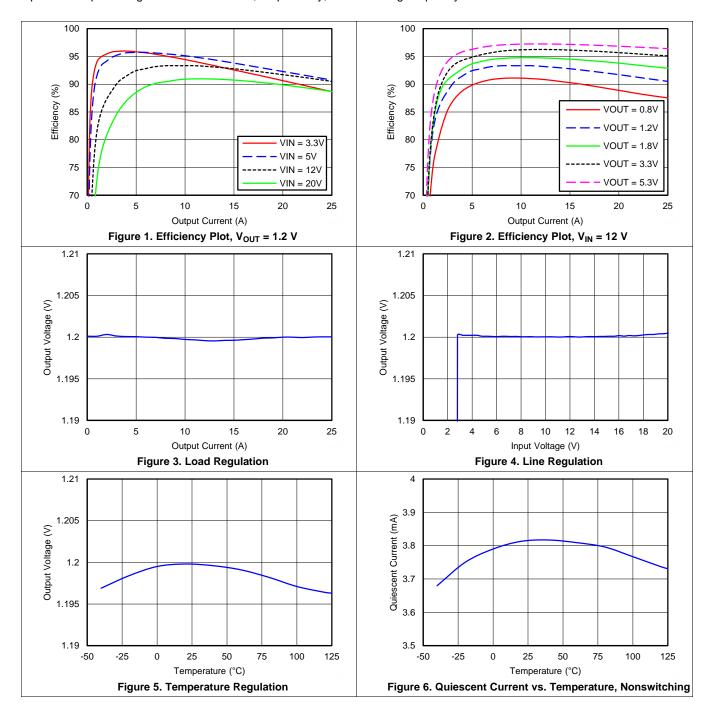

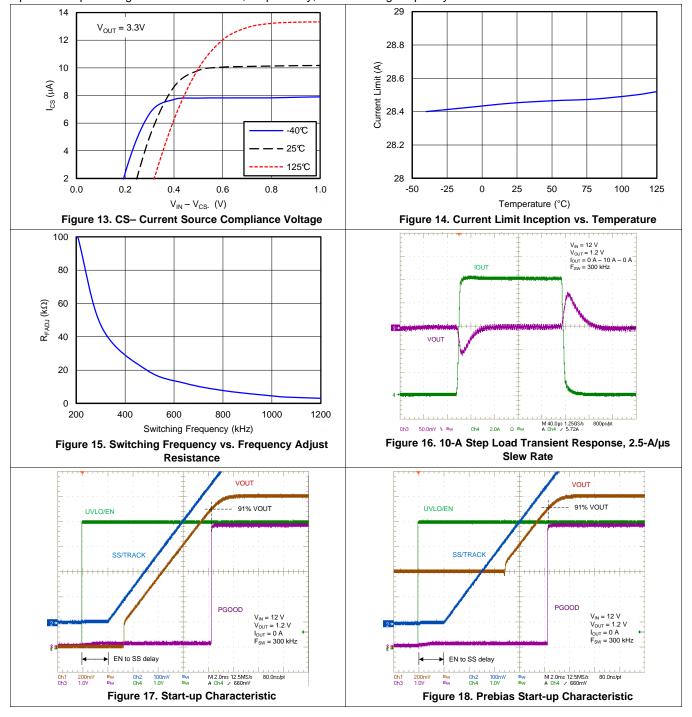

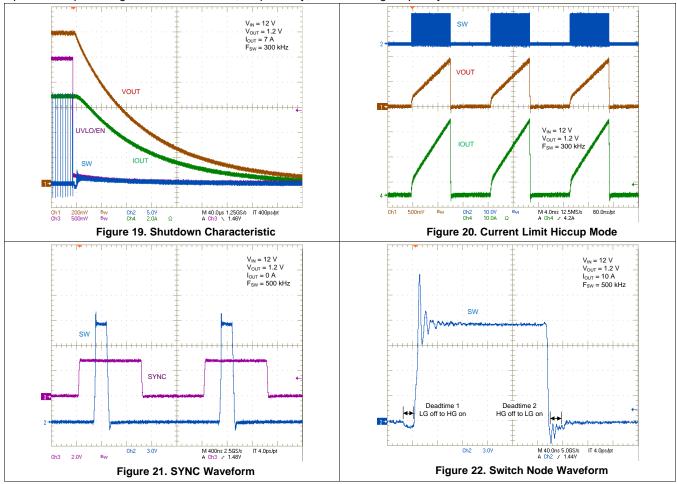

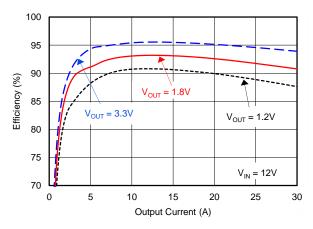

# 7.6 Typical Characteristics

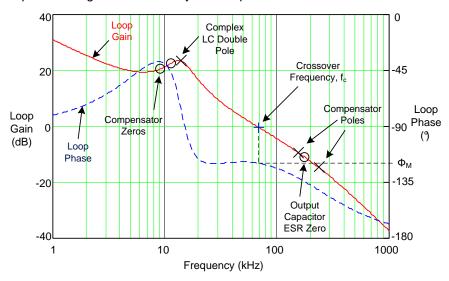

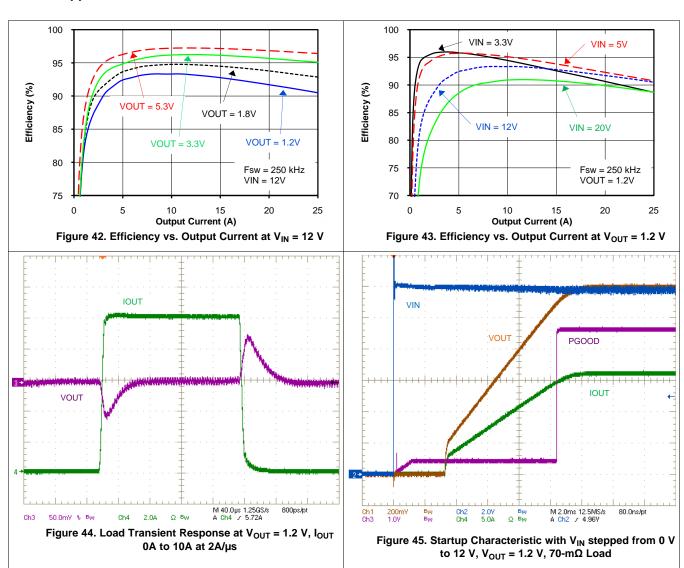

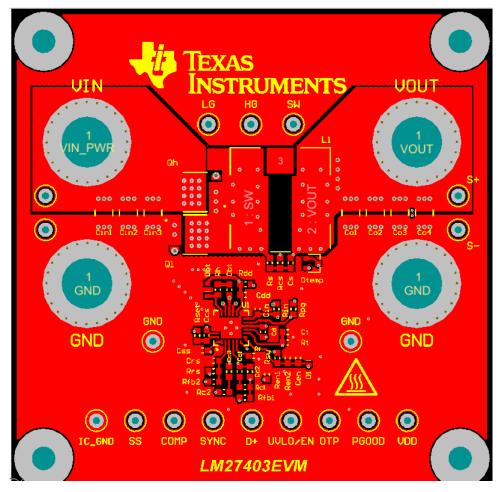

Unless otherwise stated, all datasheet curves were recorded using the circuit and powertrain designated in Figure 41 with input and output voltages of 12 V and 1.2 V, respectively, and switching frequency of 250 kHz.

Copyright © 2013–2014, Texas Instruments Incorporated

Submit Documentation Feedback

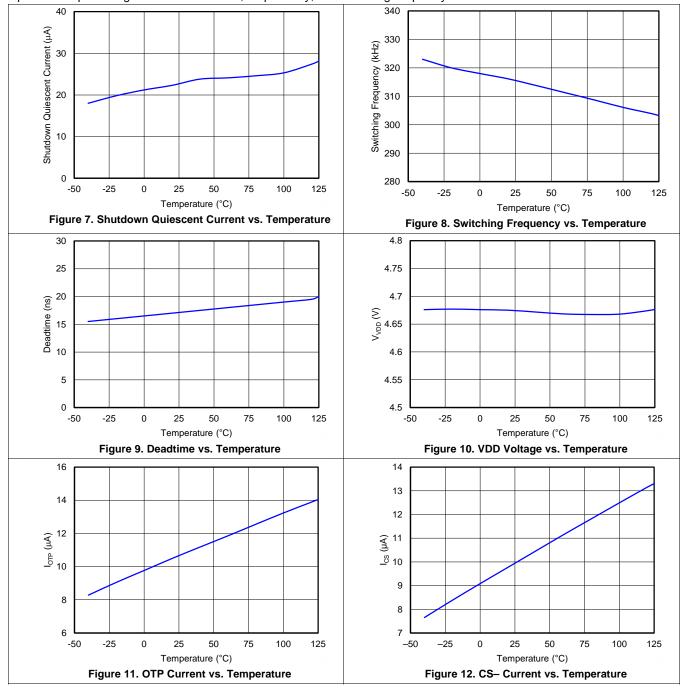

# **Typical Characteristics (continued)**

Unless otherwise stated, all datasheet curves were recorded using the circuit and powertrain designated in Figure 41 with input and output voltages of 12 V and 1.2 V, respectively, and switching frequency of 250 kHz.

Submit Documentation Feedback

Copyright © 2013–2014, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

Unless otherwise stated, all datasheet curves were recorded using the circuit and powertrain designated in Figure 41 with input and output voltages of 12 V and 1.2 V, respectively, and switching frequency of 250 kHz.

Copyright © 2013–2014, Texas Instruments Incorporated

Submit Documentation Feedback

# **Typical Characteristics (continued)**

Unless otherwise stated, all datasheet curves were recorded using the circuit and powertrain designated in Figure 41 with input and output voltages of 12 V and 1.2 V, respectively, and switching frequency of 250 kHz.

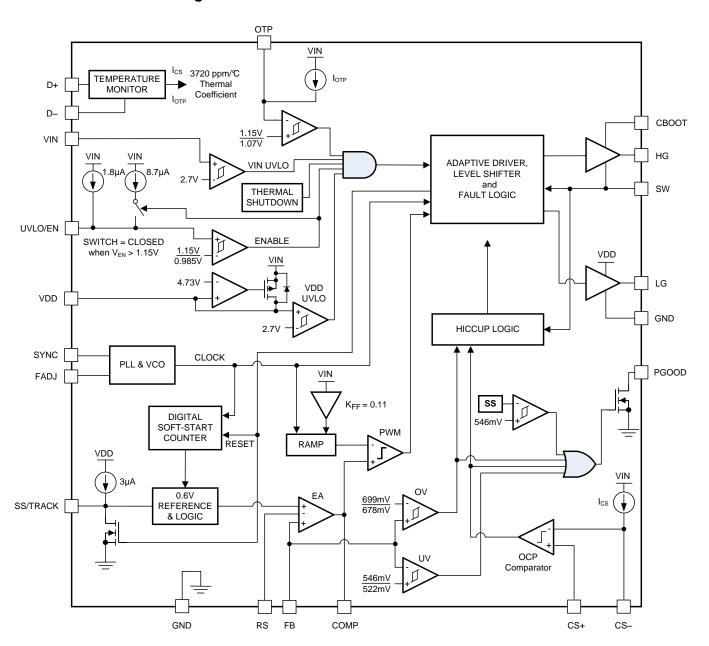

# 8 Detailed Description

#### 8.1 Overview

The distributed power supply architecture, pervasive in myriad applications including communications infrastructure equipment and computing systems, uses an intermediate bus and multiple downstream DC-DC regulators dedicated and proximate to each "point-of-load." The ASICs, FPGAs, and microprocessors that comprise these loads have supply voltage requirements whose levels are decreasing on an absolute basis and whose tolerance bands are decreasing on a percentage basis. The hallmarks of point-of-load (POL) DC-DC regulators are efficiency, size, load transient response, and cost.

To this end, the LM27403 is a feature-rich, easy-to-use, synchronous PWM DC-DC step-down controller capable of providing an ultrahigh current output for demanding, high power density POL applications. An input voltage range of 3 V to 20 V is compatible with a wide range of intermediate bus system rails and battery chemistries; especially 3.3-V, 5-V, and 12-V inputs. The output voltage is adjustable from 0.6 V to as high as 93% of the input voltage, with better than ±1% feedback system regulation accuracy over the full junction temperature range. With an accurate, adjustable and thermally compensated inductor DCR based current limit setpoint, ferrite and composite core inductors with low DCR and small footprint can be specified to maximize efficiency and reduce power loss. High-current gate drivers with adaptive deadtime are used for the high-side and low-side MOSFETs to provide further efficiency gains.

The LM27403 employs a voltage-mode control loop with output voltage remote sense, input voltage feedforward modulation, and a high gain-bandwidth error amplifier to accurately regulate the output voltage over substantial load, line, and temperature ranges. The switching frequency is programmable between 200 kHz and 1.2 MHz through a resistor or an external synchronization signal. The LM27403 is available in a 4-mm × 4-mm, thermally enhanced, 24-lead WQFN PowerPad package. This device offers high levels of integration by including MOSFET gate drivers, a low dropout (LDO) bias supply linear regulator, and comprehensive fault protection features to enable highly flexible, reliable, energy-efficient, and high power density regulator solutions.

Multiple fault conditions are accommodated, including overvoltage, undervoltage, overcurrent, and overtemperature. To improve overcurrent setpoint accuracy and enable easier filter inductor selection, the LM27403 thermally compensates for the temperature coefficient (TC) of the inductor's winding resistance by sensing the inductor temperature with an external NPN transistor configured as a thermal diode. The same thermal diode also monitors the PCB temperature to initiate a thermal shutdown in the event that the sensed temperature exceeds the programmed thermal shutdown setpoint.

### 8.2 Functional Block Diagram

## 8.3 Feature Description

#### 8.3.1 Input Range: VIN

The LM27403 operational input voltage range is from 3 V to 20 V. The device is intended for POL conversions from 3.3-V, 5-V, and 12-V unregulated, semiregulated and fully regulated supply rails. It is also suitable for connection to intermediate bus converters with output rails centered at 12 V and 9.6 V (derived from 4:1 and 5:1 primary-secondary transformer step-downs in nonregulated full-bridge converter topologies) and voltage levels intrinsic to a wide variety of battery chemistries.

The LM27403 uses an internal LDO subregulator to provide a 4.7-V bias rail for the gate drive and control circuits (assuming the input voltage is higher than 4.7 V plus the necessary subregulator dropout specification). Naturally, it can be more favorable to connect VDD directly to the input during low input voltage operation ( $V_{VIN} < 5.5 \text{ V}$ ). In summary, connecting VDD to VIN during low input voltage operation provides a greater gate drive voltage level and thus an inherent efficiency benefit. However, by virtue of the low subregulator dropout voltage, this VDD to VIN connection is not mandatory, thus enabling input ranges from 3 V up to 20 V. The application circuits shown below detail LM27403 configuration options suitable for several input rails.

Figure 23. Schematic Diagram for VIN Operating Range of 3 V to 20 V

Figure 23 shows the schematic diagram for an input voltage ranging from 3 V to 20 V. Note that a finite subregulator dropout voltage exists and is manifested to a larger extent when driving high gate charge ( $Q_G$ ) power MOSFETs at elevated switching frequencies. For example, at  $V_{VIN} = 3$  V, the VDD rail voltage is 2.8 V with a dc operating current,  $I_{VDD}$ , of 40 mA. Such a low gate drive rail may be insufficient to fully enhance the power MOSFET gates. At the very least, MOSFET on-state resistance,  $R_{DS(ON)}$ , increases at such low gate drive levels. Here are the main concerns when operating at a low input voltage:

- Increase of conduction losses (higher R<sub>DS(on)</sub> at lower V<sub>GS</sub>).

- Increase of switching losses associated with sluggish switching times when operating at low V<sub>GS</sub> levels.

- Deadtime may be larger as a result of the lower gate drive level and associated slower gate voltage slew rate.

This may become evident, for example, when using two high-side MOSFETs in a 3.3-V to 2.5-V converter design.

- Dramatic reduction in the range of suitable MOSFETs that a designer can choose from (MOSFETs with  $R_{DS(on)}$  rated at  $V_{GS} = 2.5$  V become mandatory).

Note that the increased on-state resistance is compounded by an increase in MOSFET junction temperature, bearing in mind the negative temperature coefficient of the MOSFET threshold voltage.

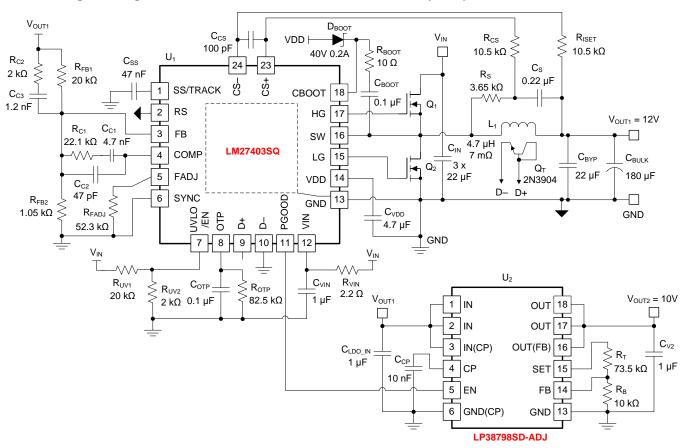

In general, the subregulator is rated to drive the two internal gate driver stages in addition to the quiescent current associated with LM27403 operation. Figure 24 shows the schematic diagram for lower input voltages such as 3.0 V to 5.5 V. The LM27403's VDD and VIN pins can be tied together if the input voltage is guaranteed not to exceed 5.5 V (absolute maximum 6 V). This short bypasses the internal LDO bias regulator and eliminates the LDO dropout voltage and power dissipation. An RC filter from the input rail to the VIN pin, for example 2.2  $\Omega$  and 1  $\mu\text{F}$ , presents supplementary filtering at the VIN pin. Low gate threshold voltage MOSFETs are recommended for this configuration.

Figure 24. Schematic Diagram for VIN Operating Range of 3.0 V to 5.5 V

#### 8.3.2 Output Voltage: FB Voltage and Accuracy

The reference voltage seen at the FB pin is set at 0.6 V, and a feedback system accuracy of  $\pm 1\%$  over the full junction temperature range is met. Junction temperature range for the device is  $-40^{\circ}$ C to  $\pm 125^{\circ}$ C. While somewhat dependent on frequency and load current levels, the LM27403 is generally capable of providing output voltages in the range of 0.6 V to a maximum of greater than 90% VIN. The dc output voltage during normal operation is set by the feedback resistor network,  $R_{FB1}$  and  $R_{FB2}$ , connected to VOUT.

#### 8.3.3 Input and Bias Rail Voltages: VIN and VDD

The LM27403 internal UVLOs ensure that the input rail (VIN) and bias supply rail (VDD) are charged and stable at 2.7 V before switching begins. VDD and VIN have independent UVLO comparators, each with 250 mV of hysteresis. There is a definite delay between UVLO power-on and switching power-on. This delay is related to the fact that the LM27403 does not begin switching until the internal temperature sense circuitry is ready and stabilized. The delay is four measurement cycles on D+, equivalent to 512 clock cycles.

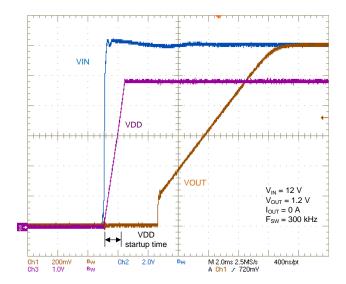

The VDD bias supply LDO has a nominal current limit of 106 mA during normal operation. However, a lower current limit is engaged at startup to control the rate of rise of the VDD voltage. Figure 25 shows the typical scope waveforms of VDD and VOUT when the input voltage is instantaneously applied. Here, the VDD voltage ramps in approximately 1.4 ms based on a 10-µF VDD decoupling capacitor and current-limited VDD feature. For more details, please see the *LM27403 EVM User's Guide*, SNVU233.

Figure 25. Typical Startup Waveforms of VDD and VOUT With Controlled Ramp Rates

#### 8.3.4 Precision Enable: UVLO/EN

The UVLO/EN pin represents a precision analog enable function for user-defined UVLO power-on input voltage levels and to toggle the output on and off. The UVLO/EN pin is essentially a comparator-based input referenced to a flat bandgap voltage with a fixed hysteresis of 165 mV.

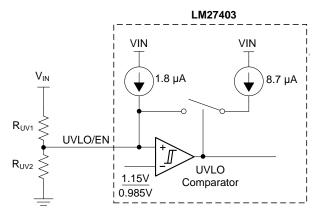

The UVLO/EN pin has an internal pullup current of 1.8  $\mu$ A, as shown in Figure 26. There is also a low I<sub>Q</sub> shutdown mode when UVLO/EN is effectively pulled below a base-emitter voltage drop (approximately 0.7 V at room temperature). This mode shuts down the bias currents of the LM27403, but the UVLO/EN pullup current source is still available. If UVLO/EN is pulled below this hard shutdown threshold, the internal LDO regulator powers off and the VDD rail collapses.

Figure 26. Precision UVLO/Enable Circuit with Hysteretic Comparator and Pullup Current Sources

When the precision enable threshold of 1.15 V is exceeded, the UVLO/EN pullup current source increases from 1.8  $\mu$ A to 10.5  $\mu$ A (that is, an 8.7- $\mu$ A hysteresis current). Use this feature to create a customizable UVLO hysteresis (above the standard 165-mV fixed voltage hysteresis) based on the resistor divider from VIN to turn on and off the LM27403 at the required input voltage levels. Also, use a capacitor from the UVLO/EN pin to GND to implement a fixed time delay in power systems with timed sequencing requirements.

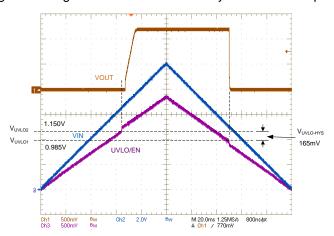

Figure 27 shows an example using the circuit in Figure 23 where the input voltage is ramping from 0 V to 10 V in 100 ms. Here, the UVLO resistors,  $R_{UV1}$  and  $R_{UV2}$ , are respectively set to 47.5 k $\Omega$  and 10 k $\Omega$ . Given these resistances, the typical input UVLO turn-on and turn-off levels are 6.5 V and 5.2 V, respectively. The UVLO/EN pin voltage steps at the rising and falling thresholds are defined by the UVLO/EN pin current hysteresis.

Figure 27. Typical Input Voltage UVLO Turn On and Off Behavior

Given  $V_{IN(on)}$  and  $V_{IN(off)}$  as the input voltage turn-on and turn-off thresholds, respectively, select the UVLO resistors using the following expressions:

$$R_{UV1} = \frac{V_{IN(on)} \frac{V_{UVLO1}}{V_{UVLO2}} - V_{IN(off)}}{I_{UVLO2} - I_{UVLO1} \frac{V_{UVLO1}}{V_{UVLO2}}}$$

$$R_{UV2} = R_{UV1} \frac{V_{UVLO2}}{V_{IN(on)} - V_{UVLO2} + R_{UV1}I_{UVLO1}}$$

(1)

The UVLO/EN pin has a maximum operating voltage rating equal to the input voltage or 5.5V, whichever is lower. Do not exceed this rating. If the input UVLO level is set at low input voltage, it is possible that this maximum UVLO/EN pin voltage could be exceeded at the higher end of the input voltage operating range. In this case, use a small 4.7-V zener diode clamp, designated  $D_{EN}$  in Figure 23, from UVLO/EN to GND, such that the maximum operating level is never exceeded.

#### 8.3.5 Switching Frequency

There are two options for setting the switching frequency of the LM27403, thus providing a power supply designer a level of flexibility when choosing external components for multiple applications. To adjust the frequency, use a resistor from the FADJ pin to GND, or synchronize the LM27403 to an external clock signal through the SYNC pin.

#### 8.3.5.1 Frequency Adjust: FADJ

Adjust the LM27403 free-running switching frequency by using a resistor from the FADJ pin to GND. The switching frequency range of the device is from 200 kHz to 1.2 MHz. An open circuit at the FADJ pin forces the frequency to the minimum value. FADJ shorted moves the frequency to its maximum value. The frequency set resistance,  $R_{\text{FADJ}}$ , is governed by Equation 3.

$$R_{\text{FADJ}}[k\Omega] = \frac{10000}{F_{\text{sw}}[k\text{Hz}]^{0.99} - 100} - 7$$

(3)

E96 resistors for common switching frequencies are given in Table 1.

Submit Documentation Feedback

| SWITCHING FREQUENCY (kHz) | FREQUENCY SET RESISTANCE (kΩ) |

|---------------------------|-------------------------------|

| 215                       | 95.3                          |

| 250                       | 68.1                          |

| 300                       | 47.5                          |

| 500                       | 20                            |

| 600                       | 15                            |

| 800                       | 7.5                           |

| 1050                      | 4.12                          |

| 1200                      | 2.87                          |

# 8.3.5.2 Clock Synchronization: SYNC

Apply an external clock synchronization signal to the LM27403 to synchronize switching in both frequency and phase. Requirements for the clock SYNC signal are:

- Clock SYNC range: 200 kHz to 1.2 MHz

- SYNC frequency range from the FADJ frequency: up to 400 kHz (up only)

In applications where the external clock is not applied to the LM27403, use the external FADJ resistor to set the minimum switching frequency. When the external clock is applied, it takes precedence only if the switching frequency is greater than that set by the FADJ resistor. When the external clock is disconnected, the LM27403 switching frequency does not decrease below the minimum frequency set by the resistor. Setting a minimum frequency in this way prevents the inductor ripple current from increasing dramatically. Externally tie SYNC to GND if synchronization functionality is not required. The SYNC logic thresholds are based on an NMOS threshold referenced to GND and, as such, are effectively independent of the VDD operating voltage.

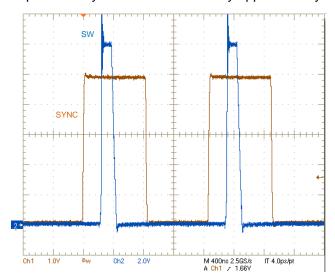

Figure 28 shows a SYNC TTL signal at 600 kHz and the corresponding SW node waveform ( $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 1.2 \text{ V}$ , free-running frequency = 250 kHz). The synchronization is with respect to the rising edge of SYNC. The rising edge of the SW voltage is phase delayed relative to SYNC by approximately 250 ns.

Figure 28. Typical 600-kHz SYNC Waveform

#### 8.3.6 Temperature Sensing: D+ and D-

The LM27403 PWM controller offers low-cost programmable thermal protection by using remote thermal diode temperature measurements based on the change in forward bias voltage of a diode when operated at two different currents. The thermal diode is a discrete small-signal 2N3904 type silicon NPN BJT located (in good thermal contact) adjacent the filter inductor.

The ideality factor is a parameter in the diode I-V relationship that approaches 1.0 or 2.0 as carrier diffusion or recombination current dominate current flow, respectively. The ideality factor for 2N3904 type diode-connected BJTs available from several manufacturers is typically 1.004. Note that 3-terminal BJTs such as the 2N3904 are vastly preferred over true 2-terminal diodes in this application. Discrete 2-terminal diodes with current largely dictated by recombination have a much higher ideality factor ( $\eta = 1.2$  to 1.5) than BJTs and, to such an extent, would cause unacceptable temperature measurement error.

Switched capacitor technology is integrated in the LM27403 to sample and measure the base-emitter voltages created by respective 10- $\mu$ A and 100- $\mu$ A bias currents flowing from the D+ to D- pins. The difference in these voltages, termed  $\Delta V_{BE}$ , is readily extracted and the sensed temperature is calculated noting that  $\Delta V_{BE}$  is directly proportional to temperature as follows:

$$V_{BE(high)} - V_{BE(low)} = \frac{\eta kT}{q} ln \Biggl( \frac{I_{high}}{I_{low}} \Biggr)$$

#### where

- k = Boltzmann's constant, 1.3806488 x 10<sup>-23</sup>J/K (Joules/Kelvin)

- T = absolute temperature in Kelvin (K)

- q = electron charge = 1.602176 x 10<sup>-19</sup> C (Coulombs)

- η = diode ideality factor = 1.004

- I<sub>low</sub> = bias current in state 1 = 10 μA

- I<sub>high</sub> = bias current in state 2 = 100 μA

(4)

The source currents from the D+ pin during state 1 and state 2 are 10  $\mu$ A and 100  $\mu$ A, respectively. The sensed temperature in Kelvin becomes:

$$T = \frac{q\Delta V_{BE}}{\eta k \ln(10)} \tag{5}$$

Figure 29 shows the 2N3904  $V_{BE}$  voltage at ambient temperatures of -40°C, 25°C and 125°C. The low and high states in  $V_{BE}$  voltage correspond to the 10- $\mu$ A and 100- $\mu$ A currents sourced from D+, each of 64 clock cycle duration. The voltage level is sampled at the end of each state. While the dc level of the  $V_{BE}$  voltage decreases logarithmically with increasing temperature, the  $\Delta V_{BE}$  amplitude increases with and is directly proportional to temperature according to Equation 5.

Figure 29. Typical 2N3904 Base-Emitter Voltage at -40°C, 25°C and 125°C

Note that D- is essentially a kelvin connection to the remote thermal diode. As such, the D- pin needs to be tied to GND at the LM27403; the D- trace should not connect to any of the PCBs current-carrying ground planes.

#### 8.3.7 Thermal Shutdown: OTP

A current proportional to the sensed temperature is sourced from the OTP pin. The resultant voltage at the OTP pin (set by a resistor connected from OTP to GND) is compared to an internal shutdown threshold of 1.15 V with 80-mV hysteresis. When the threshold is exceeded, the device stops switching until the sensed temperature drops to a level where the OTP pin voltage falls to the restart threshold. The external thermal protection is disabled by grounding the OTP pin. The thermal shutdown setpoint is governed by Equation 6:

$$R_{OTP} = R_{OTP(125^{\circ}C)} \frac{398}{T_{OTP}(^{\circ}C) + 273}$$

where

- R<sub>OTP</sub> is the required resistance at the OTP pin for the desired thermal shutdown temperature

- $R_{OTP(125^{\circ}C)}$  is the nominal resistance at the OTP pin , 80.7 k $\Omega$ , for 125°C thermal shutdown, and

- T<sub>OTP</sub> is the desired thermal shutdown temperature.

For example, the OTP resistor required for a thermal shutdown setpoint of 105°C is calculated as shown in Equation 7:

$$R_{OTP} = 80.7 \text{ k}\Omega \frac{398}{105 + 273} = 85 \text{ k}\Omega \tag{7}$$

A 100-nF capacitor connected in parallel with  $R_{OTP}$  is required. When the IC detects an overtemperature event, it responds with the normal hiccup-mode sequence of events when going into shutdown. More specifically, the following steps occur when an internal or external OTP event is detected:

- 1. The high-side MOSFET immediately turns off.

- 2. An internal zero-cross circuit is enabled to detect whether the inductor current is positive or negative:

- (a) If the current is negative, the low-side MOSFET immediately turns off.

- (b) If the current is positive, the low-side MOSFET turns off when the inductor current ramps down to zero.

Note that it is important to prevent water-soluble flux residues from contaminating the PCB during the manufacturing process. Contaminants such as these can result in unexpected leakage currents and consequent temperature-measurement errors.

#### 8.3.8 Inductor-DCR-Based Overcurrent Protection

The LM27403 exploits the filter inductor DCR to detect overcurrent events. This technique enables lossless and continuous monitoring of the output current using an RC sense network in parallel with the inductor. DCR current sensing allows the system designer to use inductors specified with low tolerance DCRs to improve the current limit setpoint accuracy. A dc current limit setpoint accuracy within the range of 10% to 15% is easily achieved using inductors with low DCR tolerances.

#### 8.3.9 Current Sensing: CS+ and CS-

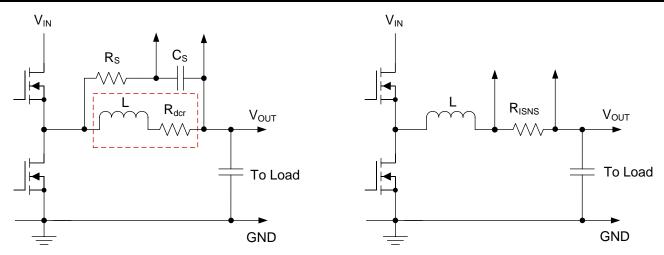

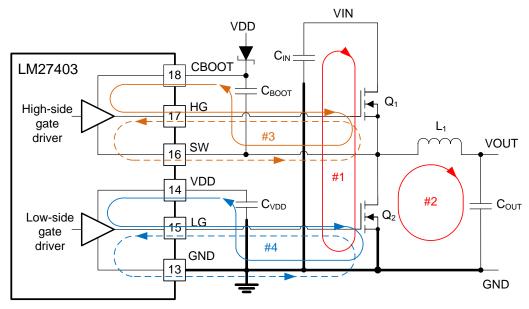

As mentioned, the LM27403 implements an inductor DCR lossless current sense scheme designed to provide both accurate overload (current limit) and short-circuit protection. Figure 30 shows the popular inductor DCR current sense method. Figure 31 shows an implementation with current shunt resistor, R<sub>ISNS</sub>.

Components  $R_S$  and  $C_S$  in Figure 30 create a low-pass filter across the inductor to enable differential sensing of the inductor DCR voltage drop. When  $R_SC_S$  is equal to  $L/R_{dcr}$ , the voltage developed across the sense capacitor,  $C_S$ , is a replica of the inductor DCR's voltage waveform. Choose the capacitance of  $C_S$  greater than 0.1  $\mu$ F to maintain low impedance of the sense network, thus reducing the susceptibility of noise pickup from the switch node.

(8)

Figure 30. Current Sensing Using Inductor DCR

Figure 31. Current Sensing Using Shunt Resistor

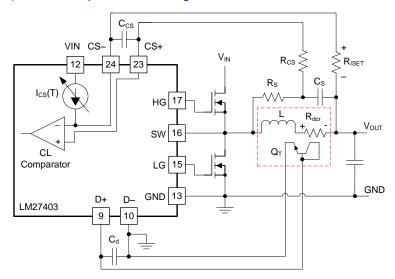

The current limit circuit arrangement is portrayed in Figure 32. The current limit setpoint is set by a single external resistor, R<sub>ISET</sub>, connected from the CS- pin to the output voltage terminal. The current sourced from CS- in combination with this series resistance sets the reference voltage to the current limit comparator, as governed by Equation 8.

$$R_{ISET} = \frac{R_{dcr} \left( I_{OCP} + \frac{\Delta i_L}{2} \right)}{I_{CS}}$$

where

- I<sub>CS</sub> is the CS- pin current, 9.9 μA typically at 25°C

- I<sub>OCP</sub> is the dc overcurrent protection setpoint, and

- Δi<sub>I</sub> is the peak-to-peak inductor ripple current.

Inductor DCR temperature compensation is automatically provided using the remote-diode sensed temperature. The temperature coefficient (TC) of the inductor winding resistance is typically 3720 ppm/°C. The current-limit setpoint is maintained essentially constant over temperature by the slope of CS– pin current over temperature. An increase in sensed DCR voltage associated with an increase of inductor winding temperature is matched by a concomitant increase in current limit comparator reference voltage. The inductor temperature is measured by placing an external diode-connected 2N3904 discrete NPN transistor, designated Q<sub>T</sub> in Figure 32, in close proximity to the inductor (see the *Temperature Sensing: D+ and D-* section for more details).

Figure 32. Current-Limit Setpoint Defined by Current Source I<sub>CS</sub> and Resistor R<sub>ISET</sub>

22

Submit Documentation Feedback

Note that the inductor DCR is shown schematically as a discrete element in Figure 30 and Figure 32. The current-sense comparator inputs operate at common mode up to the input rail voltage. The comparator incorporates a very low input-referred offset to reduce the SNR of the voltage detected across the inductor DCR. The CS- pin current is specified down to a headroom compliance voltage of less than 0.8 V (that is,  $V_{VIN} - V_{CS-}$ ) and over the full operating temperature range (see the *Electrical Characteristics* Table and Figure 13). The current source is powered from the input to allow the current limit circuit to work in high duty cycle applications.

With power inductors selected to provide lowest possible DCR to minimize power losses, the typical DCR ranges from  $0.4~\text{m}\Omega$  to  $4~\text{m}\Omega$ . Then, given a load current of 25 A, the voltage presented across the CS+ and CS- pins ranges between 10 mV and 100 mV. Note that this small differential signal is superimposed on a large common-mode signal that is the dc output voltage, which makes the current sense signal challenging to process. To aid in rejection of high frequency common-mode noise, a series resistor,  $R_{CS}$ , of same resistance as  $R_{ISET}$ , is added to the CS+ signal path as shown in Figure 32. A small capacitor,  $C_{CS}$ , added across CS+ and CS- provides differential filtering.

A current sense (or current shunt) resistor in series with the inductor can also be implemented at lower output current levels to provide accurate overcurrent protection, see Figure 31. Burdened by the unavoidable efficiency penalty and/or additional cost implications, this configuration is not usually implemented in high-current applications (except where OCP setpoint accuracy and stability over the operating temperature range are critical specifications). However, if a shunt resistor is used, temperature compensation is not required. In this case, short the D+ to D- pins to disable this function. The current sourced from CS- in this case becomes 5  $\mu$ A (typical) and is independent of temperature.

In the PCB layout, component pads are recommended to install a small capacitor, designated  $C_d$  in Figure 32, between the D+ and D- pins as close to the LM27403 as possible. This capacitor should not exceed 1 nF for 2N3904-type devices. Locate an additional capacitor, typically 100 pF, at the BJT, when operating in noisy environments (for example, where leakage flux from the airgap of a ferrite inductor may couple into the adjacent circuit board traces).

### 8.3.10 Current Limit Handling

The LM27403 implements a *hiccup* mode to allow the device to cool down during overcurrent events. If five overcurrent events are detected during any 32 clock cycle interval, the LM27403 shuts down and stops switching for a period of 5 ms. During this time, negative inductor current is not allowed, and the output cannot swing negative. After 5 ms, the LM27403 starts up in the normal startup routine at an output voltage ramp rate determined by the internal soft-start function or the external soft-start capacitor (if one is used). With each detected current limit event, the high-side MOSFET is turned off and the low-side MOSFET is turned on.

#### 8.3.11 Soft-Start: SS/TRACK

After the UVLO/EN pin exceeds the rising threshold of 1.15 V, the LM27403 begins charging the output to the dc level dictated by the feedback resistor network. The LM27403 features an adjustable soft-start (set by a capacitor from the SS/TRACK pin to GND) that determines the charging time of the output. A 3- $\mu$ A current source charges this soft-start capacitor. Soft-start limits inrush current as a result of high output capacitance and avoids an overcurrent condition. Stress on the input supply rail is also reduced. The soft-start time, t<sub>SS</sub>, for the output voltage to ramp to its nominal level is set by Equation 9:

$$t_{SS} = \frac{C_{SS} \ V_{REF}}{I_{SS}}$$

where

- C<sub>SS</sub> is the soft-start capacitance

- V<sub>REF</sub> is the 0.6-V reference, and

- I<sub>SS</sub> is the 3-μA current sourced from the SS/TRACK pin.

If a soft-start capacitor is not used, then the LM27403 defaults to a minimum internal soft-start time of 1.28 ms and provides a resolution of 128 steps. Thus, the internal soft-start dictates the fastest startup time for the circuit.

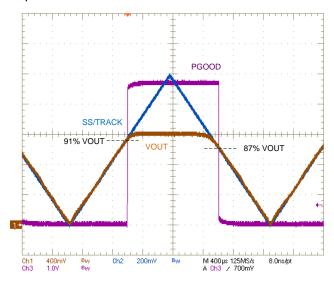

When the SS/TRACK voltage exceeds 91% of the reference voltage, the Power Good flag transitions high. Conversely, the Power Good flag goes low when the SS/TRACK voltage goes below 87% of the reference.

Product Folder Links: LM27403

(9)

#### 8.3.11.1 Tracking

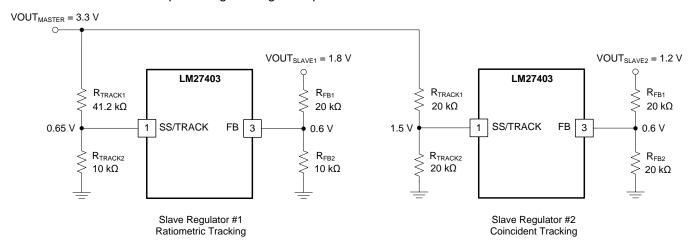

The SS/TRACK pin also doubles as a tracking pin when master-slave power-supply tracking is required. This tracking is achieved by simply dividing down the master's output voltage with a simple resistor network. Coincident, ratiometric, and offset tracking modes are possible.

If an external voltage source is connected to the SS/TRACK pin, the external soft-start capability of the LM27403 is effectively disabled (the internal soft-start is still enabled). The regulated output voltage level is reached when the SS/TRACK pin reaches the 0.6-V reference voltage level. It is the responsibility of the system designer to determine if an external soft-start capacitor is required to keep the device from entering current limit during a startup event. Likewise, the system designer must also be aware of how fast the input supply ramps if the tracking feature is enabled.

Figure 33 shows a triangular voltage signal directly driving SS/TRACK and the corresponding output voltage tracking response. Nominal output voltage here is 1.2 V, with channel scales chosen such that the waveforms overlap during tracking. As expected, the PGOOD flag transitions at thresholds of 91% (rising) and 87% (falling) of the nominal output voltage setpoint.

Figure 33. Typical Output Voltage Tracking Waveforms and PGOOD Flag

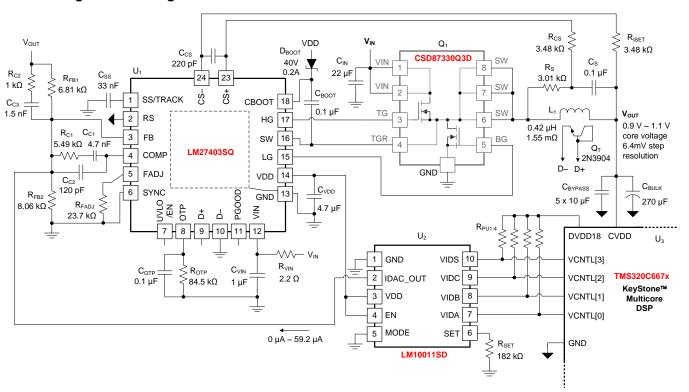

Two practical tracking configurations, ratiometric and coincident, are shown in Figure 34. The most common application is coincident tracking, used in core vs. I/O voltage tracking in DSP and FPGA implementations. Coincident tracking forces the master and slave channels to have the same output voltage ramp rate until the slave output reaches its regulated setpoint. Conversely, ratiometric tracking sets the slave's output voltage to a fraction of the master's output voltage during startup.

Figure 34. Tracking Implementation With Master, Ratiometric Slave and Coincident Slave Rails

For coincident tracking, connect the slave regulator's SS/TRACK input to a resistor divider from the master's output voltage that is the same as the divider used on the slave's FB pin. In other words, simply select  $R_{TRACK1} = R_{FB1}$  and  $R_{TRACK2} = R_{FB2}$  as shown in Figure 34. As the master voltage rises, the slave voltage rises identically. Eventually, the slave voltage reaches its regulation voltage, at which point the internal reference takes over the regulation while the SS/TRACK input continues to increase, thus removing itself from changing the output voltage.

In all cases, to ensure that the output voltage accuracy is not compromised by the SS/TRACK voltage being too close to the 0.6-V reference voltage, the final value of the slave's SS/TRACK voltage should be at least 20 mV above FB.

#### 8.3.12 Monotonic Startup

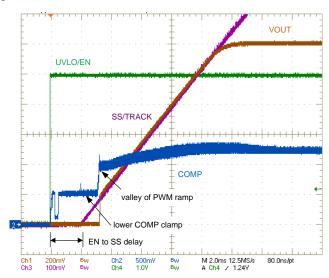

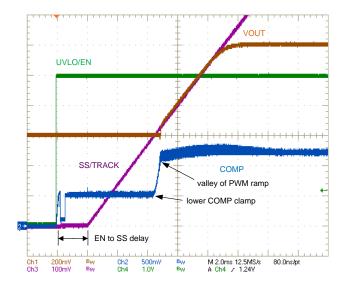

The LM27403 has monotonic startup capability with no dips or flat spots in the output voltage waveform during startup (including prebiased startup) and fault recovery. During the soft-start interval, FB follows SS/TRACK, and the output voltage linearly increases to the nominal output setpoint. Figure 35 illustrates the output voltage behavior during a monotonic startup to a nominal level of 1.2V. The UVLO/EN pin is driven high by a TTL logic signal. As mentioned previously, the startup time is determined by the use of an external soft-start capacitor at the SS/TRACK pin charged by an internally generated 3-µA constant current source. If a soft-start capacitor is not used, the device automatically enables the internal 7-bit (128 step) digital soft-start. The PGOOD flag transitions high when FB reaches its 91% threshold. As described previously, there is a calibration interval based on four cycles on the D+ pin (that is, 512 clock cycles) that creates a delay from UVLO/EN crossing its precision threshold to SS/TRACK being released.

Figure 35. Typical Monotonic Output Voltage Startup Waveforms, 1.2-V Output

#### 8.3.13 Prebias Startup

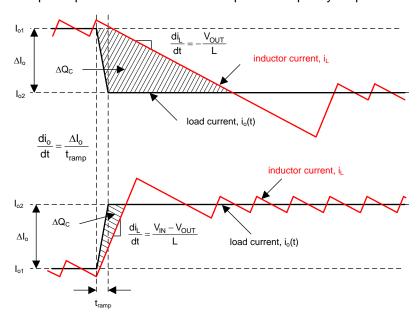

In certain applications, the output voltage may have an initial voltage prebias before the LM27403 is powered on or enabled. The LM27403 is able to startup into a prebiased load while maintaining a monotonic output voltage startup characteristic.