# LM3535 Multi-Display LED Driver with Ambient Light Sensing and Dynamic Backlight Control Compatibility

Check for Samples: LM3535

# FEATURES

- Drives Up to 8 LEDs With Up to 25mA of Diode Current Each

- External PWM Input For Dynamic Backlight Control

- Multi-Zone Ambient Light Sensing (ALS)

- Dual-ALS Sensor Inputs (LM3535-2ALS Only)

- ALS Interrupt Reporting

- Independent On/Off Control for All Current Sinks

- 128 Exponential Dimming Steps with 600:1 Dimming Ratio for Group A (Up to 6 LEDs)

- 8 Linear Dimming States for Groups B (Up to 3 LEDs) and D1C (1 LED)

- Programmable Auto-Dimming Function

- Up to 90% Efficiency

- 0.55% Accurate Current Matching

- Internal Soft-Start Limits Inrush Current

- True Shutdown Isolation for LEDs

- Wide Input Voltage Range (2.7V to 5.5V)

- Active High Hardware Enable

- Total Solution Size < 16mm<sup>2</sup>

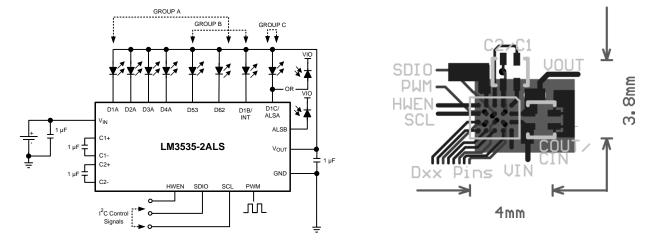

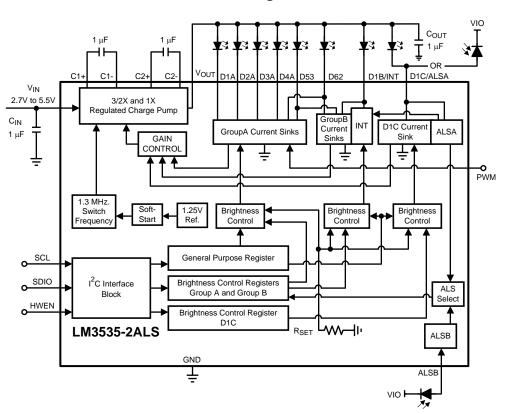

# **Typical Application Circuit**

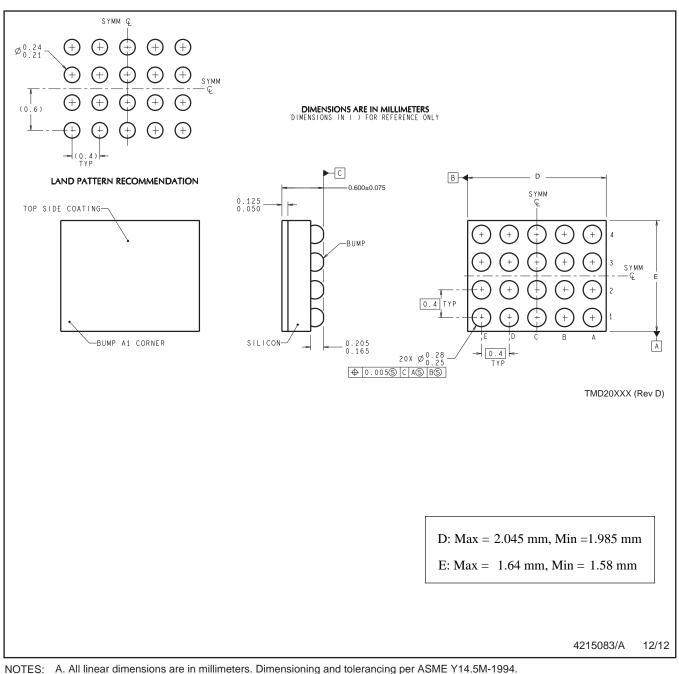

#### Low Profile 20 Bump DSBGA Package (1.650mm × 2.055mm × 0.6mm)

# **APPLICATIONS**

- Smart-Phone LED Backlighting

- Large Format LCD Backlighting

- General LED Lighting

# DESCRIPTION

The LM3535 is a highly integrated LED driver capable of driving 8 LEDs in parallel for large display applications. Independent LED control allows for a subset of the 6 main display LEDs to be selected for partial illumination applications. In addition to the main bank of 6, the LM3535 is capable of driving an additional 2 independently controlled LEDs to support Indicator applications.

The LED driver current sinks are split into three independently controlled groups. The primary group can be configured to drive up to six LEDs for use in the main phone display. Groups B and C are provided for driving secondary displays, keypads and indicator LEDs. All of the LED current sources can be independently turned on and off providing flexibility to address different application requirements.

Figure 1.

Figure 2. Minimum Layout

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION (CONTINUED)**

The LM3535 provides multi-zone Ambient Light Sensing (1 or 2 ALS inputs depending on option) allowing autonomous backlight intensity control in the event of changing ambient light conditions. A PWM input is also provided to give the user a means to adjust the backlight intensity dynamically based upon the content of the display.

The LM3535 provides excellent efficiency without the use of an inductor by operating the charge pump in a gain of 3/2 or in Pass-Mode. The proper gain for maintaining current regulation is chosen, based on LED forward voltage, so that efficiency is maximized over the input voltage range.

The LM3535 is available in a tiny 20-bump, 0.4mm pitch, thin DSBGA package.

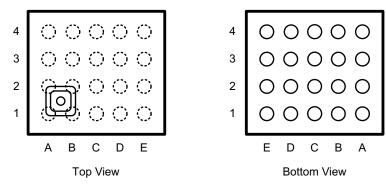

# **Connection Diagram**

#### Figure 3. 20 Bump DSBGA Package Package Number YFQ0020

| Bump Number    | Pin Names                                | Pin Descriptions                                                                                                                                                                                                   |

|----------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3             | V <sub>IN</sub>                          | Input voltage. Input range: 2.7V to 5.5V.                                                                                                                                                                          |

| A2             | V <sub>OUT</sub>                         | Charge Pump Output Voltage                                                                                                                                                                                         |

| A1, C1, B1, B2 | C1+, C1-, C2+, C2-                       | Flying Capacitor Connections                                                                                                                                                                                       |

| D3, E3, E4, D4 | D1A-D4A                                  | LED Drivers - GroupA                                                                                                                                                                                               |

| C4, B4         | D53, D62                                 | LED Drivers - Configurable Current Sinks. Can be assigned to GroupA or GroupB                                                                                                                                      |

| В3             | D1B / INT                                | LED Driver/ ALS Interrupt - GroupB Current Sink or ALS Interrupt Pin. In ALS Interrupt mode, a pull-up resistor is required. A '0' means a change has occurred, while a '1' means no ALS adjustment has been made. |

| C3             | D1C / ALS                                | LED Driver / ALS Input - Indicator LED current sink or Ambient Light Sensor Input                                                                                                                                  |

| D2             | PWM                                      | External PWM Input - Allows the current sinks to be turned on and off at a frequency and duty cycle externally controlled. Minimum On-Time Pulse Width = 15µsec.                                                   |

| E1             | HWEN                                     | Hardware Enable Pin. High = Normal Operation, Low = RESET                                                                                                                                                          |

| C2             | SDIO                                     | Serial Data Input/Output Pin                                                                                                                                                                                       |

| E2             | SCL                                      | Serial Clock Pin                                                                                                                                                                                                   |

| A4             | GND<br>(LM3535)<br>ALSB<br>(LM3535-2ALS) | Ground for LM3535 or Ambient Light Sensor B for LM3535-2ALS                                                                                                                                                        |

| D1             | GND                                      | Ground                                                                                                                                                                                                             |

#### **PIN DESCRIPTIONS**

# Absolute Maximum Ratings<sup>(1)(2)(3)</sup>

| V                                           |                                                 |                    |  |

|---------------------------------------------|-------------------------------------------------|--------------------|--|

| V <sub>IN</sub> pin voltage                 | V <sub>IN</sub> pin voltage                     |                    |  |

| SCL, SDIO, HWEN, PWM pin voltages           | -0.3V to (V <sub>IN</sub> +0.3V)<br>w/ 6.0V max |                    |  |

| I <sub>Dxx</sub> Pin Voltages               | • Voltages -0.3V to (V                          |                    |  |

| Continuous Power Dissipation <sup>(4)</sup> |                                                 | Internally Limited |  |

| Junction Temperature (T <sub>J-MAX</sub> )  |                                                 | 150°C              |  |

| Storage Temperature Range                   |                                                 | -65°C to +150° C   |  |

| Maximum Lead Temperature (Soldering)        |                                                 | See <sup>(5)</sup> |  |

| ESD Rating                                  | Human Body Model <sup>(6)</sup>                 | 2.0kV              |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pins.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 150^{\circ}C$  (typ.) and disengages at  $T_J = 125^{\circ}C$  (typ.).

- (5) For detailed soldering specifications and information, please refer to Application Note 1112 (SNVA009): DSBGA Wafer Level Chip Scale Package.

- (6) The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. (MIL-STD-883 3015.7)

### Operating Rating<sup>(1)(2)</sup>

| Input Voltage Range                                        | 2.7V to 5.5V    |

|------------------------------------------------------------|-----------------|

| LED Voltage Range                                          | 2.0V to 4.0V    |

| Junction Temperature (T <sub>J</sub> ) Range               | -30°C to +110°C |

| Ambient Temperature (T <sub>A</sub> ) Range <sup>(3)</sup> | -30°C to +85°C  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pins.

(3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 110°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

#### **Thermal Properties**

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), DSBGA Package <sup>(1)</sup> | 40°C/W |

|----------------------------------------------------------------------------------------|--------|

|----------------------------------------------------------------------------------------|--------|

(1) Junction-to-ambient thermal resistance is highly dependent on application and board layout. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design. For more information, please refer to Application Note AN-1112 (SNVA009): DSBGA Wafer Level Chip Scale Package.

SNVS598A - AUGUST 2010 - REVISED MAY 2013

#### SNVS598A - AUGUST 2010 - REVISED MAY 2013

### Electrical Characteristics<sup>(1)(2)</sup>

Limits in standard typeface are for  $T_A = 25^{\circ}$ C, and limits in boldface type apply over the full operating temperature range (-30°C to +85°C). Unless otherwise specified:  $V_{IN} = 3.6$ V;  $V_{HWEN} = V_{IN}$ ;  $V_{PWM} = 0$ V; $V_{DxA} = V_{DxB} = V_{DxC} = 0.4$ V; GroupA = GroupB = GroupC = Fullscale Current; ENxA, ENxB, ENxC Bits = "1"; 53A, 62A Bits = "0"; C1 = C2 = C<sub>IN</sub> = C<sub>OUT</sub> = 1.0 $\mu$ F.<sup>(3)</sup>

| Symbol                     | Parameter                                                       | Con                                                                                             | Condition               |                 |                 |                 | Units     |

|----------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------|-----------------|-----------------|-----------------|-----------|

|                            | Output Current Regulation                                       | $2.7V \le V_{IN} \le 5.5V$<br>EN1A to EN4A = '1', 53<br>EN62 = ENxB = ENxC<br>4 LEDs in GroupA  | 23.6<br>(-5.6%)         | 25              | 26.3<br>(+5.2%) | mA<br>(%)       |           |

|                            | GroupA                                                          | $2.7V \le V_{IN} \le 5.5V$<br>EN1A to EN4A = EN53<br>62A = '1'', ENxB = ENx<br>6 LEDs in GroupA |                         | 23.2<br>(-7.2%) | 25              | 26.3<br>(+5.2%) | mA<br>(%) |

| I <sub>Dxx</sub>           | Output Current Regulation<br>GroupB                             | $2.7V \le V_{IN} \le 5.5V$<br>EN1B = EN53 = EN62<br>ENxA = ENC = '0'<br>3 LEDs in GroupB        | = '1', 53A = 62A = '0', | 23.3<br>(-6.8%) | 25              | 26.0<br>(+4.0%) | mA<br>(%) |

|                            | Output Current Regulation<br>IDC                                | 2.7V ≤ V <sub>IN</sub> ≤ 5.5V<br>ENC = '1', ENxA = ENx                                          | xB = '0'                | 23.8<br>(-4.8%) | 25              | 26.8<br>(+7.2%) | mA<br>(%) |

|                            |                                                                 |                                                                                                 |                         |                 |                 |                 |           |

|                            | Output Current Regulation<br>GroupA, GroupB, and GroupC Enabled | $\begin{array}{l} 3.2V \leq V_{IN} \leq 5.5V \\ V_{LED} = 3.6V \end{array}$                     |                         |                 | 25<br>DxB       |                 | mA        |

|                            |                                                                 |                                                                                                 |                         | 25<br>DxC       |                 |                 |           |

|                            | LED Current Matching <sup>(4)</sup>                             |                                                                                                 | GroupA (4 LEDs)         |                 | 0.25            | 2.40            | %         |

| I <sub>Dxx-</sub><br>MATCH |                                                                 | $2.7 V \leq V_IN \leq 5.5 V$                                                                    | GroupA (6 LEDs)         |                 | 0.55            | 2.78            |           |

| MATCH                      |                                                                 |                                                                                                 |                         | 0.25            | 2.41            |                 |           |

| V <sub>DxTH</sub>          | V <sub>Dxx</sub> 1x to 3/2x Gain Transition<br>Threshold        | $V_{\text{DxA}}$ and/or $V_{\text{DxB}}$ Fallir                                                 | ng                      |                 | 130             |                 | mV        |

| V <sub>HR</sub>            | Current sink Headroom Voltage<br>Requirement <sup>(5)</sup>     | I <sub>Dxx</sub> = 95% ×I <sub>Dxx</sub> (nom.<br>(I <sub>Dxx</sub> (nom) = 25mA)               | )                       |                 | 100             |                 | mV        |

| D                          | Open-Loop Charge Pump Output                                    | Gain = 3/2                                                                                      |                         |                 | 2.4             |                 | Ω         |

| R <sub>OUT</sub>           | Resistance                                                      | Gain = 1                                                                                        |                         |                 | 0.5             |                 | 32        |

| lq                         | Quiescent Supply Current                                        | Gain = 3/2, No Load                                                                             |                         |                 | 2.86            | 4.38            | mA        |

| ιQ                         |                                                                 | Gain = 1, No Load                                                                               |                         | 1.09            | 2.31            | ШA              |           |

| I <sub>SB</sub>            | Standby Supply Current                                          | $2.7V \le V_{IN} \le 5.5V$<br>HWEN = $V_{IN}$ , All ENx b                                       |                         | 1.7             | 4.0             | μA              |           |

| I <sub>SD</sub>            | Shutdown Supply Current                                         | $2.7V \le V_{IN} \le 5.5V$<br>HWEN = 0V, All ENx b                                              | its = "0"               |                 | 1.7             | 4.0             | μA        |

| f <sub>SW</sub>            | Switching Frequency                                             |                                                                                                 |                         | 1.10            | 1.33            | 1.56            | MHz       |

| t <sub>START</sub>         | Start-up Time                                                   | V <sub>OUT</sub> = 90% steady sta                                                               | ate                     |                 | 250             |                 | μs        |

(1) All voltages are with respect to the potential at the GND pins.

(2) Min and Max limits are ensured by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

(3) C<sub>IN</sub>, C<sub>VOUT</sub>, C<sub>1</sub>, and C<sub>2</sub> : Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics

(4) For the two groups of current sinks on a part (GroupA and GroupB), the following are determined: the maximum sink current in the group (MAX), the minimum sink current in the group (MIN), and the average sink current of the group (AVG). For each group, two matching numbers are calculated: (MAX-AVG)/AVG and (AVG-MIN)/AVG. The largest number of the two (worst case) is considered the matching figure for the Group. The matching figure for a given part is considered to be the highest matching figure of the two Groups. The typical specification provided is the most likely norm of the matching figure for all parts.

(5) For each Dxxpin, headroom voltage is the voltage across the internal current sink connected to that pin. For Group A, B, and C current sinks, V<sub>HRx</sub> = V<sub>OUT</sub> -V<sub>LED</sub>. If headroom voltage requirement is not met, LED current regulation will be compromised.

# Electrical Characteristics<sup>(1)(2)</sup> (continued)

Limits in standard typeface are for  $T_A = 25^{\circ}$ C, and limits in boldface type apply over the full operating temperature range (-30°C to +85°C). Unless otherwise specified:  $V_{IN} = 3.6$ V;  $V_{HWEN} = V_{IN}$ ;  $V_{PWM} = 0$ V; $V_{DxA} = V_{DxB} = V_{DxC} = 0.4$ V; GroupA = GroupB = GroupC = Fullscale Current; ENxA, ENxB, ENxC Bits = "1"; 53A, 62A Bits = "0"; C1 = C2 = C\_{IN} = C\_{OUT} = 1.0\muF.<sup>(3)</sup>

| Symbol                                                                                                                                                                                                                                                                                                    | Parameter                                 | Co                                                         | ondition         | Min           | Тур | Max             | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------|------------------|---------------|-----|-----------------|-------|

| V <sub>ALS</sub>                                                                                                                                                                                                                                                                                          | ALS Reference Voltage Accuracy            |                                                            |                  | 0.95<br>(-5%) | 1   | 1.05<br>(+5%)   | V     |

|                                                                                                                                                                                                                                                                                                           |                                           | $R_{ALSA} = 9.08 k\Omega$                                  |                  | -5            |     | +5              |       |

| Р                                                                                                                                                                                                                                                                                                         | ALS Desister Assurage                     | $R_{ALSA} = 5.46 k\Omega$                                  |                  | -5            |     | +5              | %     |

| VALS           RALS           VHWEN           VPWM           VOL-INT           I²C Compa           VIL           VIH           VOL           I²C Compa           I²C Compa           I²C Compa           I²C Compa           I²C Compa           I²C Compa           I²L           I²C Compa           I₃ | ALS Resistor Accuracy                     | $R_{ALSB} = 9.13 k\Omega$                                  |                  | -5            |     | +5              | 70    |

|                                                                                                                                                                                                                                                                                                           |                                           | $R_{ALSB} = 5.52 k\Omega$                                  |                  | -5            |     | +5              |       |

| VIIIMENI                                                                                                                                                                                                                                                                                                  | LIV/END/oltogo Throoholdo                 |                                                            | Reset            | 0             |     | 0.45            | v     |

| VHWEN                                                                                                                                                                                                                                                                                                     | HWEN Voltage Thresholds                   | 2.7V ≤ V <sub>IN</sub> ≤ 5.5V                              | Normal Operation | 1.2           |     | V <sub>IN</sub> | v     |

| V <sub>PWM</sub>                                                                                                                                                                                                                                                                                          | PWM Voltage Thresholds                    | $2.7V \le V_{IN} \le 5.5V$                                 | Diodes Off       | 0             |     | 0.45            | V     |

|                                                                                                                                                                                                                                                                                                           |                                           |                                                            | Diodes On        | 1.2           |     | V <sub>IN</sub> |       |

| V <sub>OL-INT</sub>                                                                                                                                                                                                                                                                                       | Interrupt Output Logic Low '0'            | $I_{LOAD} = 3mA$                                           |                  |               |     | 400             | mV    |

| I <sup>2</sup> C Comp                                                                                                                                                                                                                                                                                     | patible Interface Voltage Specifications  | (SCL, SDIO)                                                |                  |               |     |                 |       |

| V <sub>IL</sub>                                                                                                                                                                                                                                                                                           | Input Logic Low '0'                       | $2.7 \text{V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{V}$ |                  | 0             |     | 0.45            | V     |

| V <sub>IH</sub>                                                                                                                                                                                                                                                                                           | Input Logic High '1'                      | $2.7V \le V_{IN} \le 5.5V$                                 |                  | 1.225         |     | V <sub>IN</sub> | V     |

| V <sub>OL</sub>                                                                                                                                                                                                                                                                                           | SDIO Output Logic Low '0'                 | $I_{LOAD} = 3mA$                                           |                  |               |     | 400             | mV    |

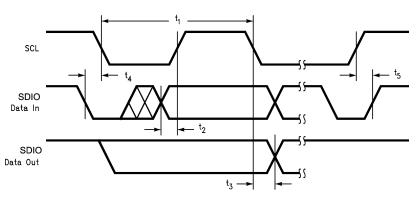

| I <sup>2</sup> C Comp                                                                                                                                                                                                                                                                                     | patible Interface Timing Specifications   | (SCL, SDIO) <sup>(6)</sup>                                 |                  |               |     |                 |       |

| t <sub>1</sub>                                                                                                                                                                                                                                                                                            | SCL (Clock Period)                        | See <sup>(7)</sup>                                         |                  | 2.5           |     |                 | μs    |

| t <sub>2</sub>                                                                                                                                                                                                                                                                                            | Data In Setup Time to SCL High            |                                                            |                  | 100           |     |                 | ns    |

| t <sub>3</sub>                                                                                                                                                                                                                                                                                            | Data Out stable After SCL Low             |                                                            |                  | 0             |     |                 | ns    |

| t <sub>4</sub>                                                                                                                                                                                                                                                                                            | SDIO Low Setup Time to SCL Low (Start)    |                                                            |                  | 100           |     |                 | ns    |

| t <sub>5</sub>                                                                                                                                                                                                                                                                                            | SDIO High Hold Time After SCL High (Stop) |                                                            |                  | 100           |     |                 | ns    |

(6) SCL and SDIO should be glitch-free in order for proper brightness control to be realized.

(7) SCL is tested with a 50% duty-cycle clock.

Texas Instruments

### SNVS598A - AUGUST 2010 - REVISED MAY 2013

www.ti.com

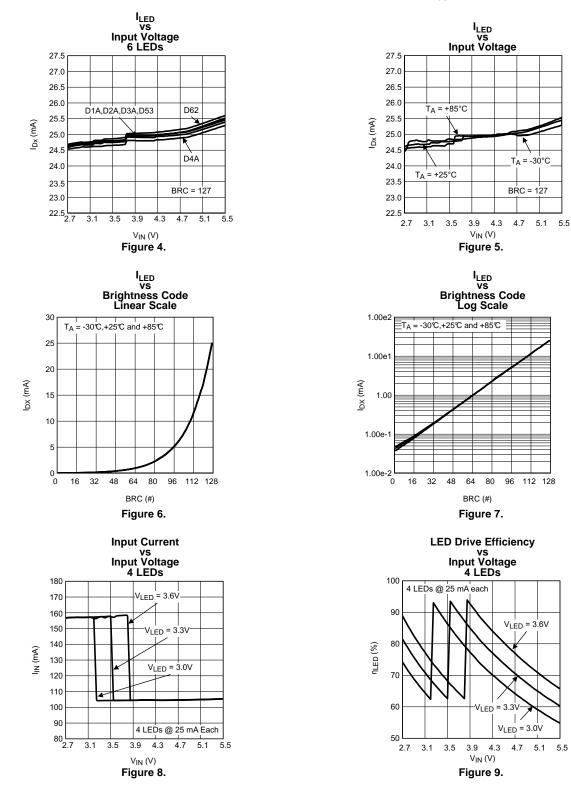

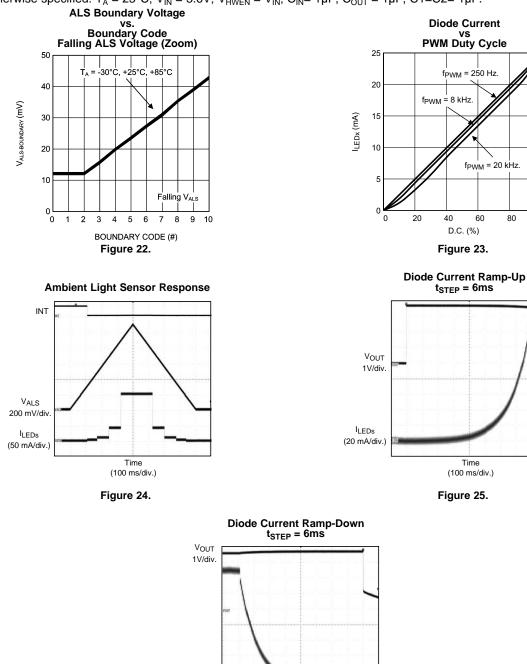

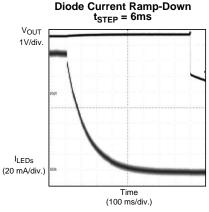

## **Typical Performance Characteristics**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ;  $V_{IN} = 3.6V$ ;  $V_{HWEN} = V_{IN}$ ;  $C_{IN} = 1\mu$ F,  $C_{OUT} = 1\mu$ F,  $C1=C2=1\mu$ F.

Texas Instruments

www.ti.com

SNVS598A - AUGUST 2010-REVISED MAY 2013

# SNVS598A – AUGUST 2010 – REVISED MAY 2013

ÈXAS **NSTRUMENTS**

www.ti.com

SNVS598A - AUGUST 2010 - REVISED MAY 2013

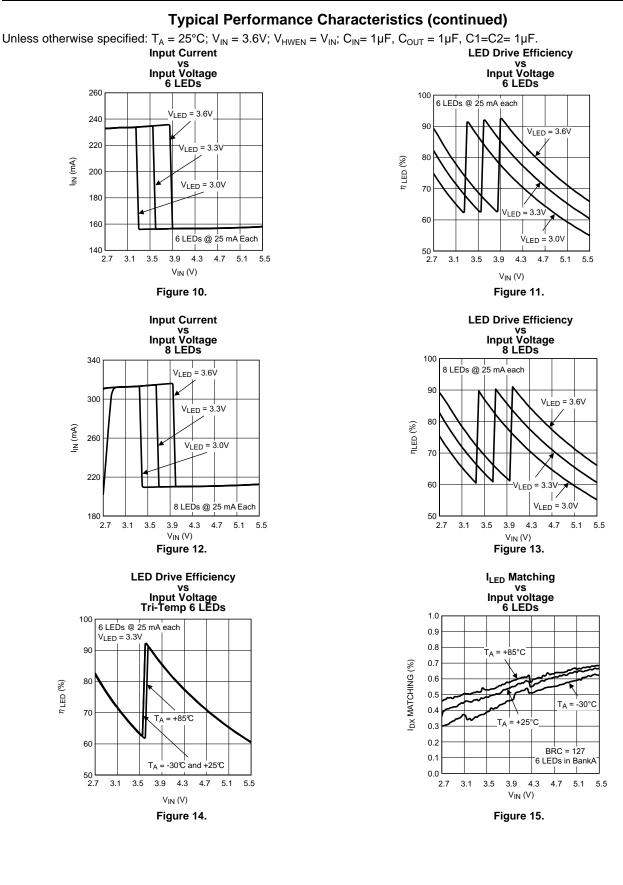

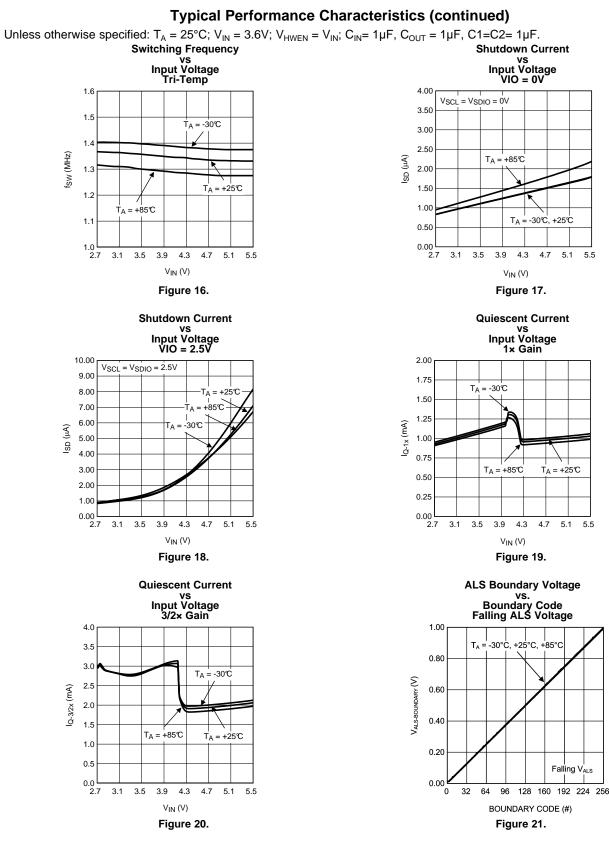

# **Typical Performance Characteristics (continued)**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ;  $V_{IN} = 3.6V$ ;  $V_{HWEN} = V_{IN}$ ;  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $C1 = C2 = 1\mu F$ .

80

100

Figure 26.

# **CIRCUIT DESCRIPTION**

#### **OVERVIEW**

The LM3535 is a white LED driver system based upon an adaptive 3/2x - 1x CMOS charge pump capable of supplying up to 200mA of total output current. With three separately controlled Groups of constant current sinks, the LM3535 is an ideal solution for platforms requiring a single white LED driver IC for main display, sub display, and indicator lighting. The tightly matched current sinks ensure uniform brightness from the LEDs across the entire small-format display.

Each LED is configured in a common anode configuration, with the peak drive current set to 25mA. An I<sup>2</sup>C compatible interface is used to enable the device and vary the brightness within the individual current sink Groups. For GroupA, 128 exponentially-spaced analog brightness control levels are available. GroupB and GroupC have 8 linearly-spaced analog brightness levels.

Additionally, the LM3535 provides 1 or 2 inputs (LM3535 has 1 and LM3535-2ALS has 2) for an Ambient Light Sensor to adaptively adjust the diode current based on ambient conditions, and a PWM pin to allow the diode current to be pulse width modulated to work with a display driver utilizing dynamic or content adjusted backlight control (DBC or CABC).

#### CIRCUIT COMPONENTS

#### Charge Pump

The input to the 3/2x - 1x charge pump is connected to the V<sub>IN</sub> pin, and the regulated output of the charge pump is connected to the V<sub>OUT</sub> pin. The recommended input voltage range of the LM3535 is 2.7V to 5.5V. The device's regulated charge pump has both open loop and closed loop modes of operation. When the device is in open loop, the voltage at V<sub>OUT</sub> is equal to the gain times the voltage at the input. When the device is in closed loop, the voltage at V<sub>OUT</sub> is regulated to 4.3V (typ.). The charge pump gain transitions are actively selected to maintain regulation based on LED forward voltage and load requirements.

#### Diode Current Sinks

Matched currents are ensured with the use of tightly matched internal devices and internal mismatch cancellation circuitry. There are eight regulated current sinks configurable into 3 different lighting regions.

#### Ambient Light Sensing (ALS) and Interrupt

The LM3535 provides an Ambient Light Sensing input (2 inputs on LM3535-2ALS version) for use with ambient backlight control. By connecting the anode of a photo diode / sensor to the sensor input pins, and configuring the appropriate ALS resistors, the LM3535 or -2ALS version, can be configured to adjust the diode current to five unique settings, corresponding to four adjustable light region trip points. Additionally, when the LM3535 determines that an ambient condition has changed, the interrupt pin, when connected to a pull-up resistor will toggle to a '0' alerting the controller. See the I<sup>2</sup>C Compatible Interface section for more details regarding the register configurations.

#### Dynamic Backlight Control Input (PWM Pin)

A PWM (Pulse Width Modulation) pin is provided on the LM3535 to allow a display driver utilizing dynamic backlight control (DBC), to adjust the LED brightness based on the content. The PWM input can be turned on or off (Acknowledge or Ignore) and the polarity can be flipped (active high or active low) through the I2C interface. The current sinks of the LM3535 require approximately 15µs. to reach steady-state target current. This turn-on time sets the minimum usable PWM pulse width for DBC/CABC.

www.ti.com

# LED Forward Voltage Monitoring

The LM3535 has the ability to switch gains (1x or 3/2x) based on the forward voltage of the LED load. This ability to switch gains maximizes efficiency for a given load. Forward voltage monitoring occurs on all diode pins. At higher input voltages, the LM3535 will operate in pass mode, allowing the  $V_{OUT}$  voltage to track the input voltage. As the input voltage drops, the voltage on the Dxx pins will also drop ( $V_{DXX} = V_{VOUT} - V_{LEDx}$ ). Once any of the active Dxx pins reaches a voltage approximately equal to 130mV, the charge pump will switch to the gain of 3/2. This switch-over ensures that the current through the LEDs never becomes pinched off due to a lack of headroom across the current sinks. Once a gain transition occurs, the LM3535 will remain in the gain of 3/2 until an I<sup>2</sup>C write to the part occurs. At that time, the LM3535 will re-evaluate the LED conditions and select the appropriate gain.

Only active Dxx pins will be monitored.

#### Configurable Gain Transition Delay

To optimize efficiency, the LM3535 has a user selectable gain transition delay that allows the part to ignore short duration input voltage drops. By default, the LM3535 will not change gains if the input voltage dip is shorter than 3 to 6 milliseconds. There are four selectable gain transition delay ranges (4 for LM3535-2ALS and 3 for LM3535) available on the LM3535. All delay ranges are set within the VF Monitor Delay Register . Please refer to the INTERNAL REGISTERS OF LM3535 section of this datasheet for more information regarding the delay ranges.

#### Hardware Enable (HWEN)

The LM3535 has a hardware enable/reset pin (HWEN) that allows the device to be disabled by an external controller without requiring an I<sup>2</sup>C write command. Under normal operation, the HWEN pin should be held high (logic '1') to prevent an unwanted reset. When the HWEN is driven low (logic '0'), all internal control registers reset to the default states and the part becomes disabled. Please see the Electrical Characteristics<sup>(1)(2)</sup> section of the datasheet for required voltage thresholds.

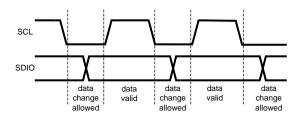

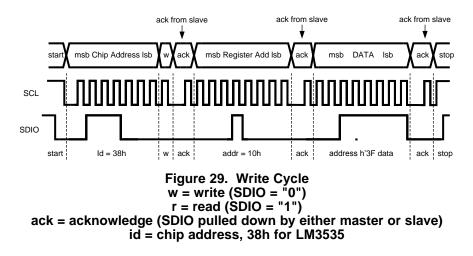

#### I<sup>2</sup>C Compatible Interface

#### DATA VALIDITY

The data on SDIO line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

Figure 27. Data Validity Diagram

A pull-up resistor between the controller's VIO line and SDIO must be greater than [(VIO-V<sub>oL</sub>) / 3mA] to meet the  $V_{OL}$  requirement on SDIO. Using a larger pull-up resistor results in lower switching current with slower edges, while using a smaller pull-up results in higher switching currents with faster edges.

<sup>(1)</sup> All voltages are with respect to the potential at the GND pins.

<sup>(2)</sup> Min and Max limits are ensured by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

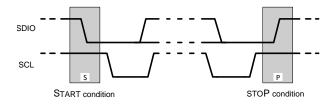

#### START AND STOP CONDITIONS

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as SDIO signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDIO transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 28. Start and Stop Conditions

#### TRANSFERRING DATA

Every byte put on the SDIO line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDIO line (HIGH) during the acknowledge clock pulse. The LM3535 pulls down the SDIO line during the 9th clock pulse, signifying an acknowledge. The LM3535 generates an acknowledge after each byte is received. There is no acknowledge created after data is read from the LM3535.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3535 7-bit address is 38h. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

#### **PC COMPATIBLE CHIP ADDRESS**

The 7-bit chip address for LM3535 is 111000, or 0x38.

#### **INTERNAL REGISTERS OF LM3535**

| Register               | Internal Hex Address | Power On Value   |  |

|------------------------|----------------------|------------------|--|

| Diode Enable Register  | 0x10                 | 0000 0000 (0x00) |  |

| Configuration Register | 0x20                 | 0000 0000 (0x00) |  |

| Options<br>Register    | 0x30                 | 0000 0000 (0x00) |  |

| ALS Zone Readback      | 0x40                 | 1111 0000 (0xF0) |  |

SNVS598A - AUGUST 2010 - REVISED MAY 2013

| Register                            | Internal He                              | ex Address    | Power On Value   |

|-------------------------------------|------------------------------------------|---------------|------------------|

| ALS Control Register                | 0x50                                     | 1 ALS Version | 0000 0011 (0x03) |

|                                     |                                          | 2 ALS Version | 0000 0000 (0x00) |

| ALS Resistor Register               | 0x51                                     | i.            | 0000 0000 (0x00) |

| ALS Select Register                 | Select Register 0x52<br>LM3535-2ALS Only |               | 1111 0001 (0xF1) |

| ALS Zone Boundary #0                | 0x60                                     |               | 0011 0011 (0x33) |

| ALS Zone Boundary #1                | 0x61                                     |               | 0110 0110 (0x66) |

| ALS Zone Boundary #2                | 0x62                                     |               | 1001 1001 (0x99) |

| ALS Zone Boundary #3                | 0x63                                     |               | 1100 1100 (0xCC) |

| ALS Brightness Zone #1              | 0x70                                     |               | 1001 1001 (0x99) |

| ALS Brightness Zone #2              | 0x71                                     |               | 1011 0110 (0xB6) |

| ALS Brightness Zone #3              | 0x72                                     |               | 1100 1100 (0xCC) |

| ALS Brightness Zone #4              | 0x73                                     |               | 1110 0110 (0xE6) |

| ALS Brightness Zone #5              | 0x74                                     |               | 1111 1111 (0xFF) |

| Group A Brightness Control Register | oup A Brightness Control Register 0xA0   |               | 1000 0000 (0x80) |

| Group B Brightness Control Register | egister 0xB0                             |               | 1100 0000 (0xC0) |

| Group C Brightness Control Register | 0xC0                                     |               | 1111 1000 (0xF8) |

| MSB  | Control Register<br>Register Address: 0x10 |      |      |      |      |      |      |  |

|------|--------------------------------------------|------|------|------|------|------|------|--|

| ENC  | EN1B                                       | EN62 | EN53 | EN4A | EN3A | EN2A | EN1A |  |

| bit7 | bit6                                       | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |

#### Figure 30. Diode Enable Register Description Internal Hex Address: 0x10

Each ENx Bit controls the state of the corresponding current sink. Writing a '1' to these bits enables the current sinks. Writing a '0' disables the current sinks. In order for current to begin flowing through the BankA current sinks, the brightness codes stored in either the BankA Brightness register or the ALS Brightness registers (with ALS enabled) must be non-zero. The BankA current sinks can be disabled in two different manors. Writing '0' to the ENx bits when the current sinks are active will disable the current sinks without going through the ramp down sequence. Additionally, setting the BankA brightness code to '0' when the current sinks are active (ENx = '1') does force the diode current to ramp down. All ramping behavior is tied to the BankA Brightness or ALS Brightness Register settings. Any change in these values will cause the LM3535 brightness state machine to ramp the diode current.

Writing a '1 to ENC, EN1B, EN62 and EN53 (when EN62 and EN53 are assigned to BankB) by default will enable the corresponding current sinks and drive the LEDs to the current value stored in the BankB and BankC brightness registers. Writing a '0' to these bits immediately disables the current sinks.

The ENC and EN1B bits are ignored if the D1C/ALS pin is configured as an ALS input and if the D1B/INT is configured as an interrupt flag.

| MSB  |        | LSB     |         |      |      |       |        |

|------|--------|---------|---------|------|------|-------|--------|

| ALSF | ALS-EN | ALS-ENB | ALS-ENA | 62A  | 53A  | PWM-P | PWM-EN |

| bit7 | bit6   | bit5    | bit4    | bit3 | bit2 | bit1  | bit0   |

#### Figure 31. Configuration Register Description Internal Hex Address:0x20

- PWM-EN: PWM Input Enable. Writing a '1' = Enable, and a '0' = Ignore (default).

- PWM-P: PWM Input Polarity. Writing a '0' = Active High (default) and a '1' = Active Low.

- 53A: Assign D53 diode to BankA. Writing a '0' assigns D53 to BankB (default) and a '1' assigns D53 to BankA.

- 62A: Assign D62 diode to BankA. Writing a '0' assigns D62 to BankB (default) and a '1' assigns D62 to BankA.

- ALS-ENA: Enable ALS on BankA. Writing a '1' enables ALS control of diode current and a '0' (default) forces the BankA current to the value stored in the BankA brightness register. The ALS-EN bit must be set to a '1' for the ALS block to control the BankA brightness.

- ALS-ENB: Enable ALS on BankB. Writing a '1' enables ALS control of diode current and a '0' (default) forces the BankB current to the value stored in the BankB brightness register. The ALS-EN bit must be set to a '1' for the ALS block to control the BankB brightness. The ALS function for BankB is different than bankA in that the ALS will only enable and disable the BankB diodes depending on the ALS zone chosen by the user. BankA utilizes the 5 different zone brightness registers (Addresses 0x70 to 0x74).

- ALS-EN: Enables ALS monitoring. Writing a '1' enables the ALS monitoring circuitry and a '0' disables it. This feature can be enabled without having the current sinks or charge pump active. The ALS value is updated in register 0x40 (ALS Zone Register)

- ALSF: ALS Interrupt Enable. Writing a '1' sets the D1B/INT pin to the ALS interrupt pin and writing a '0' (default) sets the pin to a BankB current sink.

|   | Options Register<br>Register Address: 0x30 |      |      |      |      |      |      |      |  |  |  |

|---|--------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| ſ | GT1                                        | GT0  | RD2  | RD1  | RD0  | RU2  | RU1  | RU0  |  |  |  |

|   | bit7                                       | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |  |  |

Figure 32. Options Register Internal Hex Address: 0x30

- RD0-RD2: Diode Current Ramp Down Step Time. : '000' = 6µs, '001' = 0.77ms, '010' = 1.5ms, '011' = 3ms, '100' = 6ms, '101' = 12ms, '110' = 25ms, '111' = 50ms

- RU0-RU2: Diode Current Ramp Up Step Time. : '000' = 6µs, '001' = 0.77ms, '010' = 1.5ms, '011' = 3ms, '100' = 6ms, '101' = 12ms, '110' = 25ms, '111' = 50ms

- GT0-GT1: Gain Transition Filter. The value stored in this register determines the filter time used to make a gain transition in the event of an input line step. Filter Times = '00' = 3-6ms, '01' = 0.8-1.5ms, '10' = 20μs, On LM3535-2ALS, '11' = 1μs, On LM3535, '11' = DO NOT USE

The Ramp-Up and Ramp-Down times follow the following equations:  $T_{RAMP} = (N_{Start} - N_{Target}) \times Ramp-Step Time$

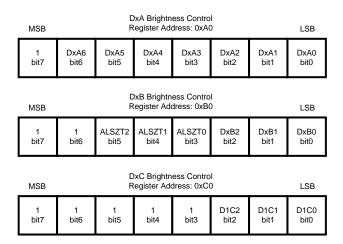

Figure 33. Brightness Control Register Description Internal Hex Address: 0xA0 (GroupA), 0xB0 (GroupB), 0xC0 (GroupC)

#### NOTE

DxA6-DxA0: Sets Brightness for DxA pins (GroupA). 111111=Fullscale. Code '0' in this register disables the BankA current sinks.

DxB2-DxB0: Sets Brightness for DxB pins (GroupB). 111=Fullscale

ALSZT2-ALSZT0: Sets the Brightness Zone boundary used to enable and disable BankB diodes based upon ambient lighting conditions.

DxC2-DxC0: Sets Brightness for D1C pin. 111 = Fullscale

The BankA Current can be approximated by the following equation where N = BRC = the decimal value stored in either the BankA Brightness Register or the five different ALS Zone Brightness Registers:

$$\begin{split} I_{\text{LED}} \ (\text{mA}) &\approx 25 \text{ x } 0.85^{[44 - \{(N+1)/2.91\}]} \\ & \text{Or} \\ \text{BRC} \ (\#) &\approx 127 + 17.9 \text{ x } \text{LN}(I_{\text{LED}(\text{mA})}/25 \text{ mA}) \end{split}$$

(1)

| BankA or<br>ALS<br>Brightness<br>Data | % of<br>I <sub>LED_MAX</sub> | BankA or ALS<br>Brightness Data | % of I <sub>LED_MAX</sub> | BankA or ALS<br>Brightness Data | % of I <sub>LED_MAX</sub> | BankA or ALS<br>Brightness<br>Data | % of I <sub>LED_MAX</sub> |

|---------------------------------------|------------------------------|---------------------------------|---------------------------|---------------------------------|---------------------------|------------------------------------|---------------------------|

| 0000000                               | 0.000%                       | 0100000                         | 0.803%                    | 1000000                         | 4.078%                    | 1100000                            | 20.713%                   |

| 0000001                               | 0.166%                       | 0100001                         | 0.845%                    | 1000001                         | 4.290%                    | 1100001                            | 21.792%                   |

| 0000010                               | 0.175%                       | 0100010                         | 0.889%                    | 1000010                         | 4.514%                    | 1100010                            | 22.928%                   |

| 0000011                               | 0.184%                       | 0100011                         | 0.935%                    | 1000011                         | 4.749%                    | 1100011                            | 24.122%                   |

| 0000100                               | 0.194%                       | 0100100                         | 0.984%                    | 1000100                         | 4.996%                    | 1100100                            | 25.379%                   |

| 0000101                               | 0.204%                       | 0100101                         | 1.035%                    | 1000101                         | 5.257%                    | 1100101                            | 26.701%                   |

| 0000110                               | 0.214%                       | 0100110                         | 1.089%                    | 1000110                         | 5.531%                    | 1100110                            | 28.092%                   |

| 0000111                               | 0.226%                       | 0100111                         | 1.146%                    | 1000111                         | 5.819%                    | 1100111                            | 29.556%                   |

| 0001000                               | 0.237%                       | 0101000                         | 1.205%                    | 1001000                         | 6.122%                    | 1101000                            | 31.096%                   |

| 0001001                               | 0.250%                       | 0101001                         | 1.268%                    | 1001001                         | 6.441%                    | 1101001                            | 32.716%                   |

| 0001010                               | 0.263%                       | 0101010                         | 1.334%                    | 1001010                         | 6.776%                    | 1101010                            | 34.420%                   |

| 0001011                               | 0.276%                       | 0101011                         | 1.404%                    | 1001011                         | 7.129%                    | 1101011                            | 36.213%                   |

| 0001100                               | 0.291%                       | 0101100                         | 1.477%                    | 1001100                         | 7.501%                    | 1101100                            | 38.100%                   |

| 0001101                               | 0.306%                       | 0101101                         | 1.554%                    | 1001101                         | 7.892%                    | 1101101                            | 40.085%                   |

| 0001110                               | 0.322%                       | 0101110                         | 1.635%                    | 1001110                         | 8.303%                    | 1101110                            | 42.173%                   |

| 0001111                               | 0.339%                       | 0101111                         | 1.720%                    | 1001111                         | 8.735%                    | 1101111                            | 44.371%                   |

| 0010000                               | 0.356%                       | 0110000                         | 1.809%                    | 1010000                         | 9.191%                    | 1110000                            | 46.682%                   |

| 0010001                               | 0.375%                       | 0110001                         | 1.904%                    | 1010001                         | 9.669%                    | 1110001                            | 49.114%                   |

| 0010010                               | 0.394%                       | 0110010                         | 2.003%                    | 1010010                         | 10.173%                   | 1110010                            | 51.673%                   |

| 0010011                               | 0.415%                       | 0110011                         | 2.107%                    | 1010011                         | 10.703%                   | 1110011                            | 54.365%                   |

| 0010100                               | 0.436%                       | 0110100                         | 2.217%                    | 1010100                         | 11.261%                   | 1110100                            | 57.198%                   |

| 0010101                               | 0.459%                       | 0110101                         | 2.332%                    | 1010101                         | 11.847%                   | 1110101                            | 60.178%                   |

| 0010110                               | 0.483%                       | 0110110                         | 2.454%                    | 1010110                         | 12.465%                   | 1110110                            | 63.313%                   |

| 0010111                               | 0.508%                       | 0111011                         | 2.582%                    | 1010111                         | 13.114%                   | 1110111                            | 66.611%                   |

| 0011000                               | 0.535%                       | 0110111                         | 2.716%                    | 1011000                         | 13.797%                   | 1111000                            | 70.082%                   |

| 0011001                               | 0.563%                       | 0111000                         | 2.858%                    | 1011001                         | 14.516%                   | 1111001                            | 73.733%                   |

| 0011010                               | 0.592%                       | 0111001                         | 3.007%                    | 1011010                         | 15.272%                   | 1111010                            | 77.574%                   |

| 0011011                               | 0.623%                       | 0111010                         | 3.163%                    | 1011011                         | 16.068%                   | 1111011                            | 81.616%                   |

| 0011100                               | 0.655%                       | 0111011                         | 3.328%                    | 1011100                         | 16.905%                   | 1111100                            | 85.868%                   |

| 0011101                               | 0.689%                       | 0111100                         | 3.502%                    | 1011101                         | 17.786%                   | 1111101                            | 90.341%                   |

#### Table 1. I<sub>LED</sub> vs. Brightness Register Data

www.ti.com

Table 1. I<sub>LED</sub> vs. Brightness Register Data (continued)

|         |        |         |        | -       | •       | •       |          |

|---------|--------|---------|--------|---------|---------|---------|----------|

| 0011110 | 0.725% | 0111101 | 3.684% | 1011110 | 18.713% | 1111110 | 95.048%  |

| 0011111 | 0.763% | 0111111 | 3.876% | 1011111 | 19.687% | 1111111 | 100.000% |

GroupB and GroupC Brightness Levels = 2.5, 5, 7.5, 10, 12.5, 15, 17.5, 25mA

| MSB       |           |           | ALS Zone<br>egister Ado | Register<br>dress: 0x40 | )             |               |               |  |  |

|-----------|-----------|-----------|-------------------------|-------------------------|---------------|---------------|---------------|--|--|

| 1<br>bit7 | 1<br>bit6 | 1<br>bit5 | 1<br>bit4               | FLAG<br>bit3            | ZONE2<br>bit2 | ZONE1<br>bit1 | ZONE0<br>bit0 |  |  |

#### Figure 34. ALS Zone Register Description Internal Hex Address: 0x40

- ZONE0-ZONE2: ALS Zone information: '000' = Zone0, '001' = Zone1, '010' = Zone2, '011' = Zone3, '100' = Zone4. Other combinations not used

- FLAG: ALS Transition Flag. '1' = Transition has occurred. '0' = No Transition. The FLAG bit is cleared once the 0x40 register has been read.

| MSB            |              | ALS Control / SI Rev Register<br>Register Address: 0x50 |              |           |           |              |              |  |  |  |  |

|----------------|--------------|---------------------------------------------------------|--------------|-----------|-----------|--------------|--------------|--|--|--|--|

| ALS-EN<br>bit7 | AVE2<br>bit6 | AVE1<br>bit5                                            | AVE0<br>bit4 | 0<br>bit3 | 0<br>bit2 | Rev1<br>bit1 | Rev0<br>bit0 |  |  |  |  |

#### Figure 35. ALS Control / Silicon Revision Register Description Internal Hex Address: 0x50

- Rev0-Rev1 : Stores the Silicon Revision value. LM3535 = '11', LM3535-2ALS = '00'

- AVE2-AVE0: Sets Averaging Time for ALS sampling. Need two to three Averaging periods to make transition decision.'000' = 25ms, '001' = 50ms, '010' = 100ms, '011' = 200ms, '100' = 400ms, '101' = 800ms, '110' = 1.6s, '111' = 3.2s

| MSB  | MSB Internal ALS Resistor Register |      |      |      |      |      |      |  |  |  |

|------|------------------------------------|------|------|------|------|------|------|--|--|--|

| R3A  | R2A                                | R1A  | R0A  | R3B  | R2B  | R1B  | R0B  |  |  |  |

| bit7 | bit6                               | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |  |  |

#### Figure 36. ALS Resistor Control Register Description Internal Hex Address: 0x51

- R3A-R0A are valid on both the LM3535 and LM3535-2ALS.

- R3B-R0B are only valid on LM3535-2ALS.

- R0-R3: Sets the internal ALS resistor value

| Table 2 | Internal | ALS | Resistor | Table |

|---------|----------|-----|----------|-------|

|---------|----------|-----|----------|-------|

| R3x | R2x | R1x | R0x | ALSA<br>Resistor<br>Value (Ω) | ALSB<br>Resistor<br>Value (Ω) |

|-----|-----|-----|-----|-------------------------------|-------------------------------|

| 0   | 0   | 0   | 0   | High Imp                      | bedance                       |

| 0   | 0   | 0   | 1   | 13.6k                         | 13.65k                        |

| 0   | 0   | 1   | 0   | 9.08k                         | 9.13k                         |

| 0   | 0   | 1   | 1   | 5.47k                         | 5.52k                         |

| 0   | 1   | 0   | 0   | 2.32k                         | 2.37k                         |

| 0   | 1   | 0   | 1   | 1.99k                         | 2.05k                         |

| 0   | 1   | 1   | 0   | 1.86k                         | 1.92k                         |

| 0   | 1   | 1   | 1   | 1.65k                         | 1.70k                         |

## SNVS598A - AUGUST 2010 - REVISED MAY 2013

|     | Table 2. Internal ALS Resistor Table (continued) |     |     |                               |                               |  |  |  |  |  |  |  |

|-----|--------------------------------------------------|-----|-----|-------------------------------|-------------------------------|--|--|--|--|--|--|--|

| R3x | R2x                                              | R1x | R0x | ALSA<br>Resistor<br>Value (Ω) | ALSB<br>Resistor<br>Value (Ω) |  |  |  |  |  |  |  |

| 1   | 0                                                | 0   | 0   | 1.18k                         | 1.24k                         |  |  |  |  |  |  |  |

| 1   | 0                                                | 0   | 1   | 1.10k                         | 1.15k                         |  |  |  |  |  |  |  |

| 1   | 0                                                | 1   | 0   | 1.06k                         | 1.11k                         |  |  |  |  |  |  |  |

| 1   | 0                                                | 1   | 1   | 986                           | 1.04                          |  |  |  |  |  |  |  |

| 1   | 1                                                | 0   | 0   | 804                           | 858                           |  |  |  |  |  |  |  |

| 1   | 1                                                | 0   | 1   | 764                           | 818                           |  |  |  |  |  |  |  |

| 1   | 1                                                | 1   | 0   | 745                           | 799                           |  |  |  |  |  |  |  |

| 1   | 1                                                | 1   | 1   | 711                           | 765                           |  |  |  |  |  |  |  |

# Table 2 Internal ALC D

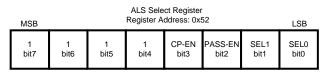

#### Figure 37. ALS Select Register (2-ALS Version Only) Internal Hex Address: 0x52

- CP-EN: Forces the LM3535 to operate in the gain of 1.5x exclusively when the Dx current sinks are enabled.

- PASS-EN: Forces the LM3535 to operate in the 1x Pass-Mode exclusively when the Dx current sinks are enabled.

| CP-EN | PASS-EN | RESULT           |  |  |  |  |

|-------|---------|------------------|--|--|--|--|

| 0     | 0       | Normal Operation |  |  |  |  |

| 0     | 1       | Pass-Mode Only   |  |  |  |  |

| 1     | 0       | 1.5x Gain Only   |  |  |  |  |

| 1     | 1       | 1.5x Gain Only   |  |  |  |  |

SEL1-SEL0: ALS Selection Bits. SEL1 and SEL0 determine how the ALS sensor information is processed. '00' = Min. of ALSA and ALSB used, '01' = ALSA used and ALSB ignored (DEFAULT), '10' = ALSB Used and ALSA ignored, '11' = Max. of ALSA and ALSB used.

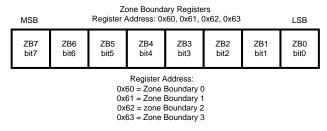

#### Figure 38. Zone Boundary Register Descriptions

- ZB7-ZB0: Sets Zone Boundary Lines with a Falling ALS voltage.

- 0xFF w/ ALS Falling = 992.3mV (typ.).

- V<sub>TRIP-LOW</sub> (typ) = [Boundary Code × 3.874mV] + 4.45mV

- For boundary codes 2 to 255. Code 0 and Code1 are mapped to equal the Code2 value.

- Each zone line has approx. 5.5mV of hysteresis between the falling and rising ALS trip points..

- Zone Boundary 0 is the line between ALS Zone 0 and Zone 1. Default Code = 0x33 or approx. 200mV

- Zone Boundary 1 is the line between ALS Zone 1 and Zone 2. Default Code = 0x66 or approx. 400mV

- Zone Boundary 2 is the line between ALS Zone 2 and Zone 3. Default Code = 0x99 or approx. 600mV

#### www.ti.com

• Zone Boundary 3 is the line between ALS Zone 3 and Zone 4. Default Code = 0xCC or approx. 800mV

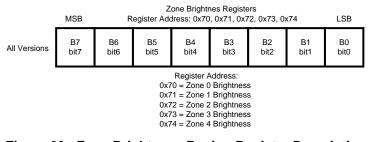

# Figure 39. Zone Brightness Region Register Description

- B7-B0: Sets the ALS Zone Brightness Code. B7 always = '1' (unused). Use the formula found in the BankA Brightness Register Description (Figure 33) to set the desired target brightness. Default values can be overwritten

- Zone0 Brightness Address = 0x70. Default = 0x99 (25) or 0.084mA

- Zone1 Brightness Address = 0x71. Default = 0xB6 (54) or 0.164mA

- Zone2 Brightness Address = 0x72. Default = 0xCC (76) or 1.45mA

- Zone3 Brightness Address = 0x73. Default = 0xE6 (102) or 6.17mA

- Zone4 Brightness Address = 0x74. Default = 0xFF (127) or 25mA

#### **APPLICATION INFORMATION**

#### AMBIENT LIGHT SENSING

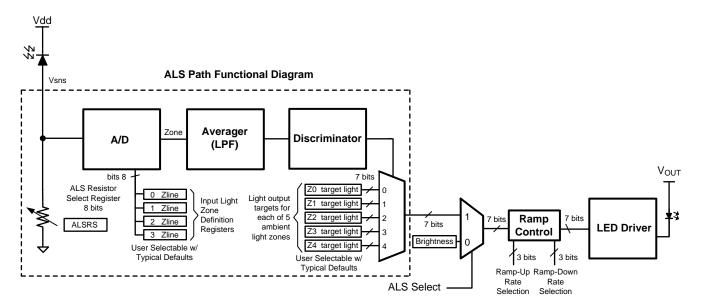

#### Ambient Light Sensor Block

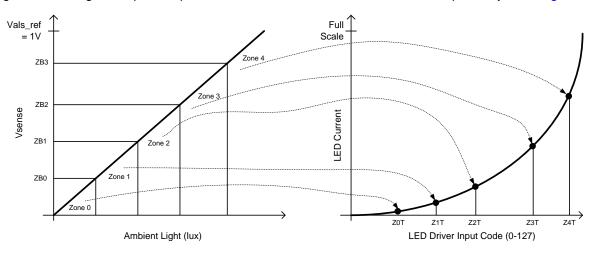

The LM3535 incorporates an Ambient Light Sensing interface (ALS) which translates an analog output ambient light sensor to a user specified brightness level. The ambient light sensing circuit has 4 programmable boundaries (ZB0 – ZB3) which define 5 ambient brightness zones. Each ambient brightness zone corresponds to a programmable brightness threshold (Z0T – Z4T).

Furthermore, the ambient light sensing inputs (ALSA and ALSB(LM3535-2ALS)) features 15 internal software selectable voltage setting resistors. This allows the LM3535 the capability of interfacing with a wide selection of ambient light sensors. Additionally, the ALS inputs can be configured as high impedance, thus providing for a true shutdown during low power modes. The ALS resistors are selectable through the ALS Resistor Select Register (see Table 2). Figure 40 shows a functional block diagram of the ambient light sensor input.

Figure 40. Ambient Light Sensor Functional Block Diagram

#### ALS Operation

The ambient light sensor input has a 0 to 1V operational input voltage range. The Typical Application Circuit shows the LM3535 with an ambient light sensor (AVAGO, APDS-9005) and the internal ALS Resistor Select Register set to 0x40 ( $2.32k\Omega$ ). This circuit converts 0 to 1000 LUX light into approximately a 0 to 850mV linear output voltage. The voltage at the active ambient light sensor input is compared against the 8 bit values programmed into the Zone Boundary Registers (ZB0-ZB3). When the ambient light sensor output crosses one of the ZB0 – ZB3 programmed thresholds the internal ALS circuitry will smoothly transition the LED current to the new 7 bit brightness level as programmed into the appropriate Zone Target Register (Z0T – Z4T, See Figure 39).

With bits [6:4] of the Configuration Register set to 1 (Bit6 = ALS Block Enable, Bit5 = BankB ALS Enable, Bit4 = BankA ALS Enable), the LM3535 is configured for Ambient Light Current Control. In this mode the ambient light sensing input (ALS) monitors the output of analog output ambient light sensing photo diode and adjusts the LED current depending on the ambient light. The ambient light sensing circuit has 4 configurable Ambient Light Boundaries (ZB0 – ZB3) programmed through the four (8-bit) Zone Boundary Registers. These zone boundaries define 5 ambient brightness zones.

On start-up the 4 Zone Boundary Registers are pre-loaded with 0x33 (51d), 0x66 (102d), 0x99 (153d), and 0xCC (204d). The ALS input has a 1V active input voltage range which makes the default Zone Boundaries approx. set at:

TEXAS

www.ti.com

Zone Boundary 0 = 200mV

Zone Boundary 1 = 400 mVZone Boundary 2 = 600 mV

Zone Boundary 3 = 800mV

These Zone Boundary Registers are all 8-bit (readable and writable) registers. By Default, the first zone (Z0) is defined between 0 and 200mV, Z1's default is defined between 200mV and 400mV, Z2 is defined between 400mV and 600mV, Z3 is defined between 600mV and 800mV, and Z4 is defined between 800mV and 1V. The default settings for the 5 Zone Target Registers are 0x19, 0x33, 0x4C, 0x66, and 0x7F. This corresponds to LED brightness settings of 84µA, 164µA, 1.45mA, 6.17mA and 25mA of current respectively. See Figure 41.

Figure 41. ALS Zone to LED Brightness Mapping

#### **ALS Configuration Example**

As an example, assume that the APDS-9005 is used as the ambient light sensing photo diode with its output connected to the ALSA input. The ALS Resistor Select Register (Address 0x51) is loaded with 0x40 which configures the ALS input for a 2.32k $\Omega$  internal pull-down resistor (see Table 2). This gives the output of the APDS-9005 a typical voltage swing of 0 to 875mV with a 0 to 1k LUX change in ambient light (0.875mV/Lux). Next, the Configuration Register (Address 0x20) is programmed with 0xDC, the ALS Control Register (Address 0x50) programmed to 0x40 and the Control Register is programmed to 0x3F. This configures the LM3535's ambient light sensing interface for:

- Ambient Light Current Control for BankA Enabled

- ALS circuitry Enabled

- Assigns D53 and D62 to bankA

- Sets the ALS Averaging Time to 400ms

Next, the Control Register (Address 0x10) is programmed with 0x3F which enables the 6 LEDs via the I<sup>2</sup>C compatible interface.

Now assume that the APDS-9005 ambient light sensor detects a 100 LUX ambient light at its input. This forces the ambient light sensors output (and the ALS1 input) to 87.5mV corresponding to Zone 0. Since Zone 0 points to the brightness code programmed in Zone Target Register 0 (loaded with code 0x19), the LED current becomes:

$I_{LED} = I_{LED\_FS} \times ZoneTarget0 = 25 \text{ mA} \times 0.336\% \approx 84 \text{ }\mu\text{A}.$

(2)

Next assume that the ambient light changes to 500 LUX (corresponding to an ALS1 voltage of 437.5mV). This moves the ambient light into Zone 2 which corresponds to Zone Target Register 2 (loaded with code 0x4C) the LED current then becomes:

$$I_{LED} = I_{LED}_{FS} \times ZoneTarget2 = 25 \text{ mA} \times 5.781\% \approx 1.45 \text{ mA}$$

(3)

This Example still applies to the LM3535-2ALS version using two ambient light sensors. The ALS selector block makes the front end decision as to which sensor to use.

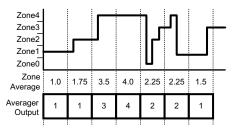

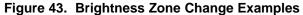

#### ALS Averaging Time

The ALS Averaging Time is the time over which the Averager block collects samples from the A/D converter and then averages them to pass to the discriminator block (see Figure 42). Ambient light sensor samples are averaged and then further processed by the discriminator block to provide rejection of noise and transient signals. The Averager is configurable with 8 different averaging times to provide varying amounts of noise and transient rejection (see Figure 35). The discriminator block algorithm has a maximum latency of two averaging cycles, therefore the averaging time selection determines the amount of delay that will exist between a steady state change in the ambient light conditions and the associated change of the backlight illumination. For example, the A/D converter samples the ALS inputs at 16kHz. If the averaging time is set to 800ms, the Averager will send the updated zone information to the discriminator every 800ms. This zone information contains the average of approximately 12800 samples (800ms × 16kHz). Due to the latency of 2 averaging cycles, when there is a steady state change in the ambient light, the LED current will begin to transition to the appropriate target value after approximately 1600ms have elapsed.

The sign and magnitude of these Averager outputs are used to determine whether the LM3535 should change brightness zones. The Averager block follows the following rules to make a zone transition:

- The Averager always begins with a Zone0 reading stored at start-up. If the main display LEDs are active before the ALS block is enabled, it is recommended that the ALS-EN bit be enabled at least 3 averaging cycles times before the ALS-ENA bit is enabled.

- The Averager will always round down to the lower zone in the case of a non-integer zone average (1.2 rounds to 1 and 1.75 also rounds to 1). Figure 42 shows an example of how the Averager will make the zone decisions for different Ambient conditions.

Figure 42. Averager Calculation

- The two most current averaging samples are used to make zone change decisions.

- To make a zone change, data from three averaging cycles are needed. (Starting Value, First Transition, Second Transition or Rest)

- To Increase the brightness zone, a positive Averager zone output must be followed by a second positive Averager output or a repeated Averager zone. ('+' to '+' or '+' to 'Rest')

- To decrease the brightness zone, a negative Averager zone output must be followed by a second negative Averager output or a repeated Averager zone. ('-' to '-' or '-' to 'Rest')

- In the case of two increases or decreases in the Averager output, the LM3535 will transition to zone equal to the last Averager output.

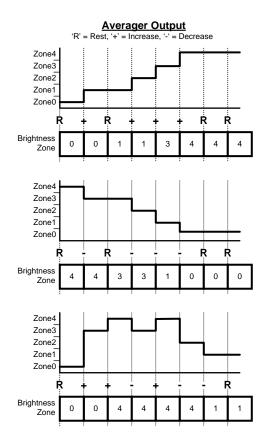

Figure 43 provides a graphical representation of the Averager's behavior.

**EXAS**

INSTRUMENTS

Using the diagram for the ALS block (Figure 40), Figure 44 shows the flow of information starting with the A/D, transitioning to the Averager, followed by the Discriminator. Each state filters the previous output to help prevent unwanted zone to zone transitions.

Figure 44. Ambient Light Input to Backlight Mapping

www.ti.com

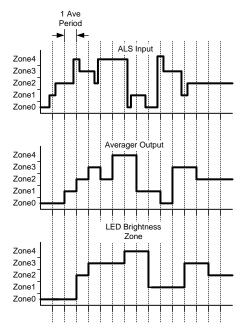

When using the ALS averaging functionality, it is important to remember that the averaging cycle is free running and is not synchronized with changing ambient lighting conditions. Due to the nature of the Averager round down, an increase in brightness can take between 2 and 3 averaging cycles to change zones while a decrease in brightness can take between 1 and 2 averaging cycles to change. See Figure 35 for a list of possible Averager periods. Figure 45 shows an example of how the perceived brightness change time can vary.

Figure 45. Perceived Brightness Change Time

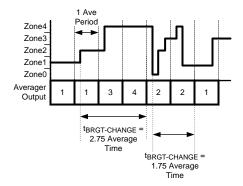

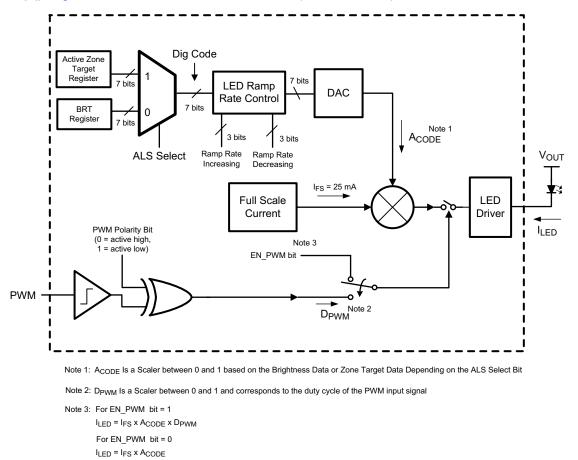

#### Ambient Light Current Control + PWM

The Ambient Light Current Control can also be a function of the PWM input duty cycle. Assume the LM3535 is configured as described in the previous example, but this time the Enable PWM bit set to '1' (Configuration Register bit [0]). Figure 46 shows how the different blocks (PWM and ALS) influence the LED current.

Figure 46. Current Control Block Diagram

#### ALS + PWM Example

(4)

In this example, the APDS-9005 sensor detects that the ambient light has changed to 1 kLux. The voltage at the ALS input is now around 875mV and the ambient light falls within Zone 5. This causes the LED brightness to be a function of Zone Target Register 5 (loaded with 0x7F). Now assume the PWM input is also driven with a 50% duty cycle pulsed waveform. The LED current now becomes:

$I_{LED} = I_{LED FS} \times ZoneTarget5 \times D = 25 \text{ mA} \times 100\% \times 50\% \approx 12.5 \text{ mA}$

#### LED CONFIGURATIONS

The LM3535 has a total of 8 current sinks capable of sinking 200mA of total diode current. These 8 current sinks are configured to operate in three independently controlled lighting regions. GroupA has four dedicated current sinks, while GroupB and GroupC each have one. To add greater lighting flexibility, the LM3535 has two additional drivers (D53 and D62) that can be assigned to either GroupA or GroupB through a setting in the general purpose register.

At start-up, the default condition is four LEDs in GroupA, three LEDs in GroupB and a single LED in GroupC (NOTE: GroupC only consists of a single current sink (D1C) under any configuration). Bits 53A and 62A in the general purpose register control where current sinks D53 and D62 are assigned. By writing a '1' to the 53A or 62A bits, D53 and D62 become assigned to the GroupA lighting region. Writing a '0' to these bits assigns D53 and D62 to the GroupB lighting region. With this added flexibility, the LM3535 is capable of supporting applications requiring 4, 5, or 6 LEDs for main display lighting, while still providing additional current sinks that can be used for a wide variety of lighting functions.

#### MAXIMUM OUTPUT CURRENT, MAXIMUM LED VOLTAGE, MINIMUM INPUT VOLTAGE

The LM3535 can drive 8 LEDs at 25mA each (GroupA, GroupB, GroupC) from an input voltage as low as 3.2V, so long as the LEDs have a forward voltage of 3.6V or less (room temperature).

The statement above is a simple example of the LED drive capability of the LM3535. The statement contains the key application parameters that are required to validate an LED-drive design using the LM3535: LED current ( $I_{LEDx}$ ), number of active LEDs ( $N_x$ ), LED forward voltage ( $V_{LED}$ ), and minimum input voltage ( $V_{IN-MIN}$ ).

The equation below can be used to estimate the maximum output current capability of the LM3535:

$$I_{LED_{MAX}} = [(1.5 \times V_{IN}) - V_{LED} - (I_{ADDITIONAL} \times R_{OUT})] / [(N_x \times R_{OUT}) + k_{HRx}] (eq. 1)$$

(5)

$$I_{LED_MAX} = [(1.5 \times V_{IN}) - V_{LED} - (I_{ADDITIONAL} \times 2.4\Omega)] / [(N_x \times 2.4\Omega) + k_{HRx}]$$

(6)

I<sub>ADDITIONAL</sub> is the additional current that could be delivered to the other LED Groups.

$R_{OUT}$  – Output resistance. This parameter models the internal losses of the charge pump that result in voltage droop at the pump output V<sub>OUT</sub>. Since the magnitude of the voltage droop is proportional to the total output current of the charge pump, the loss parameter is modeled as a resistance. The output resistance of the LM3535 is typically 2.4 $\Omega$  (V<sub>IN</sub> = 3.6V, T<sub>A</sub> = 25°C). In equation form: