# **OPA544**

# High-Voltage, High-Current OPERATIONAL AMPLIFIER

# **FEATURES**

- HIGH OUTPUT CURRENT: 2A min

- WIDE POWER SUPPLY RANGE: ±10 to ±35V

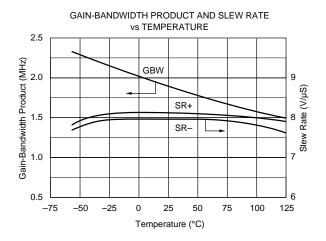

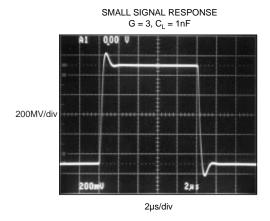

- SLEW RATE: 8V/µs

- INTERNAL CURRENT LIMIT

- THERMAL SHUTDOWN PROTECTION

- FET INPUT: I<sub>B</sub> = 100pA max

- 5-LEAD TO-220 PLASTIC PACKAGE

- 5-LEAD SURFACE MOUNT PACKAGE

# **APPLICATIONS**

- MOTOR DRIVER

- PROGRAMMABLE POWER SUPPLY

- SERVO AMPLIFIER

- VALVES, ACTUATOR DRIVER

- MAGNETIC DEFLECTION COIL DRIVER

- AUDIO AMPLIFIER

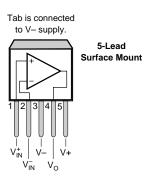

# Tab is connected to V- supply. 5-Lead TO-220 and Stagger-Formed TO-220 1 2 3 4 5

# **DESCRIPTION**

The OPA544 is a high-voltage/high-current operational amplifier suitable for driving a wide variety of high power loads. High performance FET op amp circuitry and high power output stage are combined on a single monolithic chip.

The OPA544 is protected by internal current limit and thermal shutdown circuits.

The OPA544 is available in industry-standard 5-lead TO-220 and 5-lead surface-mount power packages. Its copper tab allows easy mounting to a heat sink for excellent thermal performance. It is specified for operation over the extended industrial temperature range, -40°C to +85°C.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

At  $T_{CASE}$  = +25°C,  $V_{S}$  = ±35V, unless otherwise noted.

| PARAMETER                                                                                                                                                                                                                   | CONDITION                                                                   | MIN                                        | TYP                                                                     | MAX          | UNITS                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------|--------------|------------------------------|--|

| OFFSET VOLTAGE Input Offset Voltage vs Temperature vs Power Supply                                                                                                                                                          | Specified Temperature Range<br>V <sub>S</sub> = ±10V to ±35V                |                                            | ±1<br>±10<br>±10                                                        | ±5<br>±100   | mV<br>μV/°C<br>μV/V          |  |

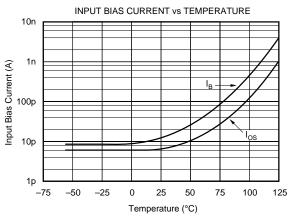

| INPUT BIAS CURRENT <sup>(1)</sup> Input Bias Current vs Temperature Input Offset Current                                                                                                                                    | V <sub>CM</sub> = 0V<br>V <sub>CM</sub> = 0V                                |                                            | ±15 See Typical Curve ±10                                               | ±100<br>±100 | pA<br>pA                     |  |

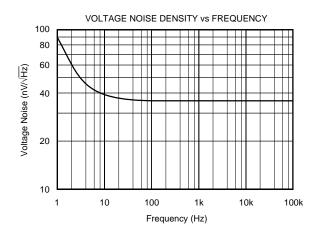

| NOISE Input Voltage Noise Noise Density, f = 1kHz Current Noise Density, f = 1kHz                                                                                                                                           |                                                                             |                                            | 36<br>3                                                                 |              | nV/√ <del>Hz</del><br>fA/√Hz |  |

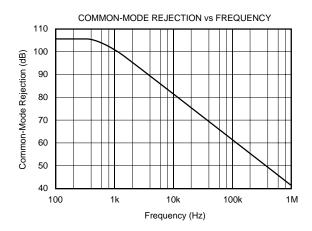

| INPUT VOLTAGE RANGE Common-Mode Input Range, Positive Negative Common-Mode Rejection                                                                                                                                        | Linear Operation Linear Operation $V_{CM} = \pm V_S - 6V$                   | (V+) -6<br>(V-) +6<br>90                   | (V+) -4<br>(V-) +4<br>106                                               |              | V<br>V<br>dB                 |  |

| INPUT IMPEDANCE Differential Common-Mode                                                                                                                                                                                    |                                                                             |                                            | 10 <sup>12</sup>    8<br>10 <sup>12</sup>    10                         |              | Ω    pF<br>Ω    pF           |  |

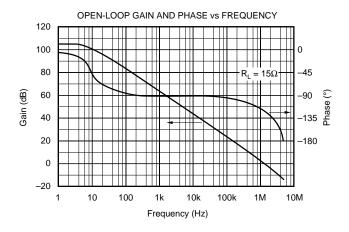

| OPEN-LOOP GAIN Open-Loop Voltage Gain                                                                                                                                                                                       | $V_O = \pm 30V$ , $R_L = 1k\Omega$                                          | 90                                         | 103                                                                     |              | dB                           |  |

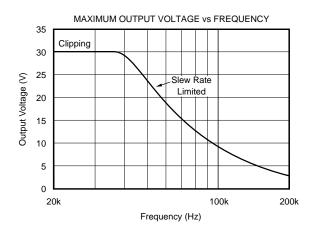

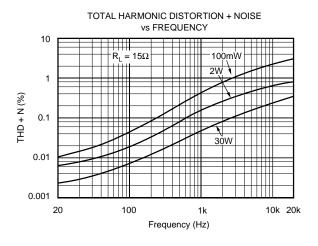

| FREQUENCY RESPONSE Gain Bandwidth Product Slew Rate Full-Power Bandwidth Settling Time 0.1% Total Harmonic Distortion                                                                                                       | $R_L = 15\Omega$ $60\text{Vp-p}, R_L = 15\Omega$ $G = -10, 60\text{V Step}$ | 5                                          | 1.4<br>8<br>See Typical Curve<br>25<br>See Typical Curve                |              | MHz<br>V/μs<br>μs            |  |

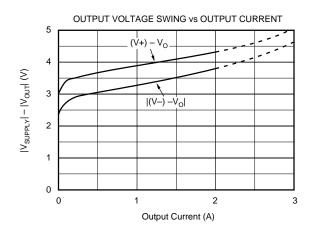

| OUTPUT  Voltage Output, Positive                                                                                                                                                                                            | $I_{O} = 2A$ $I_{O} = 2A$ $I_{O} = 0.5A$ $I_{O} = 0.5A$                     | (V+) -5<br>(V-) +5<br>(V+) -4.2<br>(V-) +4 | (V+) -4.4<br>(V-) +3.8<br>(V+) -3.8<br>(V-) +3.1<br>See SOA Curves<br>4 |              | V<br>V<br>V                  |  |

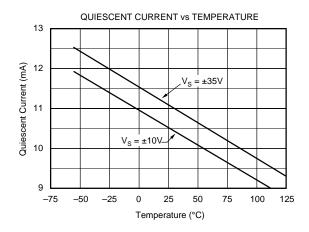

| POWER SUPPLY Specified Operating Voltage Operating Voltage Range Quiescent Current                                                                                                                                          | I <sub>O</sub> = 0                                                          | ±10                                        | ±35<br>±12                                                              | ±35<br>±15   | V<br>V<br>mA                 |  |

| $\begin{tabular}{ll} \textbf{TEMPERATURE RANGE} \\ Operating \\ Storage \\ Thermal Resistance, $\theta_{\rm JC}$ \\ Thermal Resistance, $\theta_{\rm JC}$ \\ Thermal Resistance, $\theta_{\rm JA}$ \\ \hline \end{tabular}$ | f > 50Hz<br>DC<br>No Heat Sink                                              | -40<br>-40                                 | 2.7<br>3<br>65                                                          | +85<br>+125  | °C<br>°C/W<br>°C/W<br>°C/W   |  |

NOTES: (1) High-speed test at  $T_J = 25^{\circ}C$ .

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

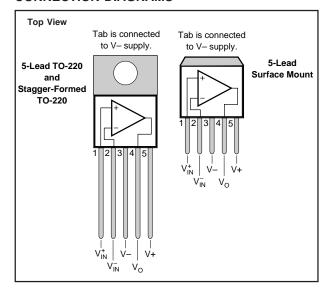

#### **CONNECTION DIAGRAMS**

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V+ to V              | 70V                      |

|--------------------------------------|--------------------------|

| Output Current                       | See SOA Curve            |

| Input Voltage                        | (V–) –0.7V to (V+) +0.7V |

| Operating Temperature                | 40°C to +125°C           |

| Storage Temperature                  | 40°C to +125°C           |

| Junction Temperature                 | 150°C                    |

| Lead Temperature (soldering -10s)(1) | 300°C                    |

NOTE: (1) Vapor-phase or IR reflow techniques are recommended for soldering the OPA544F surface mount package. Wave soldering is not recommended due to excessive thermal shock and "shadowing" of nearby devices.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT   | PACKAGE                      | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|-----------|------------------------------|------------------------------------------|

| OPA544T   | 5-Lead TO-220                | 315                                      |

| OPA544T-1 | 5-Lead Stagger-Formed TO-220 | 323                                      |

| OPA544F   | 5-Lead Surface-Mount         | 325                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

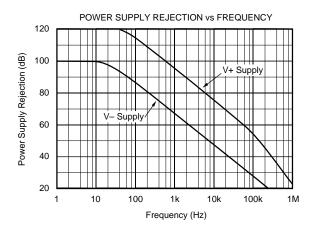

# **TYPICAL PERFORMANCE CURVES**

At  $T_{CASE} = +25$ °C,  $V_{S} = \pm 35$ V, unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_{CASE} = +25$ °C,  $V_{S} = \pm 35$ V, unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_{CASE} = +25$ °C,  $V_{S} = \pm 35$ V, unless otherwise noted.

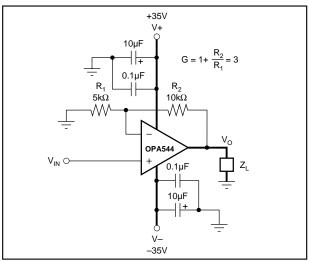

# APPLICATIONS INFORMATION

Figure 1 shows the OPA544 connected as a basic non-inverting amplifier. The OPA544 can be used in virtually any op amp configuration. Power supply terminals should be bypassed with low series impedance capacitors. The technique shown, using a ceramic and tantalum type in parallel is recommended. Power supply wiring should have low series impedance and inductance.

FIGURE 1. Basic Circuit Connections.

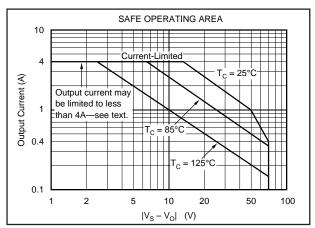

#### SAFE OPERATING AREA

Stress on the output transistors is determined by the output current and the voltage across the conducting output transistor,  $V_S - V_O$ . The power dissipated by the output transistor is equal to the product of the output current and the voltage across the conducting transistor,  $V_S - V_O$ . The Safe Operating Area (SOA curve, Figure 2) shows the permissible range of voltage and current.

The safe output current decreases as  $V_S - V_O$  increases. Output short-circuits are a very demanding case for SOA. A short-circuit to ground forces the full power supply voltage (V+ or V–) across the conducting transistor. With  $V_S = \pm 35 \, \mathrm{V}$  the safe output current is 1.5A (at 25°C). The short-circuit current is approximately 4A which exceeds the SOA. This situation will activate the thermal shutdown circuit in the OPA544. For further insight on SOA, consult Application Bulletin AB-039.

FIGURE 2. Safe Operating Area.

#### **CURRENT LIMIT**

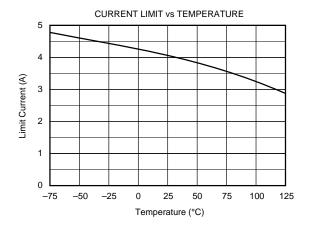

The OPA544 has an internal current limit set for approximately 4A. This current limit decreases with increasing junction temperature as shown in the typical curve, Current Limit vs Temperature. This, in combination with the thermal shutdown circuit, provides protection from many types of overload. It may not, however, protect for short-circuit to ground, depending on the power supply voltage, ambient temperature, heat sink and signal conditions.

#### POWER DISSIPATION

Power dissipation depends on power supply, signal and load conditions. For dc signals, power dissipation is equal to the product of output current times the voltage across the conducting output transistor. Power dissipation can be minimized by using the lowest possible power supply voltage necessary to assure the required output voltage swing.

For resistive loads, the maximum power dissipation occurs at a dc output voltage of one-half the power supply voltage. Dissipation with ac signals is lower. Application Bulletin AB-039 explains how to calculate or measure power dissipation with unusual signals and loads.

#### **HEATSINKING**

Most applications require a heat sink to assure that the maximum junction temperature is not exceeded. The heat sink required depends on the power dissipated and on ambient conditions. Consult Application Bulletin AB-038 for information on determining heat sink requirements.

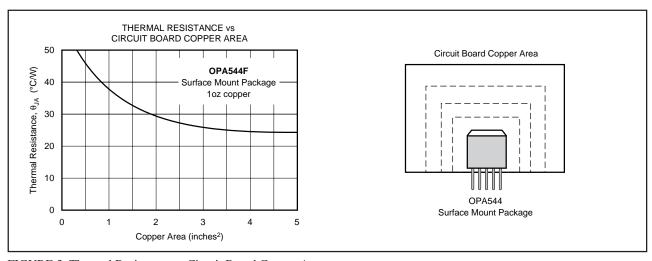

The mounting tab of the surface-mount package version should be soldered to a circuit board copper area for good heat dissipation. Figure 3 shows typical thermal resistance from junction to ambient as a function of the copper area.

#### THERMAL PROTECTION

The OPA544 has thermal shutdown that protects the amplifier from damage. Any tendency to activate the thermal shutdown circuit during normal operation is indication of excessive power dissipation or an inadequate heat sink.

The thermal protection activates at a junction temperature of approximately 155°C. For reliable operation, junction temperature should be limited to 150°C, maximum. To estimate the margin of safety in a complete design (including heat sink), increase the ambient temperature until the thermal protection is activated. Use worst-case load and signal conditions. For good reliability, the thermal protection should trigger more than 25°C above the maximum expected ambient condition of your application. This produces a junction temperature of 125°C at the maximum expected ambient condition.

Depending on load and signal conditions, the thermal protection circuit may produce a duty-cycle modulated output signal. This limits the dissipation in the amplifier, but the rapidly varying output waveform may be damaging to some loads. The thermal protection may behave differently depending on whether internal dissipation is produced by sourcing or sinking output current.

#### **OUTPUT STAGE COMPENSATION**

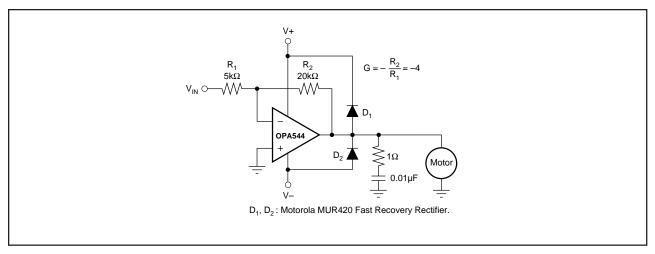

The complex load impedances common in power op amp applications can cause output stage instability. Figure 3 shows an output series R/C compensation network ( $1\Omega$  in series with  $0.01\mu F$ ) which generally provides excellent stability. Some variation in circuit values may be required with certain loads.

#### **UNBALANCED POWER SUPPLIES**

Some applications do not require equal positive and negative output voltage swing. The power supply voltages of the OPA544 do not need to be equal. For example, a –6V negative power supply voltage assures that the inputs of the OPA544 are operated within their linear common-mode range, and that the output can swing to 0V. The V+ power supply could range from 15V to 65V. The total voltage (V– to V+) can range from 20V to 70V. With a 65V positive supply voltage, the device may not be protected from damage during short-circuits because of the larger V<sub>CE</sub> during this condition.

#### **OUTPUT PROTECTION**

Reactive and EMF-generating loads can return load current to the amplifier, causing the output voltage to exceed the power supply voltage. This damaging condition can be avoided with clamp diodes from the output terminal to the power supplies as shown in Figure 4. Fast-recovery rectifier diodes with a 4A or greater continuous rating are recommended.

FIGURE 3. Thermal Resistance vs Circuit Board Copper Area.

FIGURE 4. Motor Drive Circuit.

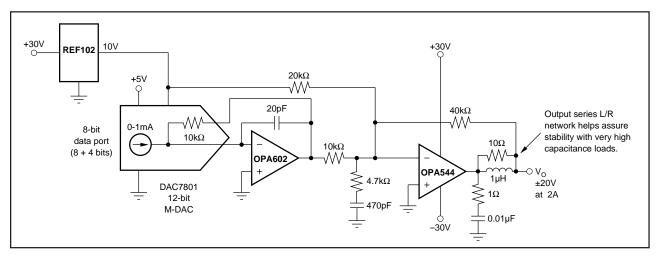

FIGURE 5. Digitally Programmable Power Supply.

17-Mar-2017

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type     | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|------------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|-------------------------|---------|

| OPA544F/500      | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    | 500            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-2-260C-1 YEAR |              | OPA544F                 | Samples |

| OPA544F/500G3    | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    | 500            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-2-260C-1 YEAR |              | OPA544F                 | Samples |

| OPA544FKTTT      | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    | 250            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-2-260C-1 YEAR |              | OPA544F                 | Samples |

| OPA544FKTTTG3    | ACTIVE | DDPAK/<br>TO-263 | KTT                | 5    | 250            | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-2-260C-1 YEAR |              | OPA544F                 | Samples |

| OPA544T          | ACTIVE | TO-220           | KC                 | 5    | 49             | Green (RoHS<br>& no Sb/Br) | CU SN            | N / A for Pkg Type  | -40 to 85    | OPA544T                 | Samples |

| OPA544TG3        | ACTIVE | TO-220           | KC                 | 5    | 49             | Green (RoHS<br>& no Sb/Br) | CU SN            | N / A for Pkg Type  | -40 to 85    | OPA544T                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight

in homogeneous material)

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# **PACKAGE OPTION ADDENDUM**

17-Mar-2017

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

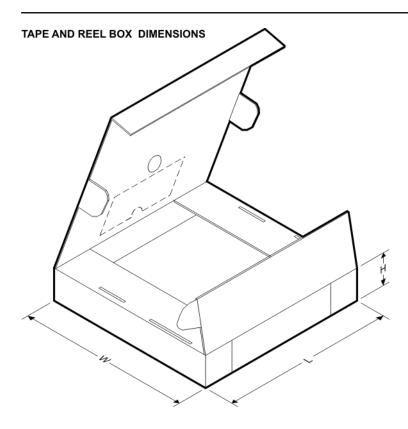

# PACKAGE MATERIALS INFORMATION

www.ti.com 21-Jan-2017

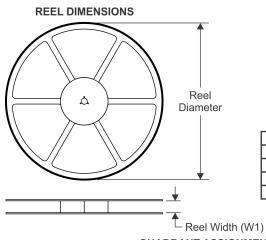

# TAPE AND REEL INFORMATION

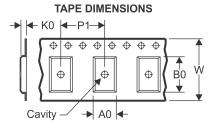

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

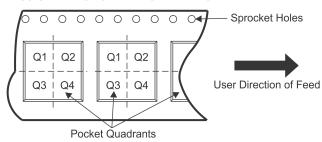

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type  | Package<br>Drawing |   | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|------------------|--------------------|---|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA544F/500 | DDPAK/<br>TO-263 | KTT                | 5 | 500 | 330.0                    | 24.4                     | 10.6       | 15.6       | 4.9        | 16.0       | 24.0      | Q2               |

| OPA544FKTTT | DDPAK/<br>TO-263 | KTT                | 5 | 250 | 330.0                    | 24.4                     | 10.6       | 15.6       | 4.9        | 16.0       | 24.0      | Q2               |

www.ti.com 21-Jan-2017

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| OPA544F/500 | DDPAK/TO-263 | KTT             | 5    | 500 | 367.0       | 367.0      | 45.0        |

| OPA544FKTTT | DDPAK/TO-263 | KTT             | 5    | 250 | 367.0       | 367.0      | 45.0        |