# Two-Channel, Asynchronous Sample Rate Converter with Integrated Digital Audio Interface Receiver and Transmitter

#### **FEATURES**

- Two-Channel Asynchronous Sample Rate Converter (SRC)

- Dynamic Range with –60dB Input (A-Weighted): 128dB typical

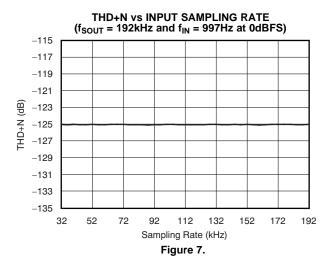

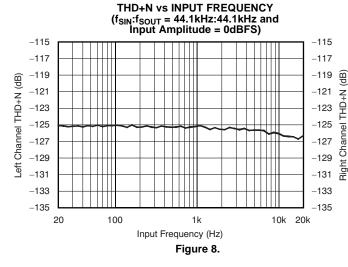

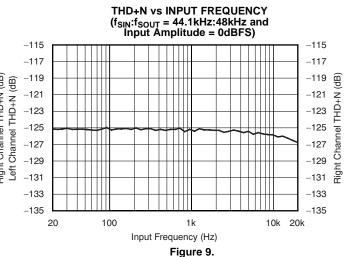

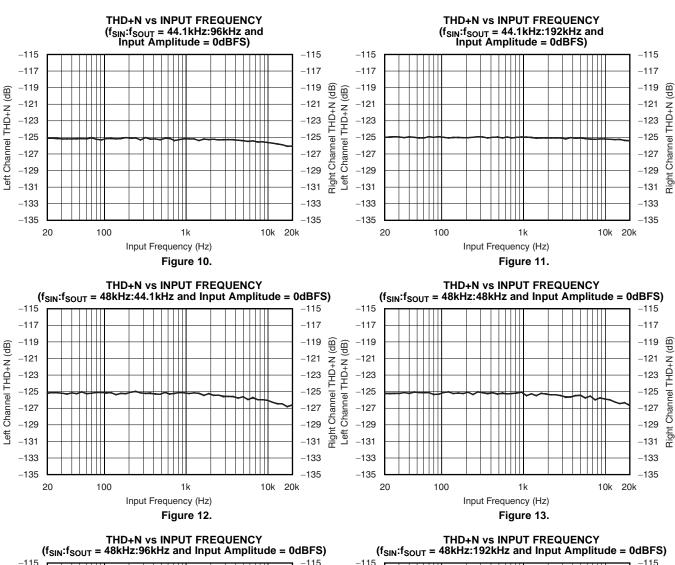

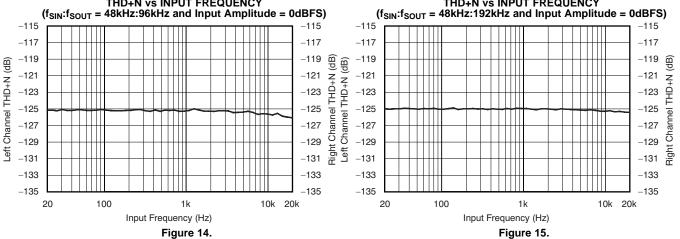

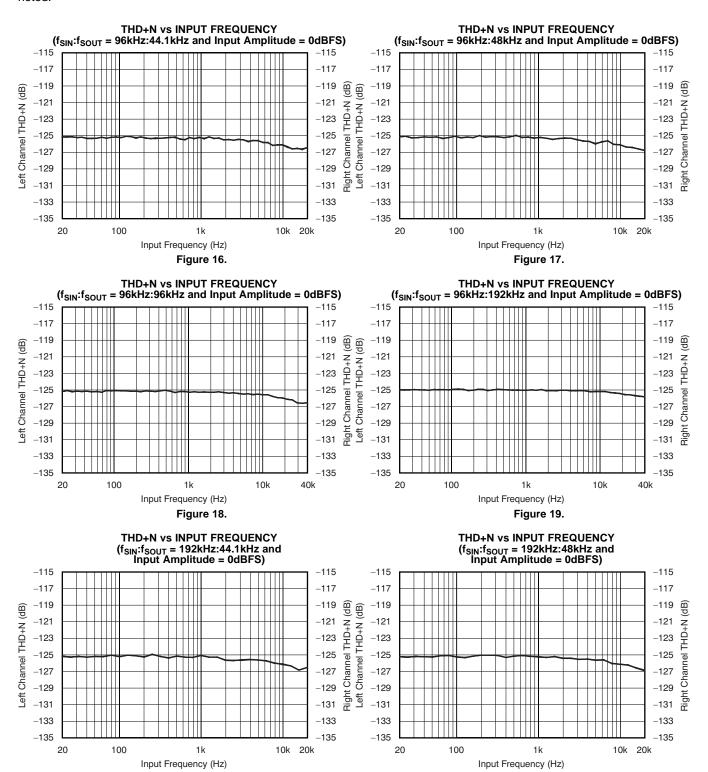

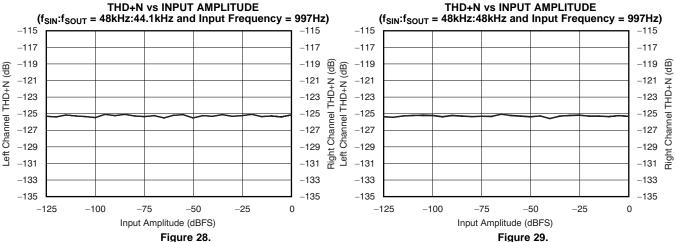

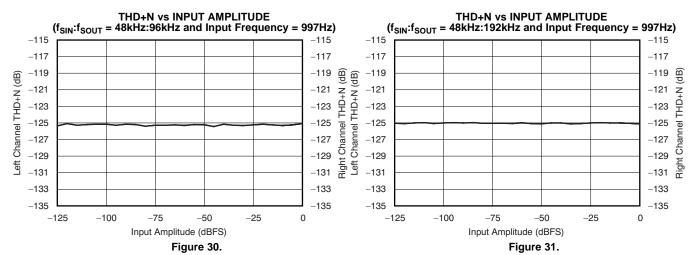

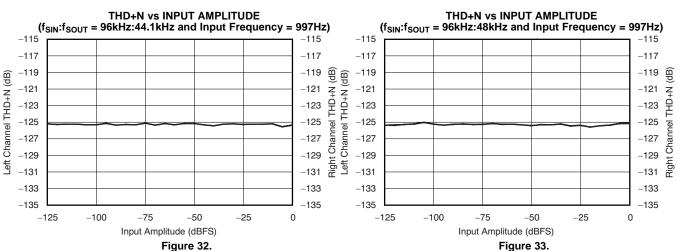

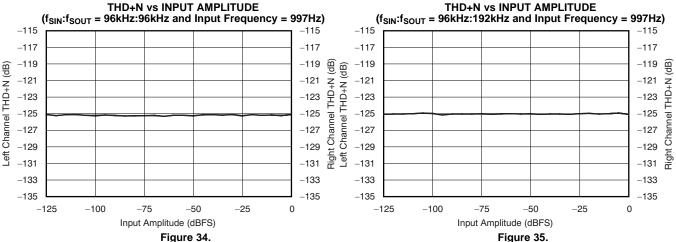

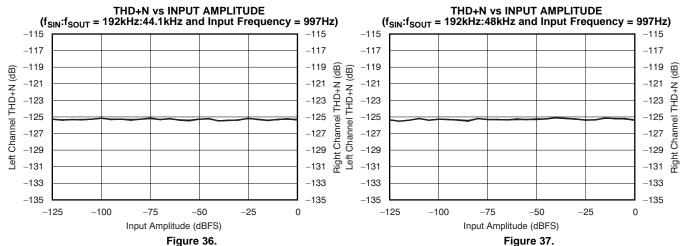

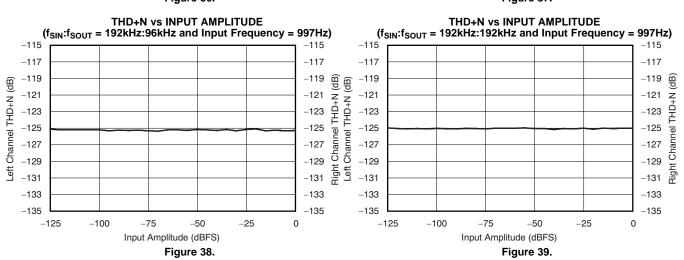

- Total Harmonic Distortion and Noise (THD+N) with Full-Scale Input: –125dB typical

- Supports Audio Input and Output Data Word Lengths Up to 24 Bits

- Supports Input and Output Sampling Frequencies Up to 216kHz

- Automatic Detection of the Input-to-Output Sampling Ratio

- Wide Input-to-Output Conversion Range:

16:1 to 1:16 Continuous

- Excellent Jitter Attenuation Characteristics

- Digital De-Emphasis Filtering for 32kHz,

44.1kHz, and 48kHz Input Sampling Rates

- Digital Output Attenuation and Mute Functions

- Output Word Length Reduction

- Status Registers and Interrupt Generation for Sampling Ratio and Ready Flags

- Digital Audio Interface Transmitter (DIT)

- Supports Sampling Rates Up to 216kHz

- Includes Differential Line Driver and CMOS Buffered Outputs

- Block-Sized Data Buffers for Both Channel Status and User Data

- Status Registers and Interrupt Generation for Flag and Error Conditions

- User-Selectable Serial Host Interface: SPI or Philips I<sup>2</sup>C<sup>™</sup>

- Provides Access to On-Chip Registers and Data Buffers

U.S. Patent No. 7,262,716

- Digital Audio Interface Receiver (DIR)

- PLL Lock Range Includes Sampling Rates from 20kHz to 216kHz

- Includes Four Differential Input Line Receivers and an Input Multiplexer

- Bypass Multiplexer Routes Line Receiver Outputs to Line Driver and Buffer Outputs

- Block-Sized Data Buffers for Both Channel Status and User Data

- Automatic Detection of Non-PCM Audio Streams (DTS CD/LD and IEC 61937 formats)

- Audio CD Q-Channel Sub-Code Decoding and Data Buffer

- Status Registers and Interrupt Generation for Flag and Error Conditions

- Low Jitter Recovered Clock Output

- Two Audio Serial Ports (Ports A and B)

- Synchronous Serial Interface to External Signal Processors, Data Converters, and Logic

- Slave or Master Mode Operation with Sampling Rates up to 216kHz

- Supports Left-Justified, Right-Justified, and Philips I<sup>2</sup>S™ Data Formats

- Supports Audio Data Word Lengths Up to 24 Bits

- Four General-Purpose Digital Outputs

- Multifunction Programmable Via Control Registers

- Extensive Power-Down Support

- Functional Blocks May Be Disabled Individually When Not In Use

- Operates From +1.8V Core and +3.3V I/O Power Supplies

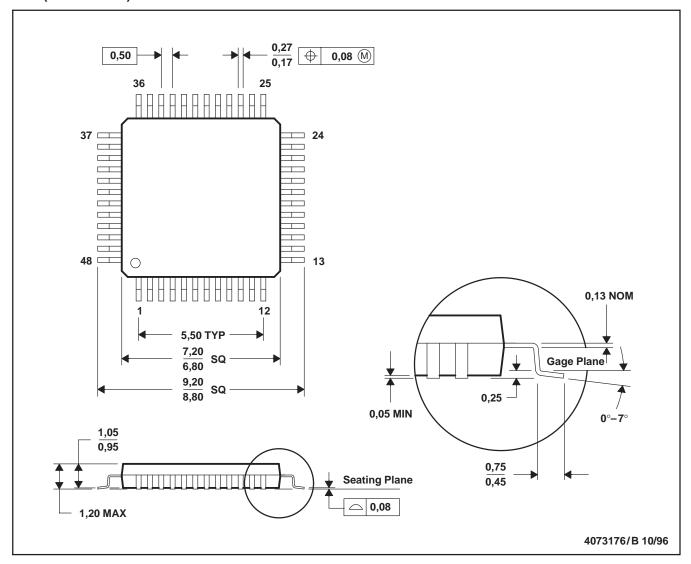

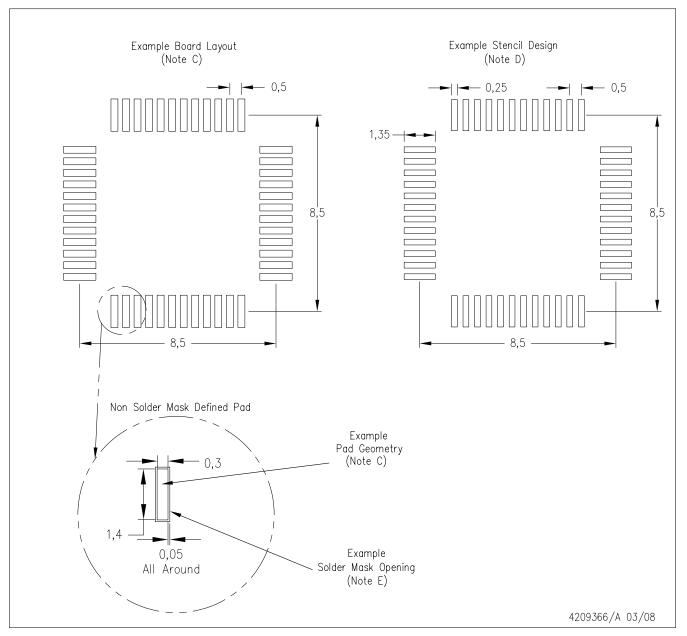

- Small TQFP-48 Package, Compatible with the SRC4392 and DIX4192

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Dolby is a registered trademark of Dolby Laboratories. I2C, I2S are trademarks of Koninklijke Philips Electronics N.V. All other trademarks are the property of their respective owners.

#### **APPLICATIONS**

- DIGITAL AUDIO RECORDERS AND MIXING DESKS

- DIGITAL AUDIO INTERFACES FOR COMPUTERS

- DIGITAL AUDIO ROUTERS AND DISTRIBUTION SYSTEMS

- BROADCAST STUDIO EQUIPMENT

- DVD/CD RECORDERS

- SURROUND SOUND DECODERS AND A/V RECEIVERS

- CAR AUDIO SYSTEMS

#### DESCRIPTION

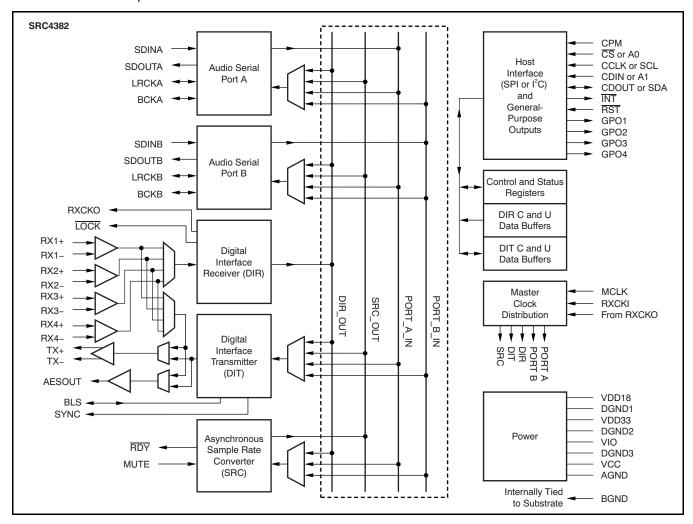

The SRC4382 is a highly-integrated CMOS device designed for use in professional and broadcast digital audio systems. The SRC4382 combines a high-performance, two-channel, asynchronous sample rate converter (SRC) with a digital audio interface receiver (DIR) and transmitter (DIT), two audio serial ports, and flexible distribution logic for interconnection of the function block data and clocks.

The DIR and DIT are compatible with the AES3, S/PDIF, IEC 60958, and EIAJ CP-1201 interface standards. The audio serial ports, DIT, and SRC may be operated at sampling rates up to 216kHz. The DIR lock range includes sampling rates from 20kHz to 216kHz.

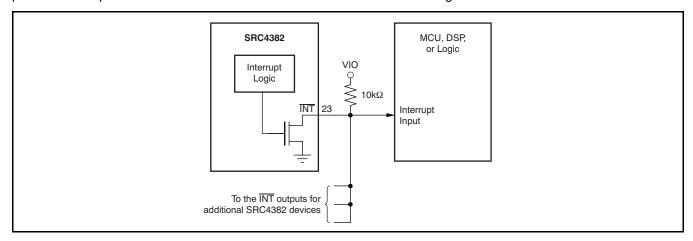

The SRC4382 is configured using on-chip control registers and data buffers, which are accessed through either a 4-wire serial peripheral interface (SPI) port, or a 2-wire Philips I<sup>2</sup>C bus interface. Status registers provide access to a variety of flag and error bits, which are derived from the various function blocks. An open drain interrupt output pin is provided, and is supported by flexible interrupt reporting and mask options via control register settings. A master reset input pin is provided for initialization by a host processor or supervisory functions.

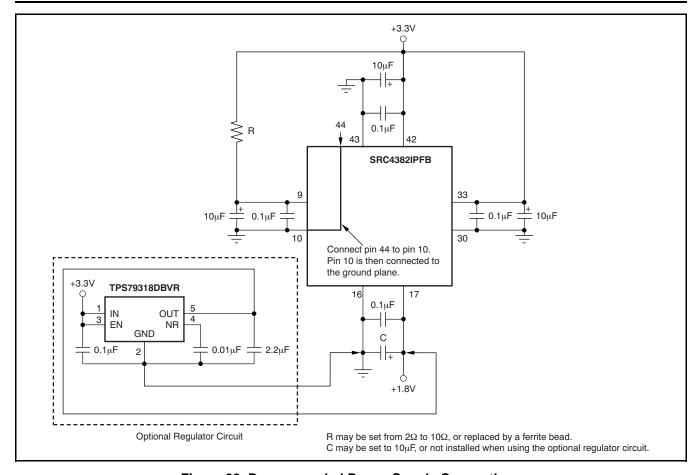

The SRC4382 requires a +1.8V core logic supply, in addition to a +3.3V supply for powering portions of the DIR, DIT, and line driver and receiver functions. A separate logic I/O supply supports operation from +1.65V to +3.6V, providing compatibility with low voltage logic interfaces typically found on digital signal processors and programmable logic devices. The SRC4382 is available in a lead-free, TQFP-48 package, and is pin- and register-compatible with the Texas Instruments SRC4392 and DIX4192 products.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| PRODUCT | PACKAGE | PACKAGE<br>DESIGNATOR | OPERATING<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|---------|---------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| SRC4382 | TQFP-48 | PFB                   | -40C to +85C                      | SRC4382I           | SRC4382IPFBT       | Tape and Reel, 250           |

| SRC4362 | TQFF-40 | PFB                   | -40C to +65C                      | 3RC43021           | SRC4382IPFBR       | Tape and Reel, 2000          |

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

| Power Supplies                                                                                                                                                            |                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| VDD18                                                                                                                                                                     | -0.3V to +2.0V                |

| VDD33                                                                                                                                                                     | -0.3V to +4.0V                |

| VIO                                                                                                                                                                       | -0.3V to +4.0V                |

| VCC                                                                                                                                                                       | -0.3V to +4.0V                |

| Digital Input Voltage: Digital Logic                                                                                                                                      |                               |

| RXCKI, MUTE, CPM, $\overline{\text{CS}}$ , CCLK, CDIN, CDOUT, $\overline{\text{INT}}$ , $\overline{\text{RST}}$ , MCLK, BLS, SYNC, BCKA, BCKB, LRCKA, LRCKB, SDINA, SDINB | -0.3V to (VIO + 0.3V)         |

| Line Receiver Input Voltage (per pin)                                                                                                                                     |                               |

| RX1+, RX1-, RX2+, RX2-, RX3+, RX3-, RX4+, RX4-                                                                                                                            | (VDD33 + 0.3) V <sub>PP</sub> |

| Input Current (all pins except power and ground)                                                                                                                          | 10mA                          |

| Ambient Operating Temperature                                                                                                                                             | -40C to +85C                  |

| Storage Temperature                                                                                                                                                       | -65C to +150C                 |

<sup>(1)</sup> These limits are stress ratings only. Stresses beyond these limits may result in permanent damage. Extended exposure to absolute maximum ratings may degrade device reliability. Normal operation or performance at or beyond these limits is not specified or ensured.

# **ELECTRICAL CHARACTERISTICS: General, SRC, DIR, and DIT**

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

| PARAMETER                                                                        | CONDITIONS                                          | MIN      | TYP | MAX      | UNITS    |

|----------------------------------------------------------------------------------|-----------------------------------------------------|----------|-----|----------|----------|

| DIGITAL I/O CHARACTERISTICS (All I/O Pins Except Line Receivers and Line Driver) |                                                     |          |     |          |          |

| High-Level Input Voltage, VIH                                                    |                                                     | 0.7 εVIO |     | VIO      | V        |

| Low-Level Input Voltage, $V_{\rm IL}$                                            |                                                     | 0        |     | 0.3 υVIO | V        |

| High-Level Input Current, I <sub>IH</sub>                                        |                                                     |          | 0.5 | 10       | μΑ       |

| Low-Level Input Current, V <sub>IL</sub>                                         |                                                     |          | 0.5 | 10       | μA       |

| High-Level Output Voltage, V <sub>OH</sub>                                       | $I_O = -4mA$                                        | 0.8 υVIO |     | VIO      | V        |

| Low-Level Output Voltage, V <sub>OL</sub>                                        | $I_O = +4mA$                                        | 0        |     | 0.2 υVIO | V        |

| Input Capacitance, C <sub>IN</sub>                                               |                                                     |          | 3   |          | pF       |

| LINE RECEIVER INPUTS<br>(RX1+, RX1-, RX2+, RX2-, RX3+, RX3-, RX4+, RX4-)         |                                                     |          |     |          |          |

| Differential Input Sensitivity, $V_{TH}$                                         | Voltage across a given differential input pair      |          | 150 | 200      | mV       |

| Input Hysteresis, V <sub>HY</sub>                                                |                                                     | 150      |     |          | mV       |

| LINE DRIVER OUTPUTS (TX+, TX-)                                                   |                                                     |          |     |          |          |

| Differential Output Voltage, $V_{TXO}$                                           | $R_L = 110\Omega$ Across TX+ and TX-                | 5.4      |     |          | $V_{PP}$ |

| MASTER CLOCK INPUT                                                               |                                                     |          |     |          |          |

| Master Clock Input (MCLK) Frequency, f <sub>MCLK</sub>                           |                                                     | 1        |     | 27.7     | MHz      |

| Master Clock Input (MCLK) Duty Cycle, f <sub>MCLKD</sub>                         |                                                     | 45       |     | 55       | %        |

| ASYNCHRONOUS SAMPLE RATE CONVERTER (SRC)                                         |                                                     |          |     |          |          |

| Input or Output Sampling Rate, $f_{\text{SIN}}$ or $f_{\text{SOUT}}$             |                                                     | 4        |     | 216      | kHz      |

| Input-to-Output Sampling Ratio                                                   |                                                     | 1:16     |     | 16:1     |          |

| Interchannel Gain Mismatch                                                       |                                                     |          | 0   |          | dB       |

| Interchannel Phase Mismatch                                                      |                                                     |          | 0   |          | Degrees  |

| Dynamic Range (no weighting filter applied) (1)                                  | BW = 22Hz to $f_{SOUT}/2$ ,<br>f = 997Hz at -60dBFS |          |     |          |          |

| $f_{SIN}:f_{SOUT} = 12kHz:192kHz$                                                |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 44.1kHz:44.1kHz$                                             |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 44.1kHz:48kHz$                                               |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 44.1kHz:96kHz$                                               |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 44.1kHz:192kHz$                                              |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 48kHz:44.1kHz$                                               |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 48kHz:48kHz$                                                 |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 48kHz:96kHz$                                                 |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 48kHz:192kHz$                                                |                                                     |          | 125 |          | dB       |

| $f_{SIN}$ : $f_{SOUT} = 96kHz$ :44.1kHz                                          |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 96kHz:48kHz$                                                 |                                                     |          | 125 |          | dB       |

| $f_{SIN}$ : $f_{SOUT} = 96kHz$ : $96kHz$                                         |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 96kHz:192kHz$                                                |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 192kHz:12kHz$                                                |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 192kHz:44.1kHz$                                              |                                                     |          | 125 |          | dB       |

| $f_{SIN}$ : $f_{SOUT} = 192kHz$ :48kHz                                           |                                                     |          | 125 |          | dB       |

| $f_{SIN}$ : $f_{SOUT} = 192kHz$ :96kHz                                           |                                                     |          | 125 |          | dB       |

| $f_{SIN}:f_{SOUT} = 192kHz:192kHz$                                               |                                                     |          | 125 |          | dB       |

<sup>(1)</sup> Measured with an Audio Precision SYS-2722 192kHz test system with the input and output sampling frequencies asynchronous to one another. A-weighted dynamic range specifications will be improved by approximately 2dB to 3dB when compared to the results without A-weighting applied.

Submit Documentation Feedback

Copyright © 2006–2007, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS: General, SRC, DIR, and DIT (continued)**

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

|                                                          |                                                   |                           | SRC4382 | SRC4382                    |         |  |

|----------------------------------------------------------|---------------------------------------------------|---------------------------|---------|----------------------------|---------|--|

| PARAMETER                                                | CONDITIONS                                        | MIN                       | TYP     | MAX                        | UNITS   |  |

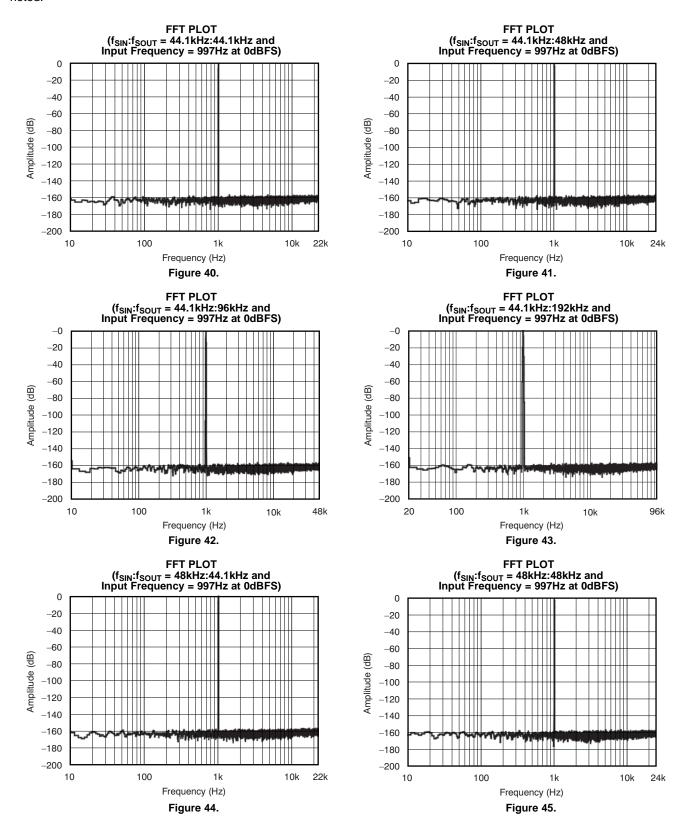

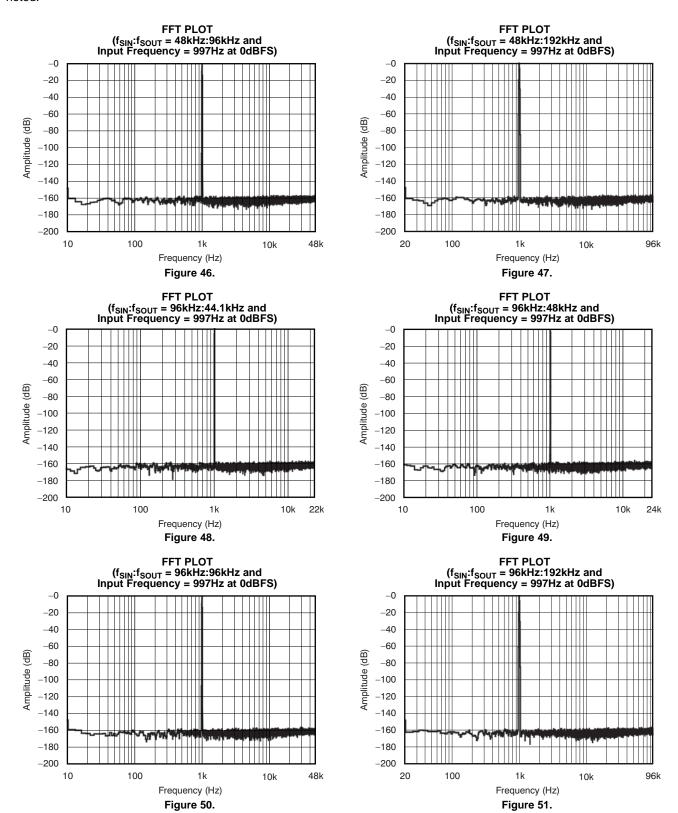

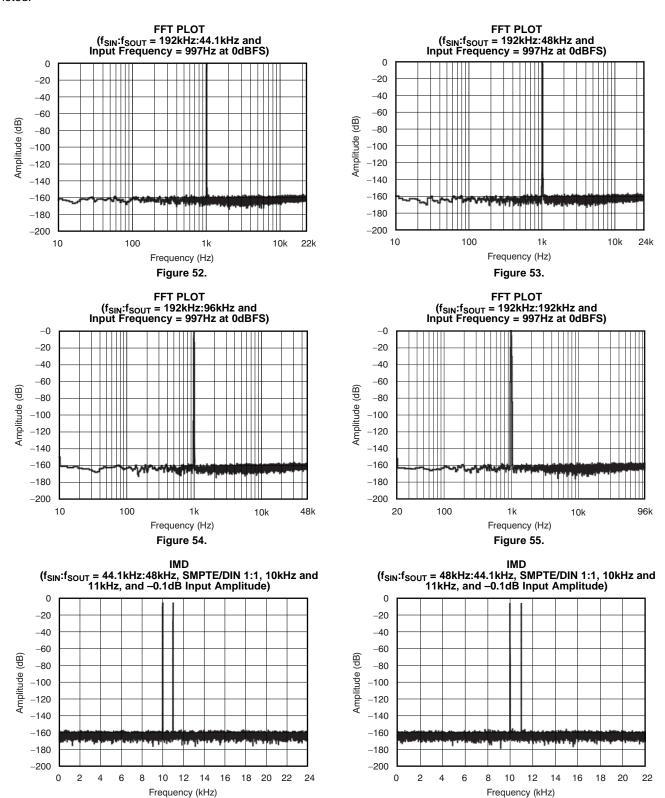

| Total Harmonic Distortion + Noise (THD+N) <sup>(2)</sup> | BW = 22Hz to $f_{SOUT}/2$ ,<br>f = 997Hz at 0dBFS |                           |         |                            |         |  |

| $f_{SIN}:f_{SOUT} = 12kHz:192kHz$                        |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 44.1kHz:44.1kHz$                     |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}$ : $f_{SOUT} = 44.1$ kHz:48kHz                  |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 44.1kHz:96kHz$                       |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 44.1kHz:192kHz$                      |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 48kHz:44.1kHz$                       |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 48kHz:48kHz$                         |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 48kHz:96kHz$                         |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}$ : $f_{SOUT} = 48$ kHz:192kHz                   |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 96kHz:44.1kHz$                       |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}$ : $f_{SOUT} = 96kHz$ :48kHz                    |                                                   |                           | -125    |                            | dB      |  |

| f <sub>SIN</sub> :f <sub>SOUT</sub> = 96kHz:96kHz        |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}$ : $f_{SOUT} = 96kHz$ :192kHz                   |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 192kHz:12kHz$                        |                                                   |                           | -125    |                            | dB      |  |

| f <sub>SIN</sub> :f <sub>SOUT</sub> = 192kHz:44.1kHz     |                                                   |                           | -125    |                            | dB      |  |

| f <sub>SIN</sub> :f <sub>SOUT</sub> = 192kHz:48kHz       |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}$ : $f_{SOUT} = 192kHz$ : $96kHz$                |                                                   |                           | -125    |                            | dB      |  |

| $f_{SIN}:f_{SOUT} = 192kHz:192kHz$                       |                                                   |                           | -125    |                            | dB      |  |

| Digital Interpolation Filter Characteristics             |                                                   |                           |         |                            |         |  |

| Passband                                                 |                                                   |                           |         | 0.4535 วf <sub>SIN</sub>   | Hz      |  |

| Passband Ripple                                          |                                                   |                           |         | 0.007                      | dB      |  |

| Transition Band                                          |                                                   | 0.4535 วf <sub>SIN</sub>  |         | 0.5465 วf <sub>SIN</sub>   | Hz      |  |

| Stop Band                                                |                                                   | 0.5465 วf <sub>SIN</sub>  |         |                            | Hz      |  |

| Stop Band Attenuation                                    |                                                   | -125                      |         |                            | dB      |  |

| Group Delay (64 samples pre-buffered)                    | Decimation filter enabled                         |                           |         | 102.53125/f <sub>SIN</sub> | Seconds |  |

| Group Delay (64 samples pre-buffered)                    | Direct down-sampling enabled                      |                           |         | 102/f <sub>SIN</sub>       | Seconds |  |

| Group Delay (32 samples pre-buffered)                    | Decimation filter enabled                         |                           |         | 70.53125/f <sub>SIN</sub>  | Seconds |  |

| Group Delay (32 samples pre-buffered)                    | Direct down-sampling enabled                      |                           |         | 70/f <sub>SIN</sub>        | Seconds |  |

| Group Delay (16 samples pre-buffered)                    | Decimation filter enabled                         |                           |         | 54.53125/f <sub>SIN</sub>  | Seconds |  |

| Group Delay (16 samples pre-buffered)                    | Direct down-sampling enabled                      |                           |         | 54/f <sub>SIN</sub>        | Seconds |  |

| Group Delay (8 samples pre-buffered)                     | Decimation filter enabled                         |                           |         | 46.53125/f <sub>SIN</sub>  | Seconds |  |

| Group Delay (8 samples pre-buffered)                     | Direct down-sampling enabled                      |                           |         | 46/f <sub>SIN</sub>        | Seconds |  |

| Digital Decimation Filter Characteristics                |                                                   |                           |         |                            |         |  |

| Passband                                                 |                                                   |                           |         | 0.4535 มf <sub>SOUT</sub>  | Hz      |  |

| Passband Ripple                                          |                                                   |                           |         | 0.008                      | dB      |  |

| Transition Band                                          |                                                   | 0.4535 มf <sub>SOUT</sub> |         | 0.5465 มf <sub>SOUT</sub>  | Hz      |  |

| Stop Band                                                |                                                   | 0.5465 ıf <sub>SOUT</sub> |         |                            | Hz      |  |

| Stop Band Attenuation                                    |                                                   | -125                      |         |                            | dB      |  |

| Group Delay                                              | Decimation filter enabled                         |                           |         | 36.46875/f <sub>SOUT</sub> | Seconds |  |

| Group Delay                                              | Direct down-sampling enabled                      |                           |         | 0                          | Seconds |  |

| Digital De-Emphasis Filter Characteristics               |                                                   |                           |         |                            |         |  |

| Filter Error for All Settings                            | De-emphasis filter enabled                        |                           |         | 0.001                      | dB      |  |

<sup>(2)</sup> Measured with an Audio Precision SYS-2722 192kHz test system with the input and output sampling frequencies asynchronous to one another.

# **ELECTRICAL CHARACTERISTICS: General, SRC, DIR, and DIT (continued)**

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

|                                                                |                         |     | SRC4382 |      |        |

|----------------------------------------------------------------|-------------------------|-----|---------|------|--------|

| PARAMETER                                                      | CONDITIONS              | MIN | TYP     | MAX  | UNITS  |

| DIGITAL AUDIO INTERFACE RECEIVER (DIR)                         |                         |     |         |      |        |

| PLL Lock Range                                                 |                         | 20  |         | 216  | kHz    |

| Reference Clock Input (RXCKI) Frequency, f <sub>RXCKI</sub>    |                         | 3.5 |         | 27.7 | MHz    |

| Reference Clock Input (RXCKI) Duty Cycle, f <sub>RXCKID</sub>  |                         | 45  |         | 55   | %      |

| Recovered Clock Output (RXCKO) Frequency, f <sub>RXCKO</sub>   |                         | 3.5 |         | 27.7 | MHz    |

| Recovered Clock Output (RXCKO) Duty Cycle, f <sub>RXCKOD</sub> |                         | 45  |         | 55   | %      |

| Recovered Clock Output (RXCKO) Intrinsic Jitter                | Measured cycle-to-cycle |     | 250     |      | ps RMS |

| DIGITAL AUDIO INTERFACE TRANSMITTER (DIT)                      |                         |     |         |      |        |

| Intrinsic Output Jitter                                        | Measured cycle-to-cycle |     | 200     |      | ps RMS |

#### **ELECTRICAL CHARACTERISTICS: Audio Serial Ports**

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

|                                                      |            |     | SRC4382 |        |       |

|------------------------------------------------------|------------|-----|---------|--------|-------|

| PARAMETER                                            | CONDITIONS | MIN | TYP     | MAX    | UNITS |

| AUDIO SERIAL PORTS (Port A and Port B)               |            |     |         |        |       |

| LRCK Clock Frequency, f <sub>LRCK</sub>              |            | 0   |         | 216    | kHz   |

| LRCK Clock Duty Cycle, t <sub>LRCKD</sub>            |            |     | 50      |        | %     |

| BCK Clock Frequency, f <sub>BCK</sub>                |            | 0   |         | 13.824 | MHz   |

| BCK High Pulse Width, t <sub>BCKH</sub>              |            | 10  |         |        | ns    |

| BCK Low Pulse Width, t <sub>BCKL</sub>               |            | 10  |         |        | ns    |

| Audio Data Input (SDIN) Setup Time, t <sub>AIS</sub> |            | 10  |         |        | ns    |

| Audio Data Input (SDIN) Hold Time, t <sub>AISH</sub> |            | 10  |         |        | ns    |

| Audio Data Output (SDOUT) Delay, t <sub>ADD</sub>    |            |     |         | 10     | ns    |

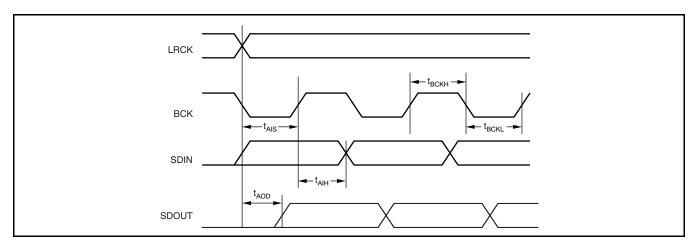

#### **ELECTRICAL CHARACTERISTICS: SPI Interface**

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

|                                                     |            |     | SRC4382 |     |       |

|-----------------------------------------------------|------------|-----|---------|-----|-------|

| PARAMETER                                           | CONDITIONS | MIN | TYP     | MAX | UNITS |

| HOST INTERFACE: SPI Mode                            |            |     |         |     |       |

| Serial Clock (CCLK) Frequency, f <sub>CCLK</sub>    |            | 0   |         | 40  | MHz   |

| CS Falling to CCLK Rising, t <sub>CSCR</sub>        |            | 8   |         |     | ns    |

| CCLK Falling to CS Rising, t <sub>CFCS</sub>        |            | 7   |         |     | ns    |

| CDIN Data Setup Time, t <sub>CDS</sub>              |            | 7   |         |     | ns    |

| CDIN Data Hold Time, t <sub>CDH</sub>               |            | 6   |         |     | ns    |

| CCLK Falling to CDOUT Data Valid, t <sub>CFDO</sub> |            |     |         | 3   | ns    |

| CS Rising to CDOUT High-Impedance, t <sub>CSZ</sub> |            |     |         | 3   | ns    |

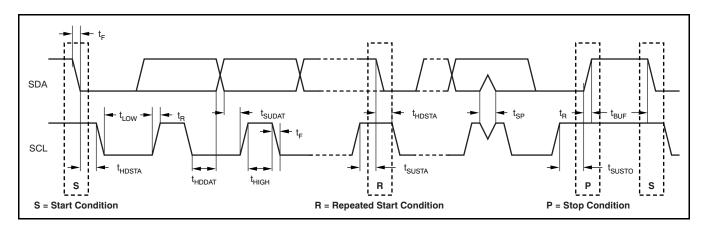

# ELECTRICAL CHARACTERISTICS: I<sup>2</sup>C Standard and Fast Modes

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

|                                                                    |            | S                                     | SRC4382 |                     |       |

|--------------------------------------------------------------------|------------|---------------------------------------|---------|---------------------|-------|

| PARAMETER                                                          | CONDITIONS | MIN                                   | TYP     | MAX                 | UNITS |

| HOST INTERFACE: I <sup>2</sup> C Standard Mode <sup>(1)</sup>      |            |                                       |         |                     |       |

| SCL Clock Frequency, f <sub>SCL</sub>                              |            | 0                                     |         | 100                 | kHz   |

| Hold Time Repeated START Condition, t <sub>HDSTA</sub>             |            | 4                                     |         |                     | μs    |

| Low Period of SCL Clock, t <sub>LOW</sub>                          |            | 4.7                                   |         |                     | μs    |

| High Period of SCL Clock, t <sub>HIGH</sub>                        |            | 4                                     |         |                     | μs    |

| Setup Time Repeated START Condition, t <sub>SUSTA</sub>            |            | 4.7                                   |         |                     | μs    |

| Data Hold Time, t <sub>HDDAT</sub>                                 |            | 0 <sup>(2)</sup>                      |         | 3.45 <sup>(3)</sup> | μs    |

| Data Setup Time, t <sub>SUDAT</sub>                                |            | 250                                   |         |                     | ns    |

| Rise Time for Both SDA and SDL, t <sub>R</sub>                     |            |                                       |         | 1000                | ns    |

| Fall Time for Both SDA and SDL, t <sub>F</sub>                     |            |                                       |         | 300                 | ns    |

| Setup Time for STOP Condition, t <sub>SUSTO</sub>                  |            | 4                                     |         |                     | μs    |

| Bus Free Time Between START and STOP, t <sub>BUF</sub>             |            | 4.7                                   |         |                     | μs    |

| Capacitive Load for Each Bus Line, C <sub>B</sub>                  |            |                                       |         | 400                 | pF    |

| Noise Margin at Low Level (including hysteresis), V <sub>NL</sub>  |            | VIOد 0.1                              |         |                     | V     |

| Noise Margin at High Level (including hysteresis), V <sub>NH</sub> |            | 0.2 نVIO                              |         |                     | V     |

| HOST INTERFACE: I <sup>2</sup> C Fast Mode <sup>(1)</sup>          |            |                                       |         |                     |       |

| SCL Clock Frequency, f <sub>SCL</sub>                              |            | 0                                     |         | 400                 | kHz   |

| Hold Time Repeated START Condition, t <sub>HDSTA</sub>             |            | 0.6                                   |         |                     | μs    |

| Low Period of SCL Clock, t <sub>LOW</sub>                          |            | 1.3                                   |         |                     | μs    |

| High Period of SCL Clock, t <sub>HIGH</sub>                        |            | 0.6                                   |         |                     | μs    |

| Setup Time Repeated START Condition, t <sub>SUSTA</sub>            |            | 0.6                                   |         |                     | μs    |

| Data Hold Time, t <sub>HDDAT</sub>                                 |            | 0 <sup>(2)</sup>                      |         | 0.9(3)              | μs    |

| Data Setup Time, t <sub>SUDAT</sub>                                |            | 100 <sup>(4)</sup>                    |         |                     | ns    |

| Rise Time for Both SDA and SDL, t <sub>R</sub>                     |            | 20 + 0.2C <sub>B</sub> <sup>(5)</sup> |         | 300                 | ns    |

| Fall Time for Both SDA and SDL, t <sub>F</sub>                     |            | $20 + 0.2C_B^{(5)}$                   |         | 300                 | ns    |

| Setup Time for STOP Condition, t <sub>SUSTO</sub>                  |            | 0.6                                   |         |                     | μs    |

| Bus Free Time Between START and STOP, t <sub>BUF</sub>             |            | 1.3                                   |         |                     | μs    |

| Spike Pulse Width Suppressed by Input Filter, t <sub>SP</sub>      |            | 0                                     |         | 50                  | ns    |

| Capacitive Load for Each Bus Line, C <sub>B</sub>                  |            |                                       |         | 400                 | pF    |

| Noise Margin at Low Level (including hysteresis), V <sub>NL</sub>  |            | 0.1 υVIO                              |         |                     | V     |

| Noise Margin at High Level (including hysteresis), V <sub>NH</sub> |            | VIO د 0.2                             |         |                     | V     |

<sup>(1)</sup> All values referred to the V<sub>IH</sub> minimum and V<sub>IL</sub> maximum levels listed in the Digital I/O Characteristics section of the *Electrical Characteristics: General, SRC, DIR, and DIT* table.

<sup>(2)</sup> A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH</sub> minimum input level) to bridge the undefined region of the falling edge of SCL.

<sup>(3)</sup> The maximum t<sub>HDDAT</sub> has only to be met if the device does not stretch the Low period (t<sub>LOW</sub>) of the SCL signal.

<sup>(4)</sup> A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement that t<sub>SUDAT</sub> be 250ns minimum must then be met. For the SRC4382, this is automatically the case, since the device does not stretch the Low period of the SCL signal.

<sup>(5)</sup> C<sub>B</sub> is defined as the total capacitance of one bus line in picofarads (pF). If mixed with High-Speed mode devices, faster fall times are allowed.

# **ELECTRICAL CHARACTERISTICS: Power Supplies**

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

| PARAMETER                                   | CONDITIONS                                     | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------------|------------------------------------------------|-------|------|-------|-------|

| POWER SUPPLIES                              |                                                |       |      |       |       |

| Recommended Supply Voltage Range            |                                                |       |      |       |       |

| VDD18                                       |                                                | +1.65 | +1.8 | +1.95 | V     |

| VDD33                                       |                                                | +3.0  | +3.3 | +3.6  | V     |

| VIO                                         |                                                | +1.65 | +3.3 | +3.6  | V     |

| VCC                                         |                                                | +3.0  | +3.3 | +3.6  | V     |

| Supply Current: Initial Startup             | All Blocks Powered Down by Default             |       |      |       |       |

| IDD18S                                      | VDD18 = +1.8V                                  |       | 90   |       | μA    |

| IDD33S                                      | VDD33 = +3.3V                                  |       | 1    |       | μA    |

| IIOS                                        | VIO = +3.3V                                    |       | 270  |       | μA    |

| ICCS                                        | VCC = +3.3V                                    |       | 1    |       | μA    |

| Supply Current: Quiescent                   | All Blocks Powered Up with No Clocks Applied   |       |      |       |       |

| IDD18Q                                      | VDD18 = +1.8V                                  |       | 3.1  |       | mA    |

| IDD33Q                                      | VDD33 = +3.3V                                  |       | 0.5  |       | mA    |

| IIOQ                                        | VIO = +3.3V                                    |       | 0.27 |       | mA    |

| ICCQ                                        | VCC = +3.3V                                    |       | 6.6  |       | mA    |

| Supply Current: Dynamic                     | All Blocks Powered Up, f <sub>S</sub> = 48kHz  |       |      |       |       |

| IDD18D                                      | VDD18 = +1.8V                                  |       | 23   |       | mA    |

| IDD33D                                      | VDD33 = +3.3V                                  |       | 14   |       | mA    |

| IIOD <sup>(1)</sup>                         | VIO = +3.3V                                    |       | 43   |       | mA    |

| ICCD                                        | VCC = +3.3V                                    |       | 8    |       | mA    |

| Supply Current: High Sampling Rate          | All Blocks Powered Up, f <sub>S</sub> = 192kHz |       |      |       |       |

| IDD18H                                      | VDD18 = +1.8V                                  |       | 58   |       | mA    |

| IDD33H                                      | VDD33 = +3.3V                                  |       | 15   |       | mA    |

| IIOH <sup>(1)</sup>                         | VIO = +3.3V                                    |       | 44   |       | mA    |

| ICCH                                        | VCC = +3.3V                                    |       | 8    |       | mA    |

| Total Power Dissipation: Initial Startup    | All Blocks Powered Down by Default             |       | 1    |       | mW    |

| Total Power Dissipation: Quiescent          | All Blocks Powered Up with No Clocks Applied   |       | 30   |       | mW    |

| Total Power Dissipation: Dynamic            | All Blocks Powered Up, f <sub>S</sub> = 48kHz  |       | 256  |       | mW    |

| Total Power Dissipation: High Sampling Rate | All Blocks Powered Up, f <sub>S</sub> = 192kHz |       | 326  |       | mW    |

<sup>(1)</sup> The typical VIO supply current is measured using the SRC4382EVM evaluation module with loading from the DAIMB mother-board circuitry. VIO supply current will be dependent upon the loading on the logic output pins.

## **TIMING DIAGRAMS**

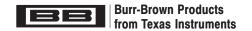

Figure 1. Audio Serial Port Timing

Figure 2. SPI Interface Timing

Figure 3. I<sup>2</sup>C Standard and Fast Mode Timing

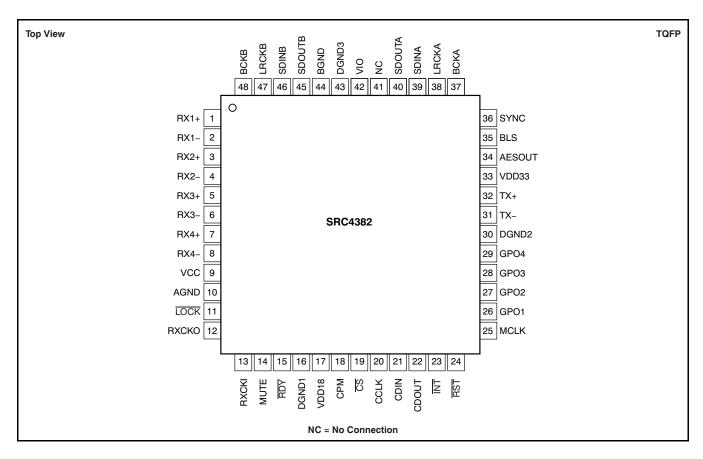

## **PIN CONFIGURATION**

## **PIN DESCRIPTIONS**

|              |            |        | T                                                                                             |

|--------------|------------|--------|-----------------------------------------------------------------------------------------------|

| NAME         | PIN NUMBER | I/O    | DESCRIPTION                                                                                   |

| RX1+         | 1          | Input  | Line Receiver 1, Noninverting Input                                                           |

| RX1-         | 2          | Input  | Line Receiver 1, Inverting Input                                                              |

| RX2+         | 3          | Input  | Line Receiver 2, Noninverting Input                                                           |

| RX2-         | 4          | Input  | Line Receiver 2, Inverting Input                                                              |

| RX3+         | 5          | Input  | Line Receiver 3, Noninverting Input                                                           |

| RX3-         | 6          | Input  | Line Receiver 3, Inverting Input                                                              |

| RX4+         | 7          | Input  | Line Receiver 4, Noninverting Input                                                           |

| RX4-         | 8          | Input  | Line Receiver 4, Inverting Input                                                              |

| VCC          | 9          | Power  | DIR Comparator and PLL Power Supply, +3.3V Nominal                                            |

| AGND         | 10         | Ground | DIR Comparator and PLL Power-Supply Ground                                                    |

| LOCK         | 11         | Output | DIR PLL Lock Flag (active Low)                                                                |

| RXCKO        | 12         | Output | DIR Recovered Master Clock (tri-state output)                                                 |

| RXCKI        | 13         | Input  | DIR Reference Clock                                                                           |

| MUTE         | 14         | Input  | SRC Output Mute (active High)                                                                 |

| RDY          | 15         | Output | SRC Ready Flag (active Low)                                                                   |

| DGND1        | 16         | Ground | Digital Core Ground                                                                           |

| VDD18        | 17         | Power  | Digital Core Supply, +1.8V Nominal                                                            |

| CPM          | 18         | Input  | Control Port Mode, 0 = SPI Mode, 1 = I <sup>2</sup> C Mode                                    |

| CS or A0     | 19         | Input  | Chip Select (active Low) for SPI Mode or Programmable Slave Address for I <sup>2</sup> C Mode |

| CCLK or SCL  | 20         | Input  | Serial Data Clock for SPI Mode or I <sup>2</sup> C Mode                                       |

| CDIN orA1    | 21         | Input  | SPI Port Serial Data input or Programmable Slave Address for I <sup>2</sup> C Mode            |

| CDOUT or SDA | 22         | I/O    | SPI Port Serial Data Output (tri-state output) or Serial Data I/O for I <sup>2</sup> C Mode   |

Submit Documentation Feedback

Copyright © 2006–2007, Texas Instruments Incorporated

# PIN DESCRIPTIONS (continued)

| NAME   | PIN NUMBER | 1/0    | DESCRIPTION                                                      |

|--------|------------|--------|------------------------------------------------------------------|

| INT    | 23         | Output | Interrupt Flag (open-drain, active Low)                          |

| RST    | 24         | Input  | Reset (active Low)                                               |

| MCLK   | 25         | Input  | Master Clock                                                     |

| GPO1   | 26         | Output | General-Purpose Output 1                                         |

| GPO2   | 27         | Output | General-Purpose Output 2                                         |

| GPO3   | 28         | Output | General-Purpose Output 3                                         |

| GPO4   | 29         | Output | General-Purpose Output 4                                         |

| DGND2  | 30         | Ground | DIR Line Receiver Bias and DIT Line Driver Digital Ground        |

| TX-    | 31         | Output | DIT Line Driver Inverting Output                                 |

| TX+    | 32         | Output | DIT Line Driver Noninverting Output                              |

| VDD33  | 33         | Power  | DIR Line Receiver Bias and DIT Line Driver Supply, +3.3V Nominal |

| AESOUT | 34         | Output | DIT Buffered AES3-Encoded Data                                   |

| BLS    | 35         | I/O    | DIT Block Start Clock                                            |

| SYNC   | 36         | Output | DIT internal Sync Clock                                          |

| BCKA   | 37         | I/O    | Audio Serial Port A Bit Clock                                    |

| LRCKA  | 38         | 1/0    | Audio Serial Port A Left/Right Clock                             |

| SDINA  | 39         | Input  | Audio Serial Port A Data Input                                   |

| SDOUTA | 40         | Output | Audio Serial Port A Data Output                                  |

| NC     | 41         | _      | No Internal Signal Connection, Internally Bonded to ESD Pad      |

| VIO    | 42         | Power  | Logic I/O Supply, +1.65V to +3.6V                                |

| DGND3  | 43         | Ground | Logic I/O Ground                                                 |

| BGND   | 44         | Ground | Substrate Ground, Connect to AGND (pin 10)                       |

| SDOUTB | 45         | Output | Audio Serial Port B Data Output                                  |

| SDINB  | 46         | Input  | Audio Serial Port B Data Input                                   |

| LRCKB  | 47         | I/O    | Audio Serial Port B Left/Right Clock                             |

| ВСКВ   | 48         | I/O    | Audio Serial Port B Bit Clock                                    |

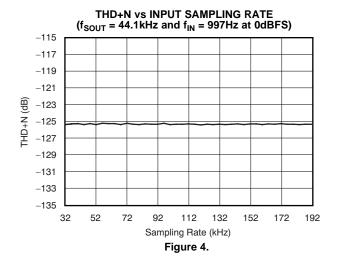

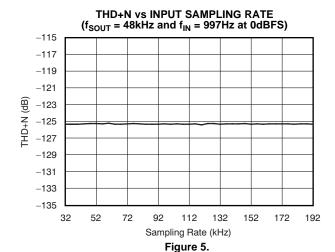

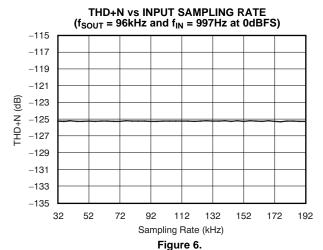

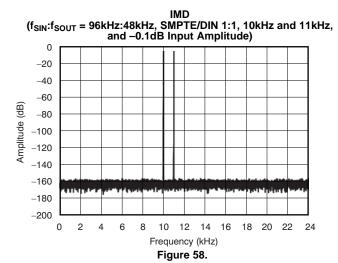

#### TYPICAL CHARACTERISTICS

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

Copyright © 2006–2007, Texas Instruments Incorporated

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

Figure 20.

Figure 21.

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

All specifications are at T<sub>A</sub> = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

All specifications are at  $T_A = +25C$ , VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

e 34. Figure 35.

Copyright © 2006–2007, Texas Instruments Incorporated

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

Figure 56.

Figure 57.

All specifications are at  $T_A$  = +25C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

Submit Documentation Feedback

21

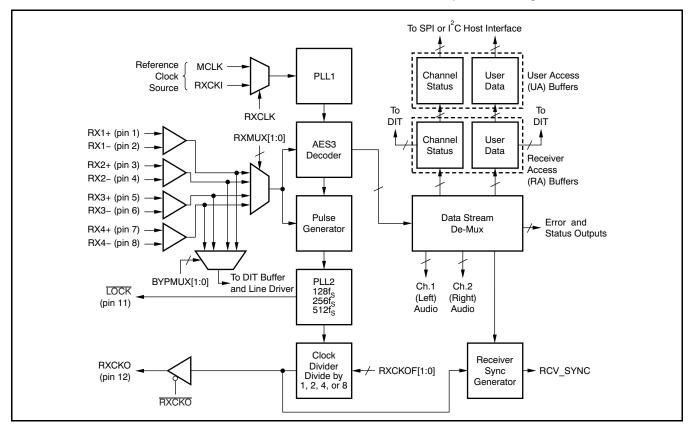

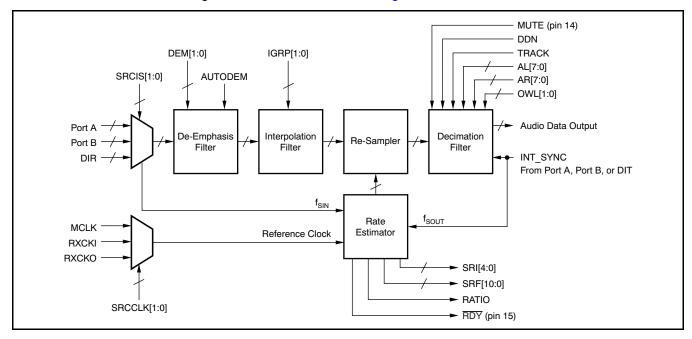

#### PRODUCT OVERVIEW

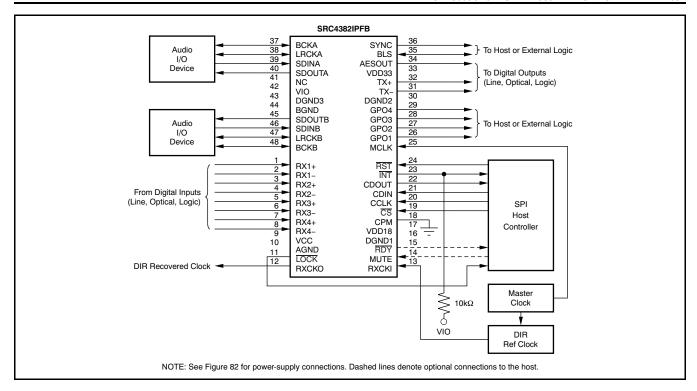

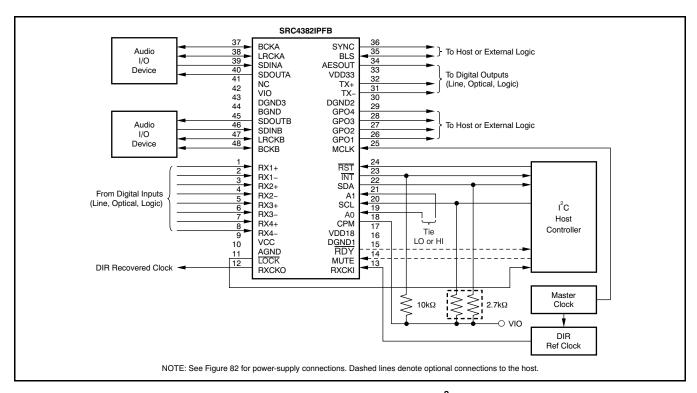

The SRC4382 is a two-channel asynchronous sample rate converter (SRC) with an integrated digital audio interface receiver and transmitter (DIR and DIT). Two audio serial ports, Port A and Port B, support input and output interfacing to external data converters, signal processors, and logic devices. On-chip routing logic provides for flexible interconnection between the five functional blocks. The audio serial ports, DIT, and SRC may be operated at sampling rates up to 216kHz. The DIR is specified for a PLL lock range that includes sampling rates from 20kHz to 216kHz. All function blocks support audio data word lengths up to 24 bits.

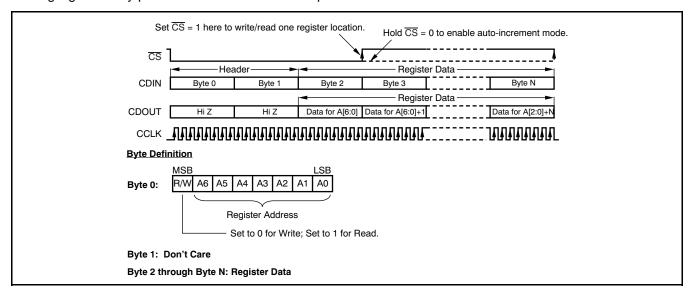

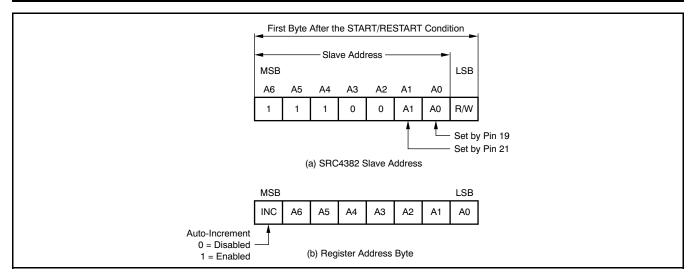

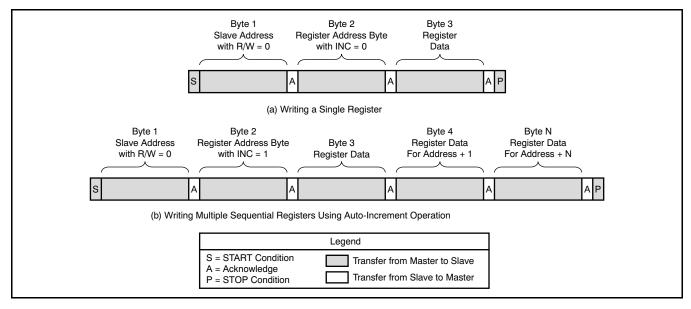

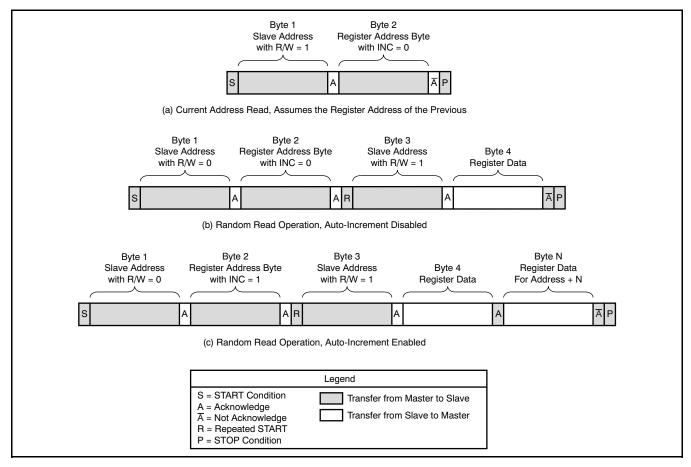

The SRC4382 requires an external host processor or logic for configuration control. The SRC4382 includes a user-selectable serial host interface, which operates as either a 4-wire serial peripheral interface (SPI) port or a 2-wire Philips I<sup>2</sup>C bus interface. The SPI port operates at bit rates up to 40MHz. The I<sup>2</sup>C bus interface may be operated in standard or fast modes, supporting operation at 100kbps and 400kbps, respectively. The SPI and I<sup>2</sup>C interfaces provide access to internal control and status registers, as well as the buffers utilized for the DIR and DIT channel status and user data.

The asynchronous SRC is based upon the successful SRC4192 core from Texas Instruments. The SRC in the SRC4382 has been further enhanced to provide exceptional jitter attenuation characteristics, helping to improve overall application performance. The SRC operates over a wide input-to-output sampling ratio range, from 1:16 to 16:1 continuous. The input-to-output sampling ratio is determined automatically by the SRC rate estimation circuitry, with the digital re-sampler parameters being updated in real-time without the need for programming. Interpolation and decimation filter delay are user-selectable. Additional SRC features include de-emphasis filtering, output word length reduction, output attenuation and muting, and input-to-output sampling ratio readback via status registers.

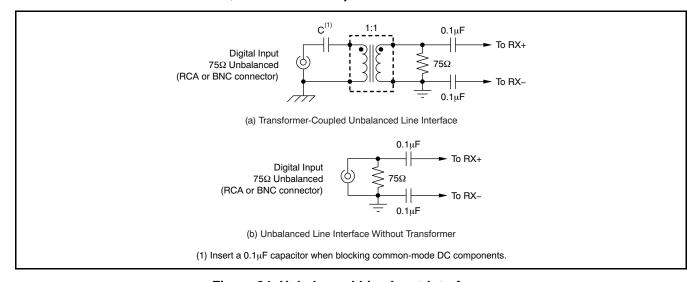

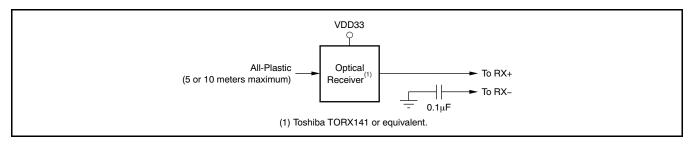

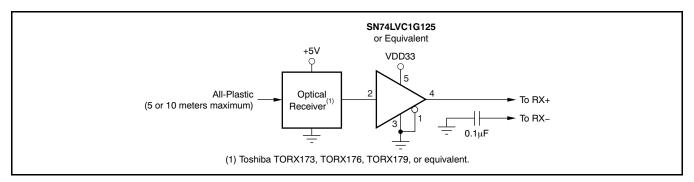

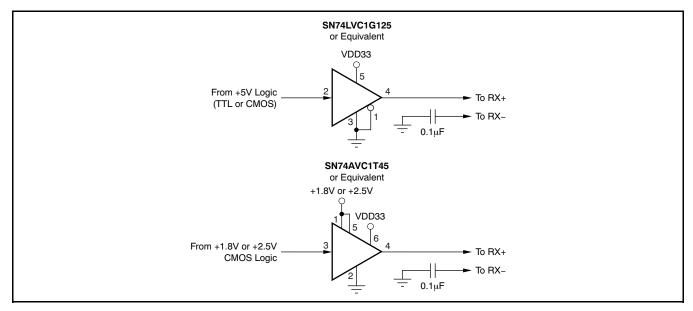

The digital interface receiver (DIR) includes four differential input line receiver circuits, suitable for balanced or unbalanced cable interfaces. Interfacing to optical receiver modules and CMOS logic devices is also supported. The outputs of the line receivers are connected to a 1-of-4 data selector, referred to as the receiver input multiplexer, which is utilized to select one of the four line receiver outputs for processing by the DIR core. The outputs of the line receivers are also connected to a second data selector, the bypass multiplexer, which may be used to route input data streams to the DIT CMOS output buffer and differential line driver functions. This configuration provides a bypass signal path for AES3-encoded input data streams.

The DIR core decodes the selected input stream data and separates the audio, channel status, user, validity, and parity data. Channel status and user data is stored in block-sized buffers, which may be accessed via the SPI or I<sup>2</sup>C serial host interface, or routed directly to the general-purpose output pins (GPO1 through GPO4). The validity and parity bits are processed to determine error status. The DIR core recovers a low jitter master clock, which may be utilized to generate word and bit clocks using on-chip or external logic circuitry.

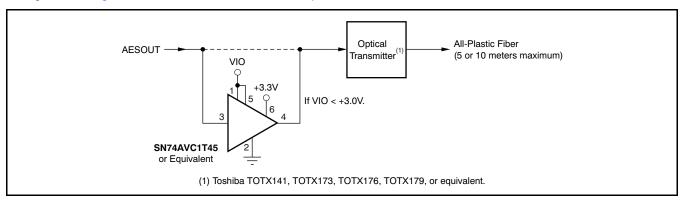

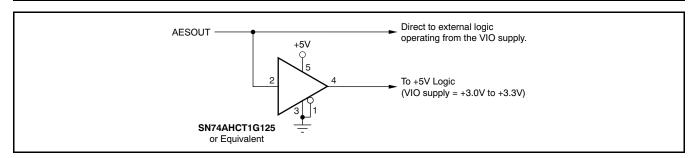

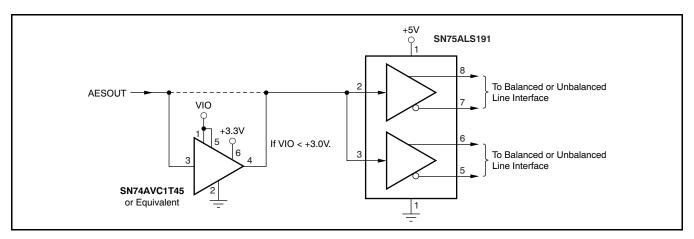

The digital interface transmitter (DIT) encodes digital audio input data into an AES3 formatted output data stream. Two DIT outputs are provided, including a differential line driver and a CMOS output buffer. Both the line driver and buffer include 1-of-2 input data selectors, which are utilized to choose either the output of the DIT AES3 encoder, or the output of the bypass multiplexer. The line driver output is suitable for balanced or unbalanced cable interfaces, while the CMOS output buffer supports interfacing to optical transmitter modules and external logic or line drivers. The DIT includes block-sized data buffers for both channel status and user data. These buffers are accessed via either the SPI or I<sup>2</sup>C host interface, or may be loaded directly from the DIR channel status and user data buffers.

The SRC4382 includes four general-purpose digital outputs, or GPO pins. The GPO pins may be configured as simple logic outputs, which may be programmed to either a low or high state. Alternatively, the GPO pins may be connected to one of 14 internal logic nodes, allowing them to serve as functional, status, or interrupt outputs. The GPO pins provide added utility in applications where hardware access to selected internal logic signals may be necessary.

22

Figure 59 shows a simplified functional block diagram for the SRC4382. Additional details for each function block will be covered in respective sections of this datasheet.

Figure 59. Functional Block Diagram

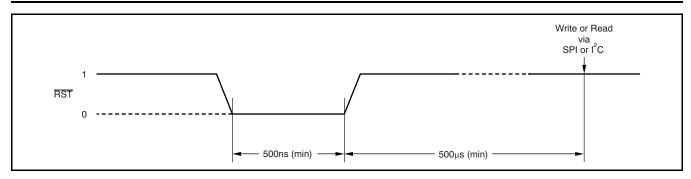

#### **RESET OPERATION**

The SRC4382 includes an asynchronous active low reset input, RST (pin 24), which may be used to initialize the internal logic at any time. The reset sequence forces all registers and buffers to their default settings. The reset low pulse width must be a minimum of 500ns in length. The user should not attempt a write or read operation using either the SPI or I<sup>2</sup>C port for at least 500µs after the rising edge of RST. See Figure 60 for the reset timing sequence of the SRC4382.

In addition to reset input, the RESET bit in control register 0x01 may be used to force an internal reset, whereby all registers and buffers are forced to their default settings. Refer to the Control Registers section for details regarding the RESET bit function.

Upon reset initialization, all functional blocks of the SRC4382 default to the powered-down state, with the exception of the SPI or I<sup>2</sup>C host interface and the corresponding control registers. The user may then program the SRC4382 to the desired configuration, and then release the desired function blocks from the power-down state utilizing the corresponding bits in control register 0x01.

Figure 60. Reset Sequence Timing

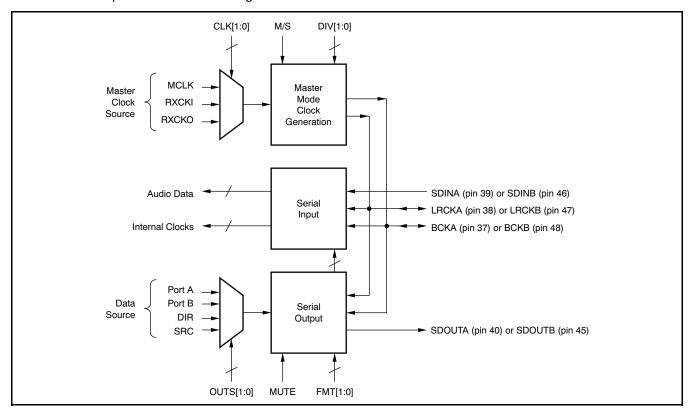

#### MASTER AND REFERENCE CLOCKS

The SRC4382 includes two clock inputs, MCLK (pin 25) and RXCKI (pin 13). The MCLK clock input is typically used as the master clock source for the audio serial ports, the DIT, and/or the SRC. The MCLK may also be utilized as the reference clock for the DIR. The RXCKI clock input is typically used for the DIR reference clock source, although it may also be used as the master or reference clock source for the audio serial ports and/or the SRC.

In addition to the MCLK and RXCKI clock sources, the DIR core recovers a master clock from the AES3-encoded input data stream. This clock is suitable for use as a master or system clock source in many applications. The recovered master clock output, RXCKO (pin 12), may be utilized as the master or reference clock source for the audio serial ports, the DIT, and/or the SRC, as well as external audio devices.

The master clock frequency for the audio serial ports (Port A and Port B) depends on the Slave or Master mode configuration of the port. In Slave mode, the ports do not require a master clock, as the left/right word and bit clocks are inputs, sourced from an external audio device serving as the serial bus timing master. In Master mode, the serial ports derive the left/right word and bit clock outputs from the selected master clock source, MCLK, RXCKI, or RXCKO. The left/right word clock rate is derived from the selected master clock source using one of four clock divider settings (divide by 128, 256, 384, or 512). Refer to the Audio Serial Port Operation section for additional details.

The DIT always requires a master clock source, which may be either the MCLK input, or the DIR recovered clock output, RXCKO. Like the audio serial ports, the DIT output frame rate is derived from the selected master clock using one of four clock divider settings (divide by 128, 256, 384, or 512). Refer to the Digital Interface Transmitter (DIT) Operation section for additional details.

The DIR reference clock may be any frequency that meets the PLL1 setup requirements, described in the Control Registers section. Typically, a common audio system clock rate, such as 11.2896MHz, 12.288MHz, 22.5792MHz, or 24.576MHz, may be used for this clock.

The SRC reference clock rate may be any frequency up to 27.7MHz, and does not have to be related to or synchronous with the input or output sampling rates. The MCLK, RXCKI, or RXCKO clocks may be utilized as the reference clock source for the SRC. Refer to the Asynchronous Sample Rate Converter (SRC) Operation section for additional details.

It is recommended that the clock sources for MCLK and RXCKI input be generated by low-jitter crystal oscillators for optimal performance. In general, phase-locked loop (PLL) clock synthesizers should be avoided, unless they are designed and/or specified for low clock jitter.

#### **AUDIO SERIAL PORT OPERATION**

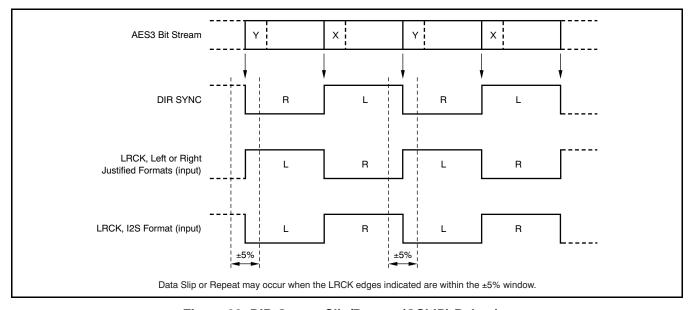

The SRC4382 includes two audio serial ports, Port A and Port B. Both ports are 4-wire synchronous serial interfaces, supporting simultaneous input and output operation. Since each port has only one pair of left/right word and bit clocks, the input and output sampling rates are identical. A simplified block diagram is shown in Figure 61.

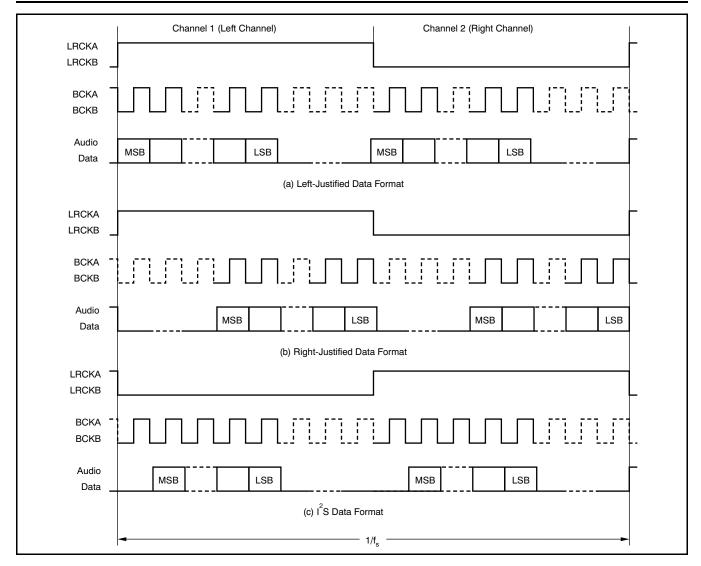

The audio serial ports may be operated at sampling rates up to 216kHz, and support audio data word lengths up to 24 bits. Philips I<sup>2</sup>S, Left-Justified, and Right-Justified serial data formats are supported. Refer to Figure 62.

The left/right word clock (LRCKA or LRCKB) and the bit clock (BCKA or BCKB) may be configured for either Master or Slave mode operation. In Master mode these clocks are outputs, derived from the selected master clock source using internal clock dividers. The master clock source may be 128, 256, 384, or 512 times the audio input/output sampling rate, with the clock divider being selected using control register bits for each port. In Slave mode the left/right word and bit clocks are inputs, being sourced from an external audio device acting as the serial bus master.

The LRCKA or LRCKB clocks operate at the input/output sampling rate, f<sub>S</sub>. The BCKA and BCKB clock rates are fixed at 64 times the left/right word clock rate in Master mode. For Slave mode, the minimum BCKA and BCKB clock rate is determined by the audio data word length multiplied by two, since there are two audio data channels per left/right word clock period. For example, if the audio data word length is 24 bits, the bit clock rate must be at least 48 times the left/right word clock rate, allowing one bit clock period for each data bit in the serial bit stream.

Serial audio data is clocked into the port on the rising edge of the bit clock, while data is clocked out of the port on the falling edge of the bit clock. Refer to the Electrical Characteristics: Audio Serial Ports table for parametric information and Figure 1 for a timing diagram related to audio serial port operation.

The audio serial ports are configured using control registers 0x03 through 0x06. Refer to the Control Registers section for descriptions of the control register bits.

Figure 61. Audio Serial Port Block Diagram

Figure 62. Audio Data Formats

#### **OVERVIEW OF THE AES3 DIGITAL AUDIO INTERFACE PROTOCOL**

This section introduces the basics of digital audio interface protocols pertaining to the transmitter (DIT) and receiver (DIR) blocks of the SRC4382. Emphasis is placed upon defining the basic terminology and characteristics associated with the AES3-2003 standard protocol, the principles of which may also be applied to a number of consumer-interface variations, including S/PDIF, IEC-60958, and EIAJ CP-1201. It is assumed that the reader is familiar with the AES3 and S/PDIF interface formats. Additional information is available from the sources listed in the Reference Documents section.

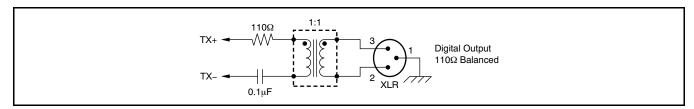

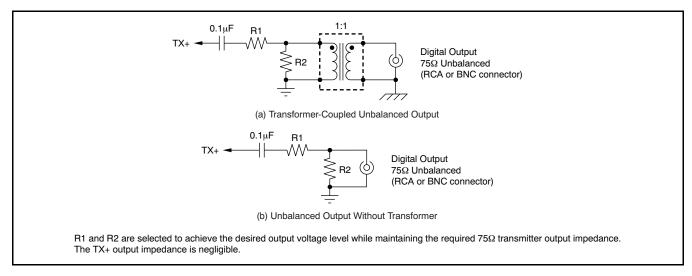

The AES3-2003 standard defines a technique for two-channel linear PCM data transmission over  $110\Omega$  shielded twisted-pair cable. The AES-3id document extends the AES3 interface to applications employing  $75\Omega$  coaxial cable connections. In addition, consumer transmission variants, such as those defined by the S/PDIF, IEC 60958, and CP-1201 standards, utilize the same encoding techniques but with different physical interfaces or transmission media. Channel status data definitions also vary between professional and consumer interface implementations.

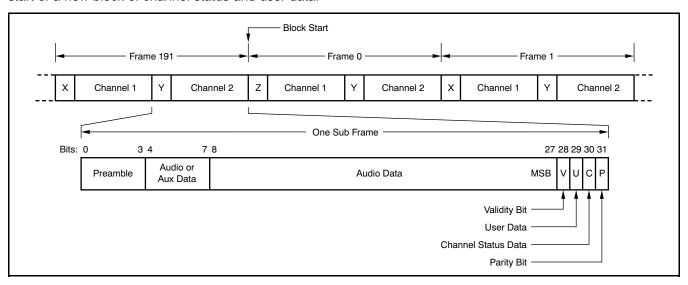

For AES3 transmission, data is encoded into frames, with each frame containing two subframes of audio and status data, corresponding to audio Channels 1 and 2 (or Left and Right, respectively, for stereophonic audio). Figure 63 shows the AES3 frame and subframe formatting. Each subframe includes four bits for the preamble, up to 24 bits for audio and/or auxiliary data, one bit indicating data validity (V), one bit for channel status data (C), one bit for user data (U), and one bit for setting parity (P).

The 4-bit preamble is used for synchronization and identification of blocks and subframes. The X and Y preamble codes are used to identify the start of the Channel 1 and Channel 2 subframes, as shown in Figure 63. However, the X preamble for the first subframe of every 192 frames is replaced by the Z preamble, which identifies the start of a new block of channel status and user data.

Figure 63. AES3 Frame and Subframe Encoding

One block is comprised of 192 frames of data. This format translates to 192 bits each for channel status and user data for each channel. The 192 bits are organized into 24 data bytes, which are defined by the AES3-2003 and consumer standards documents. The AES18 standard defines recommended usage and formatting of the user data bits, while consumer applications may utilize the user data for other purposes. The SRC4382 also includes block-sized transmitter and receiver channel status and user data buffers, which have 24 bytes each for the channel status and user data assigned to audio Channels 1 and 2. Refer to the Channel Status and User Data Buffer Maps section for the organization of the buffered channel status and user data for the receiver and transmitter functions.

The audio data for Channel 1 and Channel 2 may be up to 24 bits in length, and occupies bits 4 through 27 of the corresponding subframe. Bit 4 is the LSB while bit 27 is the MSB. If only 20 bits are required for audio data, then bits 8 through 27 are utilized for audio data, while bits 4 though 7 are utilized for auxiliary data bits.

The validity (V) bit indicates whether or not the audio sample word being transmitted is suitable for digital-to-analog (D/A) conversion or further digital processing at the receiver end of the connection. If the validity bit is 0, then the audio sample is suitable for conversion or additional processing. If the validity bit is 1, then the audio sample is not suitable for conversion or additional processing.

The parity (P) bit is set to either a 0 or 1, such that bits 4 through 31 carry an even number of ones and zeros for even parity. The DIT block in the SRC4382 automatically manages the parity bit, setting it to a 0 or 1 as needed. The DIR block checks the parity of bits 4 though 31 and generates a parity error if odd parity is detected.

Copyright © 2006–2007, Texas Instruments Incorporated

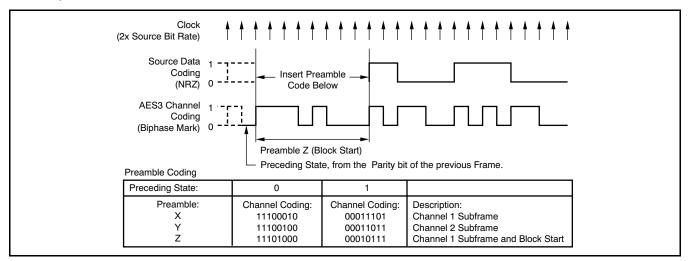

The binary non-return to zero (NRZ) formatted audio and status source data for bits 4 through 31 of each subframe are encoded utilizing a Biphase Mark format for transmission. This format allows for clock recovery at the receiver end, as well as making the interface insensitive to the polarity of the balanced cable connections. The preambles at the start of each subframe are encoded to intentionally violate the Biphase Mark formatting, making their detection by the receiver reliable, as well as avoiding the possibility of audio and status data imitating the preambles. Figure 64 shows the Biphase Mark and preamble encoding.

Although the AES3 standard originally defined transmission for sampling rates up to 48kHz, the interface is capable of handling higher sampling rates, given that attention is paid to cable length and impedance matching. Equalization at the receiver may also be required, depending on the cable and matching factors. It is also possible to transmit and decode more than two channels of audio data utilizing the AES3 or related consumer interfaces. Special encoding and/or compression algorithms are utilized to support multiple channels, including the Dolby® AC-3, DTS, MPEG-1/2, and other data reduced audio formats.

Figure 64. Biphase Mark Encoding

#### DIGITAL INTERFACE TRANSMITTER (DIT) OPERATION

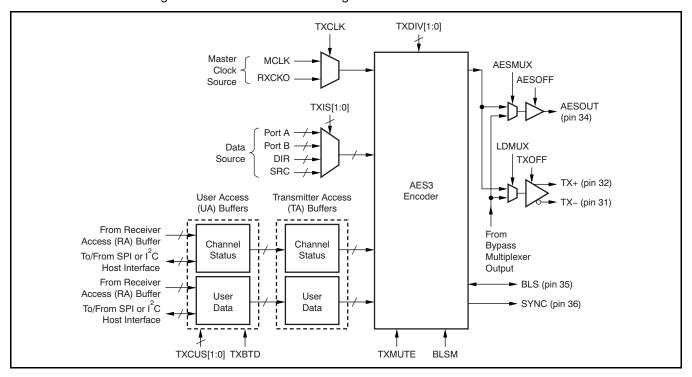

The DIT encodes a given two-channel or data-reduced audio input stream into an AES3-encoded output stream. In addition to the encoding function, the DIT includes differential line driver and CMOS buffered output functions. The line driver is suitable for driving balanced or unbalanced line interfaces, while the CMOS buffered output is designed to drive external logic or line drivers, as well as optical transmitter modules. Figure 65 illustrates the functional block diagram for the DIT.

The input of the DIT receives the audio data for Channels 1 and 2 from one of four possible sources: Port A, Port B, the DIR, or the SRC. By default, Port A is selected as the source. The DIT also requires a master clock source, which may be provided by either the MCLK input (pin 25) or RXCKO (the DIR recovered master clock output). A master clock divider is utilized to select the frame rate for the AES3-encoded output data. The TXDIV[1:0] bits in control register 0x07 are utilized to select divide by 128, 256, 384, or 512 operation.

Channel status and user data for Channels 1 and 2 are input to the AES3 encoder via the corresponding Transmitter Access (TA) data buffers. The TA data buffers are in turn loaded from the User Access (UA) buffers, which are programmed via the SPI or I<sup>2</sup>C host interface, or loaded from the DIR Receiver Access (RA) data buffers. The source of the channel status and user data is selected utilizing the TXCUS[1:0] bits in control register 0x09. When the DIR is selected as the input source, the channel status and user data output from the DIT is delayed by one block in relation to the audio data.

The validity (V) bit may be programmed using one of two sources. The VALSEL bit in control register 0x09 is utilized to select the validity data source for the DIT block. The default source is the VALID bit in control register 0x07, which is written via the SPI or I<sup>2</sup>C host interface. The validity bit may also be transferred from the AES3 decoder output of the DIR, where the V bit for the DIT subframes tracks the decoded DIR value frame by frame.

The parity (P) bit will always be generated by the AES3 encoder internal parity generator logic, such that bits 4 through 31 of the AES3-encoded subframe are even parity.

Submit Documentation Feedback

Copyright © 2006-2007, Texas Instruments Incorporated

The AES3 encoder output is connected to the output line driver and CMOS buffer source multiplexers. As shown in Figure 65, the source multiplexers allow the line driver or buffer to be driven by the AES3-encoded data from the DIT, or by the bypass multiplexer, which is associated with the outputs of the four differential input line receivers preceding the DIR core. The bypass multiplexer allows for one of the four line receiver outputs to be routed to the line driver or buffer output, thereby providing a bypass mode of operation. Both the line driver and CMOS output buffer include output disables, set by the TXOFF and AESOFF bits in control register 0x08. When the outputs are disabled, they are forced to a low logic state.

The AES3 encoder includes an output mute function that sets all bits for both the Channel 1 and 2 audio and auxiliary data to zero. The preamble, V, U, and C bits are unaffected, while the P bit is recalculated. The mute function is controlled using the TXMUTE bit in control register 0x08.

Figure 65. Digital Interface Transmitter (DIT) Functional Block Diagram

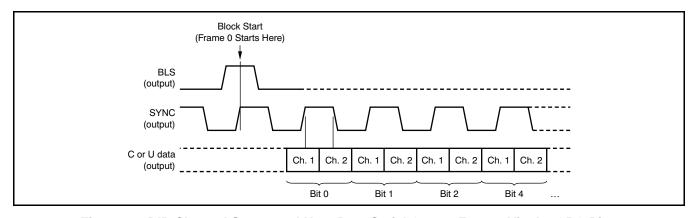

The AES3 encoder includes a block start input/output pin, BLS (pin 35). The BLS pin may be programmed as an input or output. The input/output state of the BLS pin is programmed using the BLSM bit in control register 0x07. By default, the BLS pin is configured as an input.

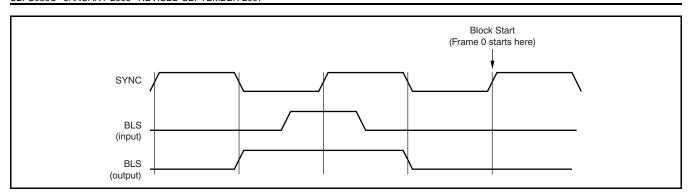

As an input, the BLS pin may be utilized to force a block start condition, whereby the start of a new block of channel status and user data is initiated by generating a Z preamble for the next frame of data. The BLS input must be synchronized with the DIT internal SYNC clock. This clock is output on SYNC (pin 36). The SYNC clock rising edge is aligned with the start of each frame for the AES3-encoded data output by the DIT. Figure 66 illustrates the format required for an external block start signal, as well as indicating the format when the BLS pin is configured as an output. When the BLS pin is an output, the DIT generates the block start signal based upon the internal SYNC clock.

For details regarding DIT control and status registers, as well as channel status and user data buffers, refer to the Control Registers and Channel Status and User Data Buffer Maps sections.

Figure 66. DIT Block Start Timing

# **DIGITAL INTERFACE RECEIVER (DIR) OPERATION**

The DIR performs AES3 decoding and clock recovery and provides the differential line receiver functions. The lock range of the DIR includes frame/sampling rates from 20kHz to 216kHz. Figure 67 shows the functional block diagram for the DIR.

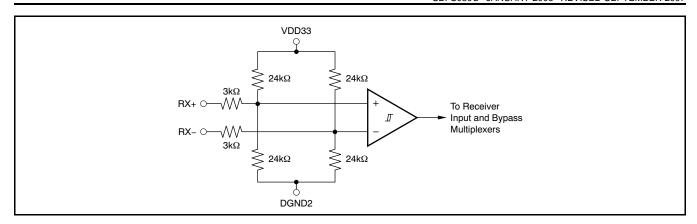

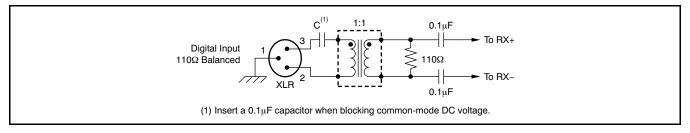

Four differential line receivers are utilized for signal conditioning the encoded input data streams. The receivers can be externally configured for either balanced or unbalanced cable interfaces, as well as interfacing with CMOS logic level inputs from optical receivers or external logic circuitry. See Figure 68 for a simplified schematic for the line receiver. External connections are discussed in the Receiver Input Interfacing section.

Figure 67. Digital Interface Receiver (DIR) Functional Block Diagram

Figure 68. Differential Line Receiver Circuit

The outputs of the four line receivers are connected to two 1-of-4 data selectors: the receiver input multiplexer and the bypass multiplexer. The input multiplexer selects one of the four line receiver outputs as the source for the AES3-encoded data stream to be processed by the DIR core. The bypass multiplexer is utilized to route a line receiver output to either the DIT line driver or CMOS buffered outputs, thereby bypassing all other internal circuitry. The bypass function is useful for simple signal distribution and routing applications.

The DIR requires a reference clock, supplied by an external source applied at either the RXCKI (pin 13) or MCLK (pin 25) clock inputs. PLL1 multiplies the reference clock to a higher rate, which is utilized as the oversampling clock for the AES3 decoder. The decoder samples the AES3-encoded input stream in order to extract all of the audio and status data. The decoded data stream is sent on to a de-multiplexer, where audio and status data are separated for further processing and buffering. The pulse generator circuitry samples the encoded input data stream and generates a clock that is 16 times the frame/sampling rate (or f<sub>S</sub>). The 16f<sub>S</sub> clock is then processed by PLL2, which further multiplies the clock rate and provides low-pass filtering for jitter attenuation. The available PLL2 output clock rates include 512f<sub>S</sub>, 256f<sub>S</sub>, and 128f<sub>S</sub>. The maximum available PLL2 output clock rate for a given input sampling rate is estimated by internal logic and made available for readback via status register 0x13.

The output of PLL2 may be divided by a factor of two, four, or eight, or simply passed through to the recovered master clock output, RXCKO (pin 12). The RXCKO clock is also be routed internally to other function blocks, where it may be further divided to create left/right word and bit clocks. The RXCKO output may be disabled and forced to a high-impedance state by means of a control register bit, allowing other tri-state buffered clocks to be tied to the same external circuit node, if needed. By default, the RXCKO output (pin 12) is disabled and forced to a high-impedance state.

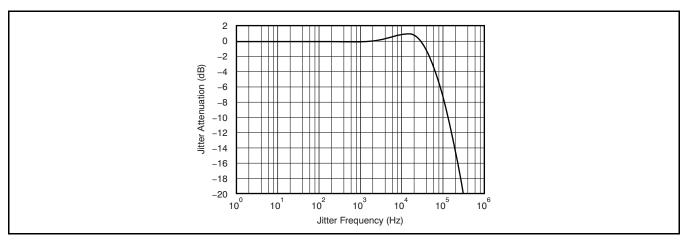

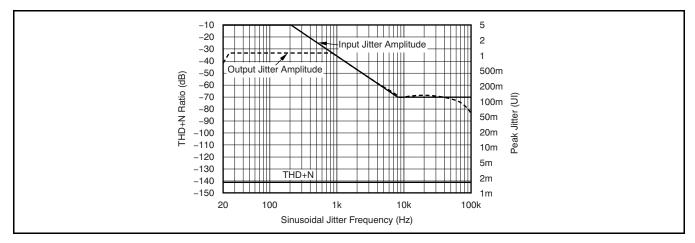

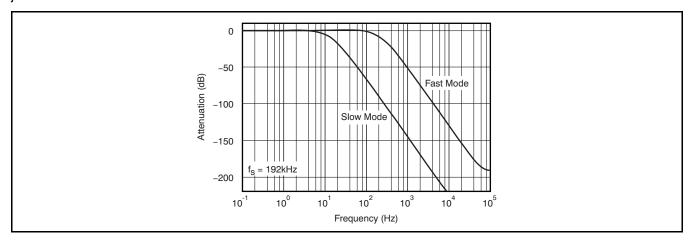

Figure 69 illustrates the frequency response of PLL2. Jitter attenuation starts at approximately 50kHz. Peaking is nominally 1dB, which is within the 2dB maximum allowed by the AES3 standard. The receiver jitter tolerance plot for the DIR is illustrated in Figure 70, along with the required AES3 jitter tolerance template. The DIR jitter tolerance satisfies the AES3 requirements, as well as the requirements set forth by the IEC60958-3 specification. Figure 70 was captured using a full-scale 24-bit, two-channel, AES3-encoded input stream with a 48kHz frame rate.

The decoded audio data, along with the internally-generated sync clocks, may be routed to other function blocks, including Port A, Port B, the SRC, and/or the DIT. The decoded channel status and user data is buffered in the corresponding Receiver Access (RA) data buffers, then transferred to the corresponding User Access (UA) data buffers, where it may be read back through either the SPI or I<sup>2</sup>C serial host interface. The contents of the RA buffers may also be transferred to the DIT UA data buffers; see Figure 65. The channel status and user data bits may also be output serially through the general-purpose output pins, GPO[4:1]. Figure 71 illustrates the output format for the GPO pins when used for this purpose, along with the DIR block start (BLS) and frame synchronization (SYNC) clocks. The rising edges of the DIR SYNC clock output are aligned with the start of each frame for the received AES3 data.

The DIR includes a dedicated, active low AES3 decoder and PLL2 lock output, named  $\overline{\text{LOCK}}$  (pin 11). The lock output is active only when both the AES3 decoder and PLL2 indicate a lock condition. Additional DIR status flags may be output at the general-purpose output (GPO) pins, or accessed through the status registers via the SPI or  $I^2\text{C}$  host interface. Refer to the General-Purpose Digital Outputs and Control Registers sections for additional information regarding the DIR status functions.

Figure 69. DIR Jitter Attenuation Characteristics

Figure 70. DIR Jitter Tolerance Plot

Figure 71. DIR Channel Status and User Data Serial Output Format Via the GPO Pins

# **ASYNCHRONOUS SAMPLE RATE CONVERTER (SRC) OPERATION**

The asynchronous SRC provides conversion from an arbitrary input sampling rate to a desired output sampling rate. The input and output sampling rates may be equal or different, within the bounds of a 1:16 to 16:1

32