**TPL0401B** SLIS144B - SEPTEMBER 2011 - REVISED FEBRUARY 2017

**TPL0401A**

# TPL0401x-10 128-TAPS Single-Channel Digital Potentiometer With I<sup>2</sup>C Interface

#### **Features**

- Single-Channel, 128-Position Resolution

- 10-kΩ End-to-End Resistance Options

- Low Temperature Coefficient: 22 ppm/°C

- I<sup>2</sup>C Serial Interface

- 2.7-V to 5.5-V Single-Supply Operation

- ±20% Resistance Tolerance

- A and B Versions Have Different I<sup>2</sup>C Addresses

- L Terminal is Internal and Connected to GND

- Operating Temperature: -40°C to +125°C

- Available in Industry Standard SC70 Packages

- ESD Performance Tested per JESD 22

- 2000-V Human-Body Model (A114-B, Class II)

## Applications

- Mechanical Potentiometer Replacement

- Adjustable Power Supplies

- Adjustable Gain Amplifiers and Offset Trimming

- Precision Calibration of Setpoint Thresholds

- Sensor Trimming and Calibration

## 3 Description

The TPL0401x-10 device is a single-channel, lineartaper digital potentiometer with 128 wiper positions. The TPL0401x-10 has the low terminal internal and connected to GND. The position of the wiper can be adjusted using an I<sup>2</sup>C interface. The TPL0401x-10 is available in a 6-pin SC70 package with a specified temperature range of -40°C to +125°C. The part has a 10-k $\Omega$  end-to-end resistance and can operate with a supply voltage range of 2.7 V to 5.5 V. This kind of product is widely used in setting the voltage reference for low power DDR3 memory.

The TPL0401x-10 has the low terminal internal and connected to GND.

#### Device Information(1)

| PART NUMBER                | PACKAGE  | BODY SIZE (NOM)   |

|----------------------------|----------|-------------------|

| TPL0401A-10<br>TPL0401B-10 | SC70 (6) | 2.00 mm × 1.25 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

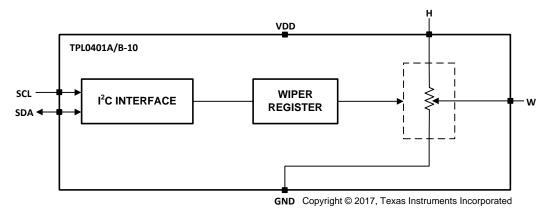

## **Simplified Schematic**

## **Table of Contents**

| 1 | Features 1                             | 10 | Application and Implementation                     | 2 <sup>.</sup> |

|---|----------------------------------------|----|----------------------------------------------------|----------------|

| 2 | Applications 1                         |    | 10.1 Application Information                       |                |

| 3 | Description 1                          |    | 10.2 Typical Application                           |                |

| 4 | Revision History2                      | 11 |                                                    |                |

| 5 | Device Comparison Table 3              |    | 11.1 Power Sequence                                |                |

| 6 | Pin Configuration and Functions 3      |    | 11.2 Power-On Reset Requirements                   |                |

| 7 | Specifications4                        |    | 11.3 I <sup>2</sup> C Communication After Power Up |                |

|   | 7.1 Absolute Maximum Ratings 4         |    | 11.4 Wiper Position While Unpowered and After Po   |                |

|   | 7.2 ESD Ratings 4                      | 12 | Layout                                             |                |

|   | 7.3 Recommended Operating Conditions 4 |    | 12.1 Layout Guidelines                             |                |

|   | 7.4 Thermal Information 4              |    | 12.2 Layout Example                                |                |

|   | 7.5 Electrical Characteristics         | 13 | Device and Documentation Support                   |                |

|   | 7.6 Timing Requirements                |    | 13.1 Documentation Support                         |                |

|   | 7.7 Typical Characteristics            |    | 13.2 Related Links                                 |                |

| 8 | Parameter Measurement Information 9    |    | 13.3 Receiving Notification of Documentation Upda  |                |

| 9 | Detailed Description 11                |    | 13.4 Community Resources                           |                |

|   | 9.1 Overview 11                        |    | 13.5 Trademarks                                    |                |

|   | 9.2 Functional Block Diagram 11        |    | 13.6 Electrostatic Discharge Caution               |                |

|   | 9.3 Feature Description                |    | <b>G</b>                                           |                |

|   | 9.4 Device Functional Modes11          |    | 13.7 Glossary                                      | 20             |

|   | 9.5 Programming                        | 14 | Mechanical, Packaging, and Orderable Information   | 20             |

|   | 9.6 Register Maps                      |    | IIIOIIIauoii                                       | 20             |

|   |                                        |    |                                                    |                |

|   |                                        |    |                                                    |                |

## 4 Revision History

| Changes from Revision | A (March 2012 | 2) to Revision E |

|-----------------------|---------------|------------------|

|-----------------------|---------------|------------------|

Page

| • | Added Device Information table, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | . 1 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed this data sheet to the new SDA format                                                                                                                                                                                                                                                                 | 1   |

| • | Removed the obsolete TPL0401C device from the data sheet                                                                                                                                                                                                                                                      | . 1 |

| • | Removed TPL0401C references                                                                                                                                                                                                                                                                                   | . 1 |

| • | Changed T <sub>A</sub> max value to 125°C from 128°C                                                                                                                                                                                                                                                          | 4   |

| • | Deleted I <sub>LKG</sub>                                                                                                                                                                                                                                                                                      | 5   |

| • | Changed R <sub>H</sub> typical and max values                                                                                                                                                                                                                                                                 | 5   |

| • | Changed I <sub>DD(STBY)</sub> measurement point from 85°C to 105°C                                                                                                                                                                                                                                            | 5   |

| • | I <sub>IN-DIG</sub> min and max values increased                                                                                                                                                                                                                                                              |     |

| • | Added Rheostat mode parameters                                                                                                                                                                                                                                                                                | 5   |

| • | Corrected typo to t <sub>OCF</sub> from t <sub>ICF</sub>                                                                                                                                                                                                                                                      | 6   |

| • | Corrected typo to t <sub>VD(DATA)</sub> from t <sub>VD(ACK)</sub>                                                                                                                                                                                                                                             | 6   |

| • | Updated Typical Characteristics graphs                                                                                                                                                                                                                                                                        | 7   |

| • | Updated Resistance Values table                                                                                                                                                                                                                                                                               | 12  |

| • | Added power supply recommendations                                                                                                                                                                                                                                                                            |     |

## Changes from Original (September 2011) to Revision A

Page ..... 1

Added TPL0401C device to the Datasheet

Added TPL0401C Package

Added TPL0401C Functional Block Diagram

2 Submit Documentation Feedback

Copyright © 2011–2017, Texas Instruments Incorporated

## 5 Device Comparison Table

| ORDERABLE PART NUMBER | END-TO-END RESISTANCE | I <sup>2</sup> C ADDRESS |

|-----------------------|-----------------------|--------------------------|

| TPL0401A-10DCKR       | 10 kΩ                 | 0101110                  |

| TPL0401B-10DCKR       | 10 kΩ                 | 0111110                  |

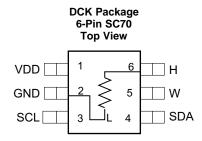

## 6 Pin Configuration and Functions

## **Pin Functions**

| PIN |      | TYPE  | DESCRIPTION             |

|-----|------|-------|-------------------------|

| NO. | NAME | ITPE  | DESCRIPTION             |

| 1   | VDD  | Power | Positive supply voltage |

| 2   | GND  | _     | Ground                  |

| 3   | SCL  | 1     | I <sup>2</sup> C Clock  |

| 4   | SDA  | I/O   | I <sup>2</sup> C Data   |

| 5   | W    | I/O   | Wiper terminal          |

| 6   | Н    | I/O   | High terminal           |

| _   | L    | I/O   | Low terminal            |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                       |                                       | MIN  | MAX            | UNIT |

|-----------------------|---------------------------------------|------|----------------|------|

| $V_{DD}$              | Supply voltage V <sub>DD</sub> to GND | -0.3 | 7              | ٧    |

| $I_H$ , $I_L$ , $I_W$ | Continuous current                    |      | ±5             | mA   |

| V                     | Digital input pins (SDA, SCL)         | -0.3 | $V_{DD} + 0.3$ | \/   |

| VI                    | Potentiometer pins (H, W)             | -0.3 | $V_{DD} + 0.3$ | V    |

| T <sub>J(MAX)</sub>   | Maximum junction temperature          |      | 130            | °C   |

| T <sub>stg</sub>      | Storage temperature                   | -65  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                          |                                                                     | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Floatroatatio dia abarra | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2500 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                           |                                 | MIN                 | MAX                 | UNIT |

|-------------------------------------------|---------------------------------|---------------------|---------------------|------|

| $V_{DD}$                                  | Supply voltage                  | 2.7                 | 5.5                 | V    |

| V <sub>W</sub> ,V <sub>H</sub> , SDA, SCL | Terminal voltage                | 0                   | $V_{DD}$            | V    |

| V <sub>IH</sub>                           | Voltage input high ( SCL, SDA ) | $0.7 \times V_{DD}$ | $V_{DD}$            | V    |

| $V_{IL}$                                  | Voltage input low ( SCL, SDA )  | 0                   | $0.3 \times V_{DD}$ | V    |

| $I_{W}$                                   | Wiper current                   | -2                  | 2                   | mA   |

| T <sub>A</sub>                            | Ambient operating temperature   | -40                 | 125                 | °C   |

#### 7.4 Thermal Information

|                      |                                              | TPL0401x-10 |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DCK (SC70)  | UNIT |

|                      |                                              | 6 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 234         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 110.5       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 79          | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 7.2         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 77          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

#### 7.5 Electrical Characteristics

Typical values are specified at 25°C and  $V_{DD} = 3.3 \text{ V}$  (unless otherwise noted)

|                            | PARAMETER                                                             | TEST CONDITIONS                                                   | MIN                      | TYP   | MAX                      | UNIT   |

|----------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|-------|--------------------------|--------|

| R <sub>TOTAL</sub>         | End-to-end resistance                                                 |                                                                   | 8                        | 10    | 12                       | kΩ     |

| R <sub>H</sub>             | Terminal resistance                                                   |                                                                   |                          | 100   | 200                      | Ω      |

| R <sub>W</sub>             | Wiper resistance                                                      |                                                                   |                          | 35    | 100                      | Ω      |

| Сн                         | Terminal capacitance                                                  |                                                                   |                          | 10    |                          | pF     |

| C <sub>W</sub>             | Wiper capacitance                                                     |                                                                   |                          | 11    |                          | pF     |

| TC <sub>R</sub>            | Resistance temperature coefficient                                    |                                                                   |                          | 22    |                          | ppm/°C |

| I <sub>DD(STBY)</sub>      | V <sub>DD</sub> standby current                                       | -40°C to +105°C                                                   |                          |       | 0.5                      | μΑ     |

| I <sub>IN-DIG</sub>        | Digital pins leakage current (SCL, SDA Inputs)                        | -40°C to +125°C                                                   | -2.5                     |       | 1.5<br>2.5               | μA     |

| SERIAL INTE                | RFACE SPECS (SDA, SCL)                                                |                                                                   |                          |       |                          |        |

| V <sub>IH</sub>            | Input high voltage                                                    |                                                                   | 0.7 ×<br>V <sub>DD</sub> |       | $V_{DD}$                 | V      |

| V <sub>IL</sub>            | Input low voltage                                                     |                                                                   | 0                        |       | 0.3 ×<br>V <sub>DD</sub> | V      |

| V <sub>OL</sub>            | Output low voltage                                                    | SDA Pin, I <sub>OL</sub> = 4 mA                                   |                          |       | 0.4                      | V      |

| C <sub>IN</sub>            | Pin capacitance                                                       | SCL, SDA Inputs                                                   |                          | 7     |                          | pF     |

| VOLTAGE DIV                | /IDER MODE (V <sub>H</sub> = V <sub>DD</sub> , V <sub>W</sub> = Not L | oaded)                                                            |                          |       |                          |        |

| INL <sup>(1)(2)</sup>      | Integral non-linearity                                                |                                                                   | -0.5                     |       | 0.5                      | LSB    |

| DNL <sup>(3)(2)</sup>      | Differential non-linearity                                            |                                                                   | -0.25                    |       | 0.25                     | LSB    |

| ZS <sub>ERROR</sub> (4)(5) | Zero-scale error                                                      |                                                                   | 0                        | 0.75  | 1.5                      | LSB    |

| FS <sub>ERROR</sub> (6)(5) | Full-scale error                                                      |                                                                   | -1.5                     | -0.75 | 0                        | LSB    |

| T <sub>CV</sub>            | Ratiometric temperature coefficient                                   | Wiper set at mid-scale                                            |                          | 4     |                          | ppm/°C |

| BW                         | Bandwidth                                                             | Wiper set at mid-scale,<br>C <sub>LOAD</sub> = 10 pF              |                          | 2862  |                          | kHz    |

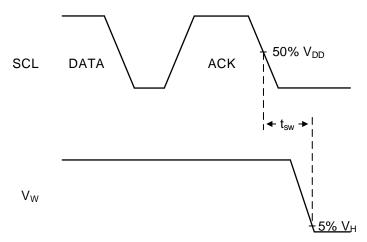

| T <sub>SW</sub>            | Wiper settling time                                                   | See Figure 10                                                     |                          | 0.152 |                          | μs     |

| THD+N                      | Total harmonic distortion                                             | V <sub>H</sub> = 1 V <sub>RMS</sub> at 1 kHz,<br>measurement at W |                          | 0.03  |                          | %      |

| RHEOSTAT N                 | IODE (V <sub>H</sub> = V <sub>DD</sub> , V <sub>W</sub> = Not Loaded) |                                                                   |                          |       |                          |        |

| RINL <sup>(7)(8)</sup>     | Rheostat mode integral non-<br>linearity                              |                                                                   | -1                       |       | 1                        | LSB    |

| RDNL <sup>(9)(8)</sup>     | Rheostat mode differential non-<br>linearity                          |                                                                   | 0.5                      |       | 0.5                      | LSB    |

| ROFFSET (10)(1             | Rheostat-mode zero-scale error                                        |                                                                   | 0                        | 0.75  | 2                        | LSB    |

<sup>(1)</sup> INL = ((V<sub>MEAS[code x]</sub> - V<sub>MEAS[code 0]</sub>) / LSB) - [code x] (2) LSB = (V<sub>MEAS[code 127]</sub> - V<sub>MEAS[code 0]</sub>) / 127 (3) DNL = ((V<sub>MEAS[code x]</sub> - V<sub>MEAS[code x-1]</sub>) / LSB) - 1 (4) ZS<sub>ERROR</sub> = V<sub>MEAS[code 0]</sub> / IDEAL\_LSB (5) IDEAL\_LSB = V<sub>H</sub> / 128 (6) ES-2000 = [(V<sub>MEAS[code x]</sub> - V<sub>MEAS[code x]</sub>) / IDEAL\_LSB] + 1

<sup>(5)</sup> IDEAL\_LSB = V<sub>H</sub> / 128

(6) FSERROR = [(VMEAS[code 127] - V<sub>H</sub>) / IDEAL\_LSB] + 1

(7) RINL = ((RMEAS[code x] - RMEAS[code 0]) / RLSB) - [code x]

(8) RLSB = (RMEAS[code 127] - RMEAS[code 0]) / 127

(9) RDNL = ((RMEAS[code x] - RMEAS[code x-1]) / RLSB) - 1

(10) ROFFSET = RMEAS[code 0] / IDEAL\_RLSB

(11) IDEAL\_RLSB = RTOT / 128

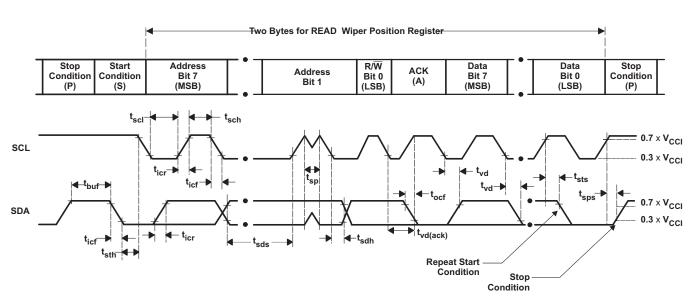

## 7.6 Timing Requirements

|                       | ming Kequirements                                                          | MIN                        | MAX  | UNIT |

|-----------------------|----------------------------------------------------------------------------|----------------------------|------|------|

| STANDAR               | D MODE                                                                     | <u> </u>                   | ,    |      |

| f <sub>SCL</sub>      | I <sup>2</sup> C clock frequency                                           | 0                          | 100  | kHz  |

| t <sub>SCH</sub>      | I <sup>2</sup> C clock high time                                           | 4                          |      | μs   |

| t <sub>SCL</sub>      | I <sup>2</sup> C clock low time                                            | 4.7                        |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                                                | 0                          | 50   | ns   |

| t <sub>SDS</sub>      | I <sup>2</sup> C serial data setup time                                    | 250                        |      | ns   |

| t <sub>SDH</sub>      | I <sup>2</sup> C serial data hold time                                     | 0                          |      | ns   |

| t <sub>ICR</sub>      | I <sup>2</sup> C input rise time                                           |                            | 1000 | ns   |

| t <sub>ICF</sub>      | I <sup>2</sup> C input fall time                                           |                            | 300  | ns   |

| t <sub>OCF</sub>      | I <sup>2</sup> C output fall time, 10 pF to 400 pF bus                     |                            | 300  | ns   |

| t <sub>BUF</sub>      | I <sup>2</sup> C bus free time between stop and start                      | 4.7                        |      | μs   |

| t <sub>STS</sub>      | I <sup>2</sup> C start or repeater start condition setup time              | 4.7                        |      | μs   |

| t <sub>STH</sub>      | I <sup>2</sup> C start or repeater start condition hold time               | 4                          |      | μs   |

| t <sub>SPS</sub>      | I <sup>2</sup> C stop condition setup time                                 | 4                          |      | μs   |

| t <sub>VD(DATA)</sub> | Valid data time, SCL low to SDA output valid                               |                            | 1    | μs   |

| t <sub>VD(ACK)</sub>  | Valid data time of ACK condition, ACK signal from SCL low to SDA (out) low |                            | 1    | μs   |

| FAST MOD              | DE                                                                         |                            |      |      |

| f <sub>SCL</sub>      | I <sup>2</sup> C clock frequency                                           | 0                          | 400  | kHz  |

| t <sub>SCH</sub>      | I <sup>2</sup> C clock high time                                           | 0.6                        |      | μs   |

| t <sub>SCL</sub>      | I <sup>2</sup> C clock low time                                            | 1.3                        |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                                                | 0                          | 50   | ns   |

| t <sub>SDS</sub>      | I <sup>2</sup> C serial data setup time                                    | 100                        |      | ns   |

| t <sub>SDH</sub>      | I <sup>2</sup> C serial data hold time                                     | 0                          |      | ns   |

| t <sub>ICR</sub>      | I <sup>2</sup> C input rise time                                           | 20                         | 300  | ns   |

| t <sub>ICF</sub>      | I <sup>2</sup> C input fall time                                           | $20 \times (V_{DD} / 5.5)$ | 300  | ns   |

| t <sub>OCF</sub>      | I <sup>2</sup> C output fall time, 10 pF to 400 pF bus                     | $(V_{DD} / 5.5) \times 20$ | 300  | ns   |

| t <sub>BUF</sub>      | I <sup>2</sup> C bus free time between stop and start                      | 1.3                        |      | μs   |

| t <sub>STS</sub>      | I <sup>2</sup> C start or repeater start condition setup time              | 1.3                        |      | μs   |

| t <sub>STH</sub>      | I <sup>2</sup> C start or repeater start condition hold time               | 0.6                        |      | μs   |

| t <sub>SPS</sub>      | I <sup>2</sup> C stop condition setup time                                 | 0.6                        |      | μs   |

| t <sub>VD(DATA)</sub> | Valid data time, SCL low to SDA output valid                               |                            | 1    | μs   |

| t <sub>VD(ACK)</sub>  | Valid data time of ACK condition, ACK signal from SCL low to SDA (out) low |                            | 1    | μs   |

Submit Documentation Feedback

Copyright © 2011–2017, Texas Instruments Incorporated

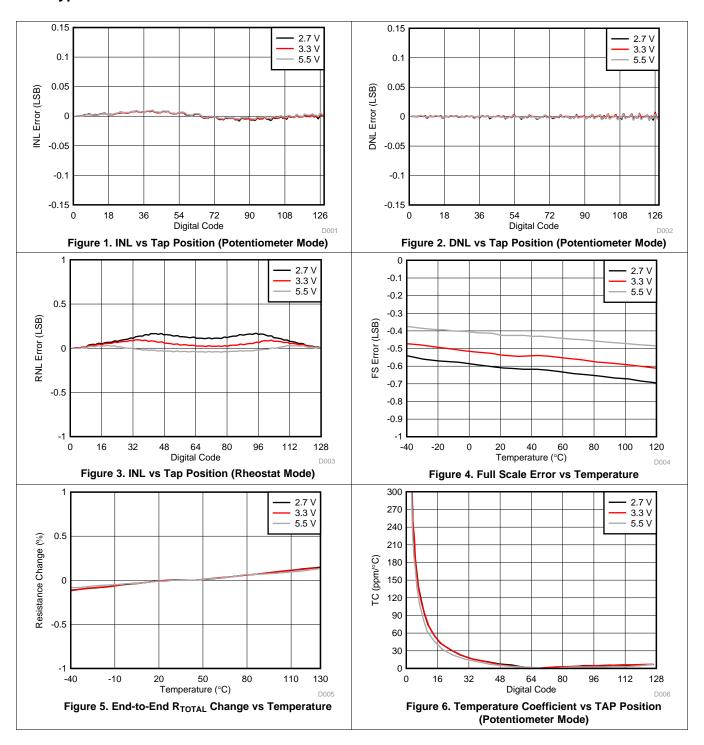

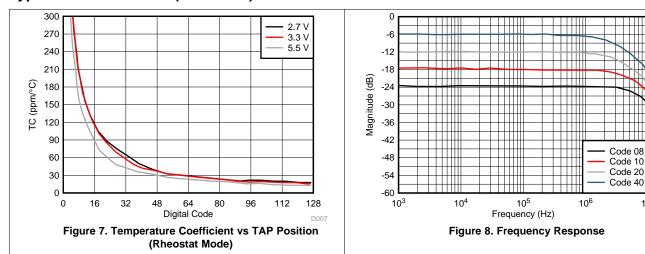

## 7.7 Typical Characteristics

10<sup>7</sup>

## **Typical Characteristics (continued)**

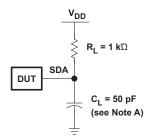

## 8 Parameter Measurement Information

**SDA LOAD CONFIGURATION**

**VOLTAGE WAVEFORMS**

| BYTE | DESCRIPTION         |

|------|---------------------|

| 1    | I C address         |

| 2    | Wiper Position Data |

- A.  $C_L$  includes probe and jig capacitance. tocf is measured with  $C_L$  of 10 pF or 400 pF.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50 \Omega$ ,  $t_r/t_f \leq$  30 ns.

- C. All parameters and waveforms are not applicable to all devices.

Figure 9. I<sup>2</sup>C Interface Load Circuit and Voltage Waveforms

## **Parameter Measurement Information (continued)**

- A. Code change is from 0x40 to 0x00

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50 \Omega$ ,  $t_r/t_f \leq$  30 ns.

Figure 10. Switch Time Waveform (t<sub>SW</sub>)

Submit Documentation Feedback

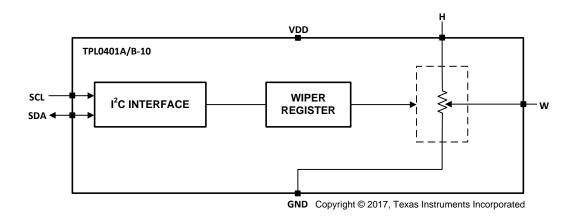

## 9 Detailed Description

#### 9.1 Overview

The TPL0401x-10 has a single linear-taper digital potentiometer with 128 wiper positions and an end-to-end resistance of 10 k $\Omega$ . The potentiometer can be used as a three-terminal potentiometer. The main operation of TPL0401x-10 is in voltage divider mode.

The low (L) terminal of the TPL0401x-10 is tied directly to GND. The high (H) and low (GND) terminals of TPL0401-10 are equivalent to the fixed terminals of a mechanical potentiometer. The H terminal must have a higher voltage than the low terminal (GND). The position of the wiper (W) terminal is controlled by the value in the Wiper Resistance (WR) 8-bit register. When the WR register contains all zeroes (zero-scale), the wiper terminal is closest to its L terminal. As the value of the WR register increases from all zeroes to all ones (full-scale), the wiper moves from the position closest to the GND terminal to the position closest to the H terminal. At the same time, the resistance between W and GND increases, whereas the resistance between W and H decreases.

#### 9.2 Functional Block Diagram

## 9.3 Feature Description

The TPL0401x-10 device is a single-channel, linear taper digital potentiometer with 128 wiper positions. Default power up state for the TPL0401x-10 is mid code (0x40). The TPL0401x-10 has the low terminal connected to GND internally. The position of the wiper can be adjusted using an  $I^2$ C interface. The TPL0401x-10 is available in a 6-pin SOT package with a specified temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. The part has a 10-k $\Omega$  end-to-end resistance and can operate with a supply voltage range of 2.7 V to 5.5 V. This kind of product is widely used in setting the voltage reference for low power DDR3 memory. The TPL0401x-10 has the low terminal internal and connected to GND.

#### 9.4 Device Functional Modes

#### 9.4.1 Voltage Divider Mode

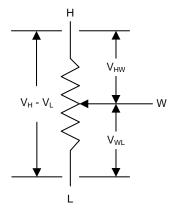

The digital potentiometer generates a voltage divider when all three terminals are used. The voltage divider at wiper-to-H and wiper-to-GND is proportional to the input voltage at H to L (see Figure 11).

#### **Device Functional Modes (continued)**

Figure 11. Equivalent Circuit for Voltage Divider Mode

For example, connecting terminal H to 5 V, the output voltage at terminal W can range from 0 V to 5 V. Equation 1 is the general equation defining the output voltage at terminal W for any valid input voltage applied to terminal H and terminal L (GND).

$$V_{W} = V_{WL} = (V_{H} - V_{L}) \times \frac{D}{128}$$

(1)

The voltage difference between terminal H and terminal W can also be calculated in Equation 2.

$$V_{HW} = (V_H - V_L) \times \left(1 - \left(\frac{D}{128}\right)\right)$$

where

D is the decimal value of the wiper code

(2)

Table 1 shows the ideal values for DPOT with end-to end resistance of 10 k $\Omega$ . The absolute values of resistance can vary significantly but the Ratio ( $R_{WL}/R_{TOT}$ ) is extremely accurate.

The linearity values are *relative* linearity values (that is, linearity after zero-scale and full-scale offset errors are removed). Consider this when expecting a certain absolute accuracy because some error is introduced when the device gets close in magnitude to the offset errors.

Note that the MSB is always discarded during a write to the wiper position register. For example, if 0x80 is written to the wiper position register, a read returns 0x00. Another similar example is if 0xFF is written, then 0x7F is read.

**Table 1. Resistance Values Table**

| STEP | HEX  | R <sub>WL</sub> (KΩ) | R <sub>HW</sub> (KΩ) | R <sub>WL</sub> /R <sub>TOT</sub> |

|------|------|----------------------|----------------------|-----------------------------------|

| 0    | 0x00 | 0.00                 | 10.00                | 0.0%                              |

| 1    | 0x01 | 0.08                 | 9.92                 | 0.8%                              |

| 2    | 0x02 | 0.16                 | 9.84                 | 1.6%                              |

| 3    | 0x03 | 0.23                 | 9.77                 | 2.3%                              |

| 4    | 0x04 | 0.31                 | 9.69                 | 3.1%                              |

| 5    | 0x05 | 0.39                 | 9.61                 | 3.9%                              |

| 6    | 0x06 | 0.47                 | 9.53                 | 4.7%                              |

| 7    | 0x07 | 0.55                 | 9.45                 | 5.5%                              |

| 8    | 0x08 | 0.63                 | 9.38                 | 6.3%                              |

| 9    | 0x09 | 0.70                 | 9.30                 | 7.0%                              |

| 10   | 0x0A | 0.78                 | 9.22                 | 7.8%                              |

Submit Documentation Feedback

Copyright © 2011–2017, Texas Instruments Incorporated

**Table 1. Resistance Values Table (continued)**

| STEP | HEX  | R <sub>WL</sub> (KΩ) | R <sub>HW</sub> (KΩ) | R <sub>WL</sub> /R <sub>TOT</sub> |

|------|------|----------------------|----------------------|-----------------------------------|

| 11   | 0x0B | 0.86                 | 9.14                 | 8.6%                              |

| 12   | 0x0C | 0.94                 | 9.06                 | 9.4%                              |

| 13   | 0x0D | 1.02                 | 8.98                 | 10.2%                             |

| 14   | 0x0E | 1.09                 | 8.91                 | 10.9%                             |

| 15   | 0x0F | 1.17                 | 8.83                 | 11.7%                             |

| 16   | 0x10 | 1.25                 | 8.75                 | 12.5%                             |

| 17   | 0x11 | 1.33                 | 8.67                 | 13.3%                             |

| 18   | 0x12 | 1.41                 | 8.59                 | 14.1%                             |

| 19   | 0x13 | 1.48                 | 8.52                 | 14.8%                             |

| 20   | 0x14 | 1.56                 | 8.44                 | 15.6%                             |

| 21   | 0x15 | 1.64                 | 8.36                 | 16.4%                             |

| 22   | 0x16 | 1.72                 | 8.28                 | 17.2%                             |

| 23   | 0x17 | 1.80                 | 8.20                 | 18.0%                             |

| 24   | 0x18 | 1.88                 | 8.13                 | 18.8%                             |

| 25   | 0x19 | 1.95                 | 8.05                 | 19.5%                             |

| 26   | 0x1A | 2.03                 | 7.97                 | 20.3%                             |

| 27   | 0x1B | 2.11                 | 7.89                 | 21.1%                             |

| 28   | 0x1C | 2.19                 | 7.81                 | 21.9%                             |

| 29   | 0x1D | 2.27                 | 7.73                 | 22.7%                             |

| 30   | 0x1E | 2.34                 | 7.66                 | 23.4%                             |

| 31   | 0x1F | 2.42                 | 7.58                 | 24.2%                             |

| 32   | 0x20 | 2.50                 | 7.50                 | 25.0%                             |

| 33   | 0x21 | 2.58                 | 7.42                 | 25.8%                             |

| 34   | 0x22 | 2.66                 | 7.34                 | 26.6%                             |

| 35   | 0x23 | 2.73                 | 7.27                 | 27.3%                             |

| 36   | 0x24 | 2.81                 | 7.19                 | 28.1%                             |

| 37   | 0x25 | 2.89                 | 7.11                 | 28.9%                             |

| 38   | 0x26 | 2.97                 | 7.03                 | 29.7%                             |

| 39   | 0x27 | 3.05                 | 6.95                 | 30.5%                             |

| 40   | 0x28 | 3.13                 | 6.88                 | 31.3%                             |

| 41   | 0x29 | 3.20                 | 6.80                 | 32.0%                             |

| 42   | 0x2A | 3.28                 | 6.72                 | 32.8%                             |

| 43   | 0x2B | 3.36                 | 6.64                 | 33.6%                             |

| 44   | 0x2C | 3.44                 | 6.56                 | 34.4%                             |

| 45   | 0x2D | 3.52                 | 6.48                 | 35.2%                             |

| 46   | 0x2E | 3.59                 | 6.41                 | 35.9%                             |

| 47   | 0x2F | 3.67                 | 6.33                 | 36.7%                             |

| 48   | 0x30 | 3.75                 | 6.25                 | 37.5%                             |

| 49   | 0x31 | 3.83                 | 6.17                 | 38.3%                             |

| 50   | 0x32 | 3.91                 | 6.09                 | 39.1%                             |

| 51   | 0x33 | 3.98                 | 6.02                 | 39.8%                             |

| 52   | 0x34 | 4.06                 | 5.94                 | 40.6%                             |

| 53   | 0x35 | 4.14                 | 5.86                 | 41.4%                             |

| 54   | 0x36 | 4.22                 | 5.78                 | 42.2%                             |

| 55   | 0x37 | 4.30                 | 5.70                 | 43.0%                             |

| 56   | 0x38 | 4.38                 | 5.63                 | 43.8%                             |

| 57   | 0x39 | 4.45                 | 5.55                 | 44.5%                             |

Table 1. Resistance Values Table (continued)

| STEP             | HEX          | R <sub>WL</sub> (KΩ) | R <sub>HW</sub> (KΩ) | R <sub>WL</sub> /R <sub>TOT</sub> |

|------------------|--------------|----------------------|----------------------|-----------------------------------|

| 58               | 0x3A         | 4.53                 | 5.47                 | 45.3%                             |

| 59               | 0x3A<br>0x3B | 4.61                 | 5.39                 | 46.1%                             |

| 60               | 0x3C         | 4.69                 | 5.31                 | 46.9%                             |

|                  |              |                      |                      |                                   |

| 61               | 0x3D         | 4.77                 | 5.23                 | 47.7%                             |

| 62               | 0x3E         | 4.84                 | 5.16                 | 48.4%                             |

| 63               | 0x3F         | 4.92                 | 5.08                 | 49.2%                             |

| 64 (POR Default) | 0x40         | 5.00                 | 5.00                 | 50.0%                             |

| 65               | 0x41         | 5.08                 | 4.92                 | 50.8%                             |

| 66               | 0x42         | 5.16                 | 4.84                 | 51.6%                             |

| 67               | 0x43         | 5.23                 | 4.77                 | 52.3%                             |

| 68               | 0x44         | 5.31                 | 4.69                 | 53.1%                             |

| 69               | 0x45         | 5.39                 | 4.61                 | 53.9%                             |

| 70               | 0x46         | 5.47                 | 4.53                 | 54.7%                             |

| 71               | 0x47         | 5.55                 | 4.45                 | 55.5%                             |

| 72               | 0x48         | 5.63                 | 4.38                 | 56.3%                             |

| 73               | 0x49         | 5.70                 | 4.30                 | 57.0%                             |

| 74               | 0x4A         | 5.78                 | 4.22                 | 57.8%                             |

| 75               | 0x4B         | 5.86                 | 4.14                 | 58.6%                             |

| 76               | 0x4C         | 5.94                 | 4.06                 | 59.4%                             |

| 77               | 0x4D         | 6.02                 | 3.98                 | 60.2%                             |

| 78               | 0x4E         | 6.09                 | 3.91                 | 60.9%                             |

| 79               | 0x4F         | 6.17                 | 3.83                 | 61.7%                             |

| 80               | 0x50         | 6.25                 | 3.75                 | 62.5%                             |

| 81               | 0x51         | 6.33                 | 3.67                 | 63.3%                             |

| 82               | 0x52         | 6.41                 | 3.59                 | 64.1%                             |

| 83               | 0x53         | 6.48                 | 3.52                 | 64.8%                             |

| 84               | 0x54         | 6.56                 | 3.44                 | 65.6%                             |

| 85               | 0x55         | 6.64                 | 3.36                 | 66.4%                             |

| 86               | 0x56         | 6.72                 | 3.28                 | 67.2%                             |

| 87               | 0x57         | 6.80                 | 3.20                 | 68.0%                             |

| 88               | 0x58         | 6.88                 | 3.13                 | 68.8%                             |

| 89               | 0x59         | 6.95                 | 3.05                 | 69.5%                             |

| 90               | 0x5A         | 7.03                 | 2.97                 | 70.3%                             |

| 91               | 0x5B         | 7.11                 | 2.89                 | 71.1%                             |

| 92               | 0x5C         | 7.19                 | 2.81                 | 71.9%                             |

| 93               | 0x5D         | 7.27                 | 2.73                 | 72.7%                             |

| 94               | 0x5E         | 7.34                 | 2.66                 | 73.4%                             |

| 95               | 0x5F         | 7.42                 | 2.58                 | 74.2%                             |

| 96               | 0x60         | 7.50                 | 2.50                 | 75.0%                             |

| 97               | 0x61         | 7.58                 | 2.42                 | 75.8%                             |

| 98               | 0x62         | 7.66                 | 2.34                 | 76.6%                             |

| 99               | 0x63         | 7.73                 | 2.27                 | 77.3%                             |

| 100              | 0x64         | 7.81                 | 2.19                 | 78.1%                             |

| 101              | 0x65         | 7.89                 | 2.11                 | 78.9%                             |

| 102              | 0x66         | 7.97                 | 2.03                 | 79.7%                             |

| 103              | 0x67         | 8.05                 | 1.95                 | 80.5%                             |

| 104              |              | 8.13                 | 1.88                 | 81.3%                             |

| 104              | 0x68         | 0.13                 | 1.00                 | 01.3%                             |

Table 1. Resistance Values Table (continued)

| STEP | HEX  | R <sub>WL</sub> (KΩ) | R <sub>HW</sub> (KΩ) | R <sub>WL</sub> /R <sub>TOT</sub> |

|------|------|----------------------|----------------------|-----------------------------------|

| 105  | 0x69 | 8.20                 | 1.80                 | 82.0%                             |

| 106  | 0x6A | 8.28                 | 1.72                 | 82.8%                             |

| 107  | 0x6B | 8.36                 | 1.64                 | 83.6%                             |

| 108  | 0x6C | 8.44                 | 1.56                 | 84.4%                             |

| 109  | 0x6D | 8.52                 | 1.48                 | 85.2%                             |

| 110  | 0x6E | 8.59                 | 1.41                 | 85.9%                             |

| 111  | 0x6F | 8.67                 | 1.33                 | 86.7%                             |

| 112  | 0x70 | 8.75                 | 1.25                 | 87.5%                             |

| 113  | 0x71 | 8.83                 | 1.17                 | 88.3%                             |

| 114  | 0x72 | 8.91                 | 1.09                 | 89.1%                             |

| 115  | 0x73 | 8.98                 | 1.02                 | 89.8%                             |

| 116  | 0x74 | 9.06                 | 0.94                 | 90.6%                             |

| 117  | 0x75 | 9.14                 | 0.86                 | 91.4%                             |

| 118  | 0x76 | 9.22                 | 0.78                 | 92.2%                             |

| 119  | 0x77 | 9.30                 | 0.70                 | 93.0%                             |

| 120  | 0x78 | 9.38                 | 0.63                 | 93.8%                             |

| 121  | 0x79 | 9.45                 | 0.55                 | 94.5%                             |

| 122  | 0x7A | 9.53                 | 0.47                 | 95.3%                             |

| 123  | 0x7B | 9.61                 | 0.39                 | 96.1%                             |

| 124  | 0x7C | 9.69                 | 0.31                 | 96.9%                             |

| 125  | 0x7D | 9.77                 | 0.23                 | 97.7%                             |

| 126  | 0x7E | 9.84                 | 0.16                 | 98.4%                             |

| 127  | 0x7F | 9.92                 | 0.08                 | 99.2%                             |

## 9.5 Programming

## 9.5.1 I<sup>2</sup>C General Operation and Overview

#### 9.5.1.1 START and STOP Conditions

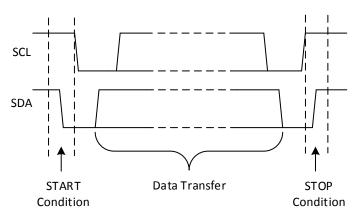

I<sup>2</sup>C communication with this device is initiated by the master sending a START condition and terminated by the master sending a STOP condition. A high-to-low transition on the SDA line while the SCL is high defines a START condition. A low-to-high transition on the SDA line while the SCL is high defines a STOP condition. See Figure 12.

Figure 12. Definition of START and STOP Conditions

#### 9.5.1.2 Data Validity and Byte Formation

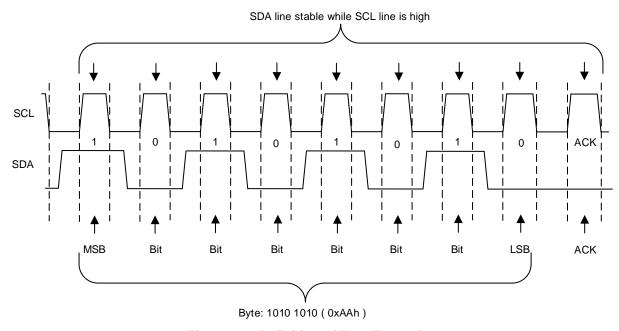

One data bit is transferred during each clock pulse of the SCL. One byte is comprised of eight bits on the SDA line. See Figure 13. A byte may either be a device address, register address, or data written to or read from a slave.

Data is transferred Most Significant Bit (MSB) first. Any number of data bytes can be transferred from the master to slave between the START and STOP conditions. Data on the SDA line must remain stable during the high phase of the clock period, as changes in the data line when the SCL is high are interpreted as control commands (START or STOP).

Figure 13. Definition of Byte Formation

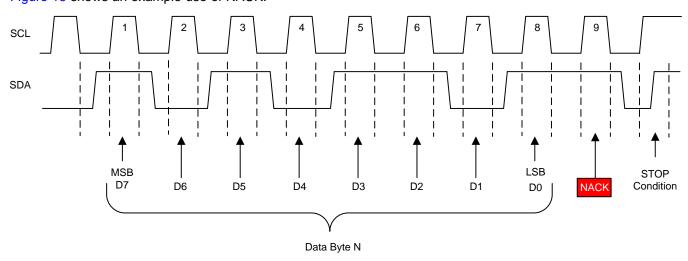

#### 9.5.1.3 Acknowledge (ACK) and Not Acknowledge (NACK)

Each byte is followed by one ACK bit from the receiver. The ACK bit allows the receiver to communicate to the transmitter that the byte was successfully received and another byte may be sent.

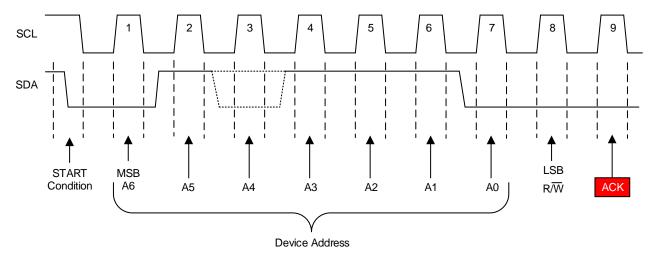

The transmitter must release the SDA line before the receiver can send the ACK bit. To send an ACK bit, the receiver shall pull down the SDA line during the low phase of the ACK/NACK-related clock period (period 9), so that the SDA line is stable low during the high phase of the ACK/NACK-related clock period. Consider setup and hold times. Figure 14 shows an example use of ACK.

Submit Documentation Feedback

Figure 14. Example Use of ACK

When the SDA line remains high during the ACK/NACK-related clock period, this is a NACK signal. There are several conditions that lead to the generation of a NACK:

- The receiver is unable to receive or transmit because it is performing some real-time function and is not ready

to start communication with the master.

- During the transfer, the receiver gets data or commands that it does not understand.

- During the transfer, the receiver cannot receive any more data bytes.

- A master-receiver is done reading data and indicates this to the slave through a NACK.

Figure 15 shows an example use of NACK.

Figure 15. Example Use of NACK

#### 9.5.1.4 Repeated Start

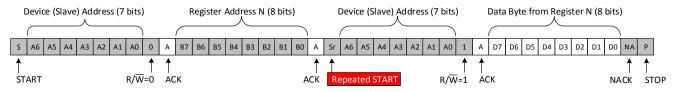

A repeated START condition may be used in place of a complete STOP condition follow by another START condition when performing a read function. The advantage of this is that the I<sup>2</sup>C bus does not become available after the stop and therefore prevents other devices from grabbing the bus between transfers.

### 9.5.2 Programing with I<sup>2</sup>C

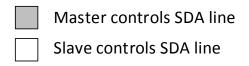

### 9.5.2.1 Write Operation

To write on the I<sup>2</sup>C bus, the master sends a START condition on the bus with the address of the slave, as well as the last bit (the R/W bit) set to 0, which signifies a write. After the slave responds with an acknowledge, the master then sends the register address of the register to which it wishes to write. The slave acknowledges again, letting the master know that it is ready. After this, the master starts sending the register data to the slave until the master has sent all the data necessary (which is sometimes only a single byte), and the master terminates the transmission with a STOP condition. See Figure 16.

### Write to one register in a device

Figure 16. Write Operation

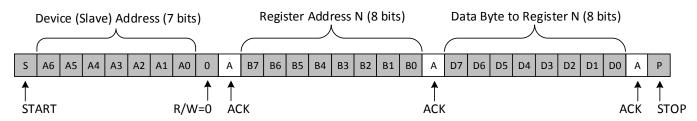

#### 9.5.2.2 Read Operation

Reading from a slave is very similar to writing, but requires some additional steps. in order to read from a slave, the master must first instruct the slave which register it wishes to read from. This is done by the master starting off the transmission in a similar fashion as the write, by sending the address with the R/W bit equal to 0 (signifying a write), followed by the register address it wishes to read from. When the slave acknowledges this register address, the master sends a START condition again, followed by the slave address with the R/W bit set to 1 (Signifying a read). This time, the slave acknowledges the read request, and the master releases the SDA bus but continues supplying the clock to the slave. During this part of the transaction, the master becomes the master-receiver, and the slave becomes the slave-transmission.

The master continues to send out the clock pulses, for each byte of data that it wishes to receive. At the end of every byte of data, the master sends an ACK to the slave, letting the slave know that it is ready for more data. When the master has received the number of bytes it was expecting (or needs to stop communication), it sends a NACK, signaling to the slave to halt communications and release the bus. The master follows this up with a STOP condition. Figure 17 shows the read operation from one register.

Submit Documentation Feedback

#### Read from one register in a device

#### Read from one register in a device (Repeated Start)

Figure 17. Read Operation from One Register

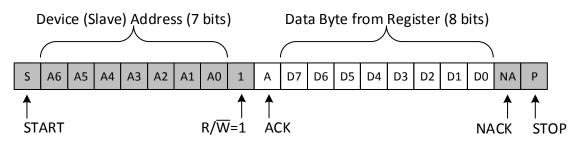

## Read from one register in a device with single register

Figure 18. Short Read Operation

The TPL0401x-10 has 1 register, and it is not a requirement that the register address be sent before a read. A shorter read allows the user to simply send a read request to the device address as shown in Figure 18.

#### 9.6 Register Maps

#### 9.6.1 Slave Address

Table 2 and Table 3 show the TPL0401A-10 and TPL0401B-10 bit address repectively.

#### Table 2. TPL0401A-10 Bit Address

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| (MSB) |       |       |       |       |       |       | (LSB) |

| 0     | 1     | 0     | 1     | 1     | 1     | 0     | R/W   |

#### Table 3. TPL0401B-10 Bit Address

| BIT 7<br>(MSB) | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0<br>(LSB) |

|----------------|-------|-------|-------|-------|-------|-------|----------------|

| 0              | 1     | 1     | 1     | 1     | 1     | 0     | R/W            |

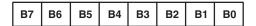

### 9.6.2 Register Address

Following the successful acknowledgment of the address byte, the bus master sends a command byte as shown in Figure 19, which is stored in the Control Register in the TPL0401x-10. The TPL0401x-10 has only 1 register, but requires the command byte be sent during communication.

Figure 19. Register Address Byte

Table 4 shows the TPL0401x-10 register address byte.

**Table 4. Register Address Byte**

|    |    | REGIS | STER A | DDRESS | BITS |    |    | REGISTER         |                | POWER-UP        |                     |

|----|----|-------|--------|--------|------|----|----|------------------|----------------|-----------------|---------------------|

| В7 | В6 | B5    | В4     | В3     | B2   | B1 | В0 | ADDRESS<br>(HEX) | REGISTER       | PROTOCOL        | DEFAULT             |

| 0  | 0  | 0     | 0      | 0      | 0    | 0  | 0  | 0x00             | Wiper Position | Read/Write byte | 0100 0000<br>(0×40) |

See Table 1 for more information on the wiper position register values. Note that the MSB is always discarded during a write to the wiper position register. For example, if 0x80 is written to the wiper position register, a read returns 0x00. Another similar example is if 0xFF is written, then 0x7F is read.

Submit Documentation Feedback

## 10 Application and Implementation

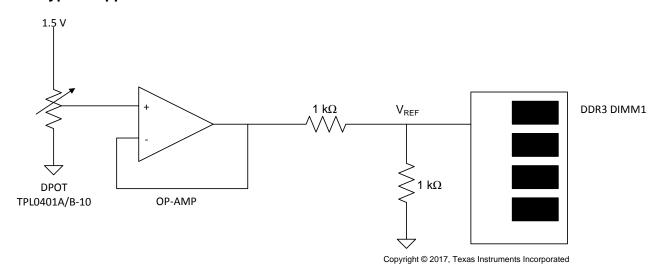

## **10.1** Application Information

There are many applications in which voltage division is needed through the use of a digital potentiometer such as the TPL0401x-10; this is one example of the many. In conjunction with many amplifiers, the TPL0401x-10 can effectively be used in voltage divider mode to create a buffer to adjust the reference voltage for DDR3 DIMM1 Memory.

## 10.2 Typical Application

Figure 20. DDR3 Voltage Reference Adjustment

#### 10.2.1 Design Requirements

Table 5 lists the design parameters for this example.

**Table 5. Design Parameters**

| PARAMETER     | EXAMPLE VALUE |  |  |  |

|---------------|---------------|--|--|--|

| Input voltage | 1.5 V         |  |  |  |

| $V_{REF}$     | 0 V to 0.75 V |  |  |  |

#### 10.2.2 Detailed Design Procedure

The TPL0401x-10 can be used in voltage divider mode with a unity-gain op amp buffer to provide a clean voltage reference for DDR3 DIMM1 Memory. The analog output voltage,  $V_{REF1}$  is determined by the wiper setting programmed through the  $I^2C$  bus.

The op amp is required to buffer the high-impedance output of the TPL0401x-10 or else loading placed on the output of the voltage divider affects the output voltage.

## 10.2.3 Application Curve

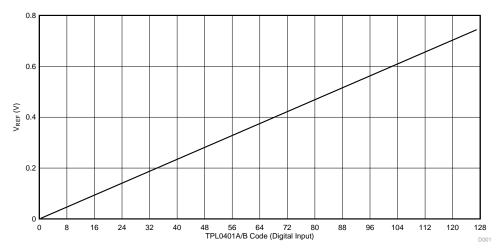

The voltage, 1.5 V, applied to terminal H of TPL0401x-10 determines the voltage that is buffered by the unity-gain op amp and divided as the DDR3 DIMM1 voltage reference. By using the TPL0401x-10, and dividing the 1.5 V, a maximum of 0.75 V is applied to the buffer and passed to the voltage divider. The output voltage then ranges from 0 V to 0.75 V.

Figure 21. TPL0401-10 Digital Input vs Reference Voltage for DDR3 DIMM Memory

## 11 Power Supply Recommendations

## 11.1 Power Sequence

Protection diodes limit the voltage compliance at SDA, SCL, terminal H, and terminal W, making it important to power up  $V_{DD}$  first before applying any voltage to SDA, SCL, terminal H, and terminal W. The diodes are forward-biasing, meaning  $V_{DD}$  can be powered unintentionally if  $V_{DD}$  is not powered first. The ideal power-up sequence is  $V_{DD}$ , digital inputs, and  $V_{W}$  and  $V_{H}$ . The order of powering digital inputs,  $V_{H}$  and  $V_{W}$  does not matter as long as they are powered after  $V_{DD}$ .

## 11.2 Power-On Reset Requirements

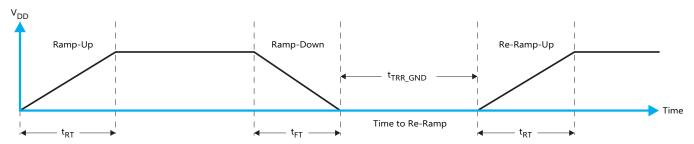

In the event of a glitch or data corruption, the TPL0401-10 can be reset to its default conditions by using the power-on reset feature. Power-on reset requires that the device go through a power cycle to be completely reset. This reset also happens when the device is powered on for the first time in an application.

Figure 22. V<sub>DD</sub> is Lowered to 0 V and then Ramped Up to V<sub>DD</sub>

Table 6 specifies the performance of the power-on reset feature for the TPL0401-10 for both types of power-on reset.

Table 6. Recommended Supply Sequencing and Ramp Rates at  $T_A = 25^{\circ}C^{(1)}$

|                     | PARAMETER                                           |               | MIN    | MAX  | UNIT |

|---------------------|-----------------------------------------------------|---------------|--------|------|------|

| t <sub>FT</sub>     | Fall rate                                           | See Figure 22 | 0.0001 | 1000 | ms   |

| t <sub>RT</sub>     | Rise rate                                           | See Figure 22 | 0.0001 | 1000 | ms   |

| t <sub>RR_GND</sub> | Time to re-ramp (when V <sub>DD</sub> drops to GND) | See Figure 22 | 1      |      | μS   |

<sup>(1)</sup> Not tested. Specified by design.

## 11.3 I<sup>2</sup>C Communication After Power Up

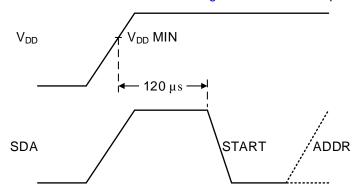

In order to ensure a complete device reset after a power up condition, the user must wait 120 µs after power up before initiating communication with the TPL0401x-10. See Figure 23 for an example waveform.

Figure 23. Recommended Start Up Sequence

Copyright © 2011–2017, Texas Instruments Incorporated

Submit Documentation Feedback

## 11.4 Wiper Position While Unpowered and After Power Up

When DPOT is powered off, the impedance of the device is undefined and not known.

Upon power-up, the device returns to 0×40h code because this device does not contain non-volatile memory.

Submit Documentation Feedback

Copyright © 2011–2017, Texas Instruments Incorporated

## 12 Layout

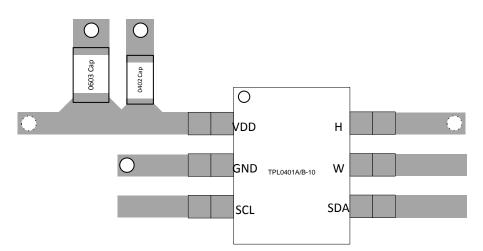

## 12.1 Layout Guidelines

To ensure reliability of the device, follow common printed-circuit board (PCB) layout guidelines:

- · Leads to the input must be as direct as possible with a minimum conductor length.

- The ground path must have low resistance and low inductance.

- · Use short trace-lengths to avoid excessive loading.

- It is common to have a dedicated ground plane on an inner layer of the board.

- Terminals that are connected to ground must have a low-impedance path to the ground plane in the form of wide polygon pours and multiple vias.

- Use bypass capacitors on power supplies and placed them as close as possible to the V<sub>DD</sub> pin.

- Apply low equivalent series resistance (0.1-μF to 10-μF tantalum or electrolytic capacitors) at the supplies to minimize transient disturbances and to filter low-frequency ripple.

- To reduce the total I<sup>2</sup>C bus capacitance added by PCB parasitics, data lines (SCL and SDA) must be as short as possible and the widths of the traces must also be minimized (for example, 5 to 10 mils depending on copper weight).

### 12.2 Layout Example

Via to VDD Power Plane

Via to GND Plane

Figure 24. Layout Recommendation

## 13 Device and Documentation Support

### 13.1 Documentation Support

#### 13.1.1 Related Documentation

For related documentation, see the following:

- PC Bus Pullup Resistor Calculation

- Understanding the l<sup>2</sup>C Bus

- TPL0401 Evaluation Module User's Guide

#### 13.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to order now.

Table 7. Related Links

| PARTS    | PRODUCT FOLDER | ORDER NOW  | TECHNICAL DOCUMENTS | TOOLS & SOFTWARE | SUPPORT & COMMUNITY |

|----------|----------------|------------|---------------------|------------------|---------------------|

| TPL0401A | Click here     | Click here | Click here          | Click here       | Click here          |

| TPL0401B | Click here     | Click here | Click here          | Click here       | Click here          |

## 13.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 13.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 13.5 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 13.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 13.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

9-Sep-2014

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|----------------------|---------|

| TPL0401A-10DCKR  | ACTIVE | SC70         | DCK                | 6    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | (7TD ~ 7TV)          | Samples |

| TPL0401B-10DCKR  | ACTIVE | SC70         | DCK                | 6    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | (7UD ~ 7UV)          | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **PACKAGE OPTION ADDENDUM**

9-Sep-2014

| n no event shall TI's liability arisir | ng out of such information exceed the total | purchase price of the TI part(s) a | at issue in this document sold by | / TI to Customer on an annual basis. |

|----------------------------------------|---------------------------------------------|------------------------------------|-----------------------------------|--------------------------------------|

|                                        |                                             |                                    |                                   |                                      |

## PACKAGE MATERIALS INFORMATION

www.ti.com 18-Jul-2014

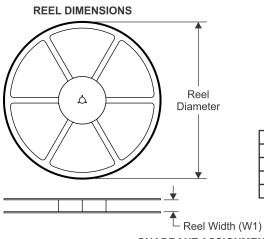

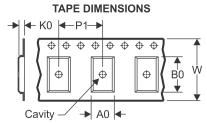

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

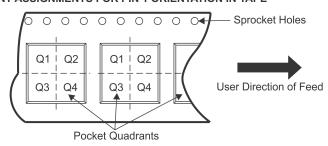

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPL0401A-10DCKR | SC70            | DCK                | 6 | 3000 | 180.0                    | 8.4                      | 2.41       | 2.41       | 1.2        | 4.0        | 8.0       | Q3               |

| TPL0401B-10DCKR | SC70            | DCK                | 6 | 3000 | 180.0                    | 8.4                      | 2.41       | 2.41       | 1.2        | 4.0        | 8.0       | Q3               |

www.ti.com 18-Jul-2014

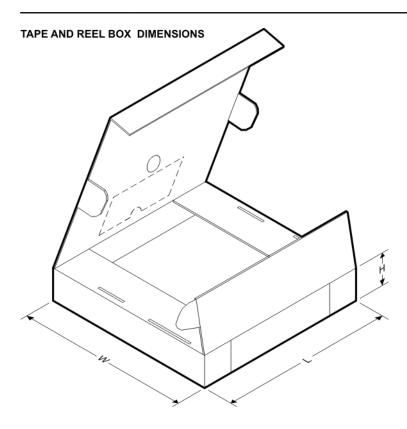

#### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPL0401A-10DCKR | SC70         | DCK             | 6    | 3000 | 202.0       | 201.0      | 28.0        |

| TPL0401B-10DCKR | SC70         | DCK             | 6    | 3000 | 202.0       | 201.0      | 28.0        |

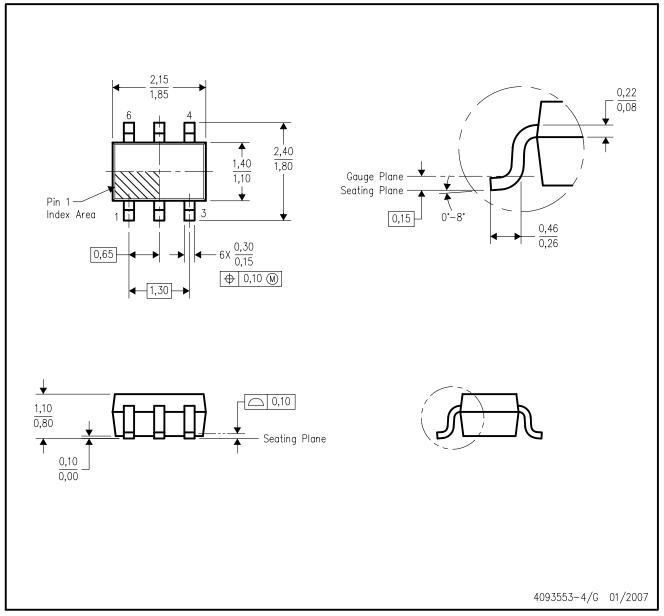

# DCK (R-PDSO-G6)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-203 variation AB.

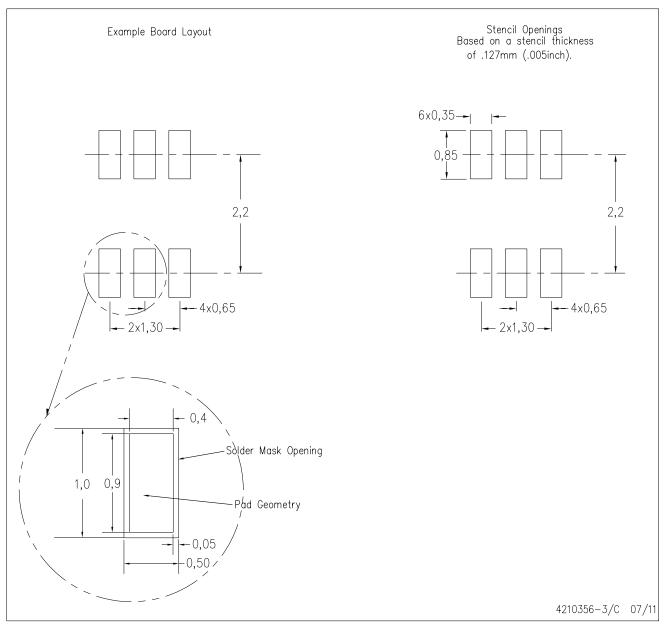

# DCK (R-PDSO-G6)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated