## -48-V HOT SWAP WITH INSERTION AND REMOVAL DETECTION DELAY

## FEATURES

- Wide Input Supply Range: –20 V to –80 V

- Transient Rating to –100 V

- Insertion/Removal Detection Delay

- Extended Debounce Delay

- Programmable Current Limit

- Programmable Current Slew Rate

- Programmable UV/OV Thresholds/Hysteresis

- Open-Drain Power Good (PG) Output

- Fault Timer to Eliminate Nuisance Trips

- Open-Drain Fault Output (FAULT)

- 14-Pin TSSOP package

## APPLICATIONS

- -48-V Distributed Power Systems

- Central Office Switching

- Wireless Base Station

## DESCRIPTION

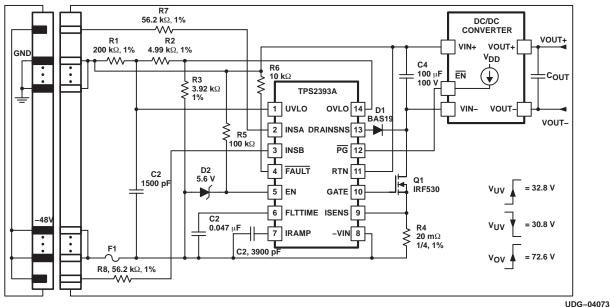

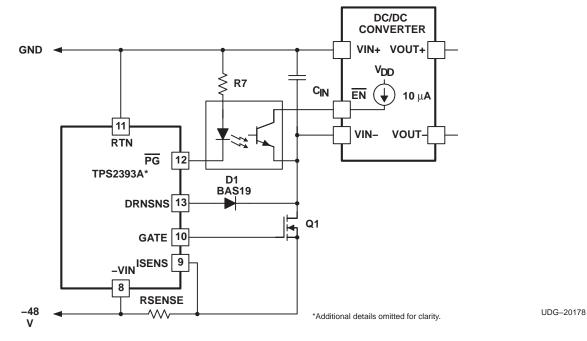

The TPS2393A integrated circuit is a hot swap power manager optimized for use in nominal -48-V systems. It operates with supply voltage ranges from -20-V to -80-V, and is rated to withstand spikes to -100 V. In conjunction with an external N-channel FET and sense resistor, it can be used to enable live insertion of plug-in cards and modules in powered systems. It provides load current slew rate control and peak magnitude limiting. Undervoltage and overvoltage shutdown thresholds are easily programmed via a three-resistor divider network. In addition, two active-low, debounced inputs provide plug-in insertion and removal detection. The associated debounce delay applies to both actions. A power (PG) output enables downstream aood converters. The TPS2393A also provides the basic hot swap functions of electrical isolation of faulty cards, filtered protection against nuisance overcurrent trips, and single-line fault reporting.

The TPS2393A periodically retries the load in the event of a fault.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright © 2004, Texas Instruments Incorporated

#### SLUS610 - JULY 2004

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **ORDERING INFORMATION**

| TA            | FAULT OPERATION | PACKAGE            | PART NUMBER |

|---------------|-----------------|--------------------|-------------|

| -40°C to 85°C | PERIODIC RETRY  | TSSOP (PW)(NO TAG) | TPS2393APW  |

The PW package is also available taped and reeled. Add an R suffix to the device type (i.e., TPS2393APWR) for quantities of 2,500 per reel.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                          |                                                                              | TPS2393A    | UNIT |  |

|------------------------------------------|------------------------------------------------------------------------------|-------------|------|--|

|                                          | UVLO, INSA, INSB, FLTTIME, IRAMP, OVLO, DRAINSNS, GATE, ISENS <sup>(2)</sup> | -0.3 to 15  |      |  |

| Input voltage range, VI                  | RTN <sup>(2)</sup>                                                           |             | 1    |  |

|                                          | EN(2)(3)                                                                     |             | V    |  |

|                                          | FAULT(2)(4)                                                                  | -0.3 to 100 |      |  |

| Output voltage range, VO                 | PG(2)(4)                                                                     | 7           |      |  |

|                                          | FAULT                                                                        | 10          | 1    |  |

| Continuous output current                | PG                                                                           | 10          | mA   |  |

| Operating junction temperature range, TJ |                                                                              | -55 to 125  |      |  |

| Storage temperature, T <sub>Stg</sub>    |                                                                              | -65 to 150  | °C   |  |

| Lead temperature 1,6 mm (1/16 inch) from | case for 10 seconds                                                          | 260         |      |  |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltages are with respect to -VIN (unless otherwise noted).

With 100-k $\Omega$  minimum input series resistance.

With 10-k $\Omega$  minimum series resistance.

## **RECOMMENDED OPERATING CONDITIONS**

|                                                | MIN | NOM MAX | UNIT |

|------------------------------------------------|-----|---------|------|

| Input supply voltage, –VIN to RTN              | -80 | -20     | V    |

| Operating junction temperature, T <sub>J</sub> | -40 | 85      | °C   |

#### **DISSIPATION RATINGS**

| PACKAGE  | T <sub>A</sub> < 25°C | DERATING FACTOR             | T <sub>A</sub> = 85°C |

|----------|-----------------------|-----------------------------|-----------------------|

|          | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          |

| TSSOP-14 | 750 mW                | 7.5 mW/°C                   | 300 mW                |

## **ELECTRICAL CHARACTERISTICS**

$V_{I(-VIN)} = -48 \text{ V with respect to RTN, } V_{I(EN)} = 2.8 \text{ V, } V_{I(INSA)} = 0 \text{ V, } V_{I(INSB)} = 0 \text{ V, } V_{I(UVLO)} = 2.5 \text{ V, } V_{I(OVLO)} = 0 \text{ V, } V_{I(ISENS)}$ all outputs unloaded,  $T_{A} = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (unless otherwise noted)(1)(2)

|                     | PARAMETER                                                 | TEST CONDITIONS                                                                             | MIN   | TYP   | MAX  | UNIT |

|---------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|-------|------|------|

| INPUT SU            | PPLY                                                      |                                                                                             |       |       |      |      |

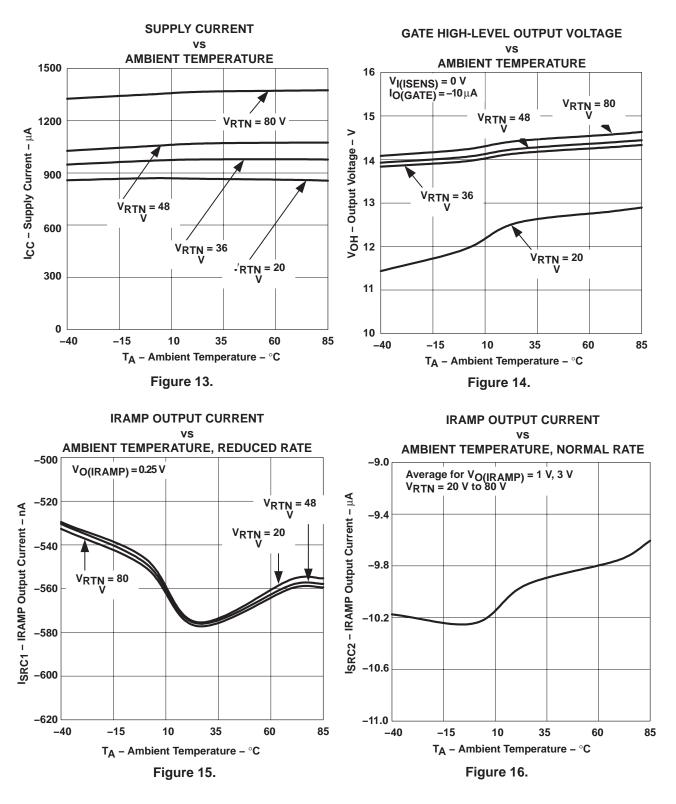

| ICC1                |                                                           | V <sub>I(RTN)</sub> = 48 V                                                                  |       | 1050  | 1500 |      |

| ICC2                | Supply current, RTN                                       | VI(RTN) = 80 V                                                                              |       | 1350  | 1700 | μA   |

| VUVLO_L             | Internal UVLO threshold, VIN rising                       | To GATE pull-up                                                                             | -19   | -16   | -13  | V    |

| V <sub>HYS</sub>    | Internal UVLO hysteresis                                  |                                                                                             |       | 200   |      | mV   |

|                     | NPUT (EN)                                                 | •                                                                                           | •     |       |      |      |

| VTH                 | Threshold voltage, VIN rising                             | To GATE pull-up                                                                             | 1.3   | 1.4   | 1.5  | V    |

| ISRC_EN             | EN pin switched pull-up current                           |                                                                                             | -12   | -10   | -8   | μΑ   |

|                     | DLTAGE/OVERVOLTAGE COMPARATORS                            | •                                                                                           | •     |       |      |      |

| VTH_UV              | Threshold voltage, VIN rising, UVLO                       | To GATE pull-up                                                                             | 1.36  | 1.40  | 1.44 | V    |

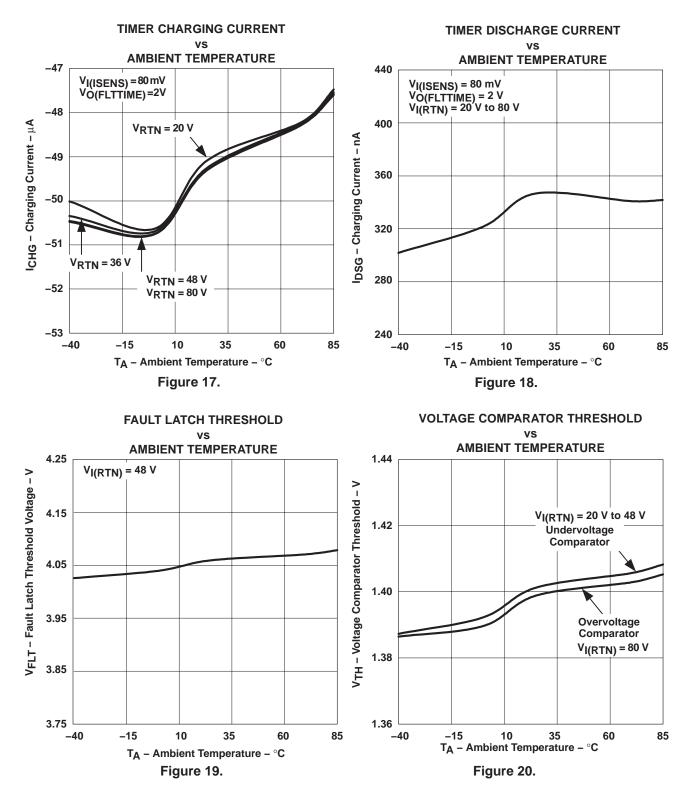

| ISRC_UV             | UVLO pin switched pull-up current                         | V <sub>I(UVLO)</sub> = 2.5 V                                                                | -11.7 | -10.0 | -8.3 | μΑ   |

| IIL                 | UVLO low-level input current                              | $V_{I(UVLO)} = 1 V$                                                                         | -1    |       | 1    | μΑ   |

| VTH_OV              | Threshold voltage, VIN rising, OVLO                       | To GATE pull-up                                                                             | 1.36  | 1.40  | 1.44 | V    |

| ISRC OV             | OLVO pin switched pull-up current                         | VI(OVLO) = 2.5 V                                                                            | -11.7 | -10.0 | -8.3 | μA   |

|                     | OVLO low-level input current                              | $V_{I(OVLO)} = 1 V$                                                                         | -1    |       | 1    | μA   |

|                     | N DETECTION                                               |                                                                                             |       |       |      |      |

| VTH                 | Threshold voltage, V <sub>IN</sub> rising, INSA, INSB     | To GATE pull-down                                                                           | 1.0   | 1.4   | 1.8  | V    |

| ISRC_INS            | INSA, INSB pin pull-up current                            | V <sub>I(INSA)</sub> = 0 V, V <sub>I(INSB)</sub> = 0 V                                      | -14   | -11   | -8   | μΑ   |

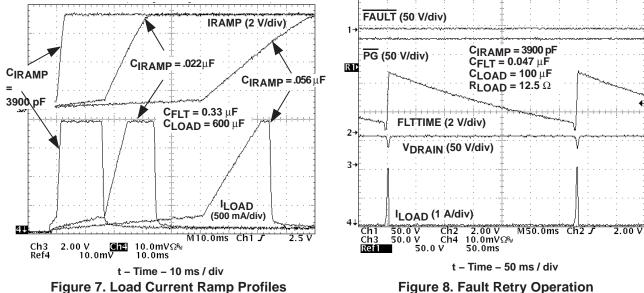

| <sup>t</sup> D INSF | Insertion delay time, V <sub>IN</sub> falling, INSA, INSB | To GATE pull-up                                                                             | 4.25  | 6.20  | 8.25 | ms   |

| <sup>t</sup> D_INSR | Extraction delay time, VIN rising, INSA, INSB             | To GATE pull-down                                                                           | 4.25  | 6.20  | 8.25 | ms   |

|                     | URRENT AMPLIFIER (LCA)                                    |                                                                                             | -     |       |      |      |

| Vон                 | High-level output voltage, GATE                           | $V_{I(ISENS)} = 0 V, I_{O(GATE)} = -10 \mu A$                                               | 11    | 14    | 17   | V    |

| ISINK               | Output sink current, linear mode                          | $V_{I}(ISENS) = 80 \text{ mV}, V_{O}(GATE) = 5 \text{ V}$<br>$V_{O}(FLTTIME) = 2 \text{ V}$ |       | 5     | 10   |      |

| IFAULT              | Output sink current, fault shutdown                       | VI(ISENS) = 80 mV, VO(GATE) = 5 V<br>VO(FLTTIME) > 4 V                                      | 50    | 100   |      | mA   |

| li                  | Input current, ISENS                                      | 0 V < V <sub>I(ISENS)</sub> < 0.2 V                                                         | -1    |       | 1    | μA   |

| V <sub>REF_K</sub>  | Reference clamp voltage                                   | V <sub>O(IRAMP)</sub> = OPEN                                                                | 33    | 40    | 47   |      |

| VIO                 | Input offset voltage                                      | $V_{O(IRAMP)} = 2 V$                                                                        | -7    |       | 7    | mV   |

| RAMP GE             | NERATOR                                                   |                                                                                             |       |       |      |      |

| ISRC1               | IRAMP source current, reduced rate turn-on                | V <sub>O(IRAMP)</sub> = 0.25 V                                                              | -850  | -600  | -400 | nA   |

|                     |                                                           | $V_{O(IRAMP)} = 1 V$                                                                        | -11   | -10   | -9   |      |

| ISRC2               | IRAMP source current, normal rate                         | $V_{O(IRAMP)} = 3 V$                                                                        | -11   | -10   | -9   | μA   |

| Vol                 | Low-level output voltage, IRAMP                           | $V_{I(EN)} = 0 V$                                                                           |       |       | 2    | mV   |

| AV                  | Voltage gain, relative to ISENS                           |                                                                                             | 9.5   | 10.0  | 10.5 | mV/V |

|                     | AD COMPARATOR                                             | •                                                                                           |       |       |      |      |

| VTH_OL              | Current overload threshold, ISENS                         |                                                                                             | 80    | 100   | 120  | mV   |

|                     | Glitch filter delay time                                  | VI(ISENS) = 200 mV                                                                          | 2     | 4     | 7    | μs   |

$(1) \qquad \qquad \text{All voltages are with respect to the -VIN terminal, unless otherwise stated.}$

(2) Currents are positive into and negative out of the specified terminals.

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{I(-VIN)} = -48 \text{ V with respect to RTN, } V_{I(EN)} = 2.8 \text{ V, } V_{I(INSA)} = 0 \text{ V, } V_{I(INSB)} = 0 \text{ V, } V_{I(UVLO)} = 2.5 \text{ V, } V_{I(OVLO)} = 0 \text{ V, } V_{I(ISENS)}$ all outputs unloaded,  $T_{A} = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  (unless otherwise noted)

|                     | PARAMETER                                    | TEST CONDITIONS                                                   | MIN  | TYP  | MAX  | UNIT |

|---------------------|----------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| FAULT T             | IMER                                         |                                                                   |      |      |      |      |

| VOL                 | Low-level output voltage, FLTTIME            | $V_{I(EN)} = 0 V$                                                 |      |      | 5    | mV   |

| ICHG                | Charging current, current limit mode         | VI(ISENS) = 80 mV, VO(FLTTIME) = 2 V                              | -55  | -50  | -45  | μΑ   |

| V <sub>FLT</sub>    | Fault threshold voltage                      |                                                                   | 3.75 | 4.00 | 4.25 | V    |

| IDSG                | Discharge current, retry mode TPS2393        | VI(ISENS) = 80 mV, VO(FLTTIME) = 2 V                              |      | 0.38 | 0.61 | μΑ   |

| D                   | Output duty cycle TPS2393                    | VI(ISENS) = 80 mV                                                 |      | 1.0% | 1.5% |      |

| IRST                | Discharge current, timer reset mode          | V <sub>O(FLTTIME)</sub> = 2 V, V <sub>I(ISENS)</sub> = 0 V        |      | 1    |      | mA   |

| POWER               | GOOD SENSING                                 |                                                                   |      |      |      |      |

| VTH                 | DRAINSNS threshold voltage                   |                                                                   | 1.20 | 1.35 | 1.50 | V    |

| ISRC                | DRAINSNS pull-up current                     | VI(DRAINSNS) = 0 V                                                | -14  | -11  | -8   |      |

| ЮН                  | High-level output leakage current, PG output | $V_{I(EN)} = 0 V, V_{O}(\overline{PG}) = 65 V$                    |      |      | 10   | μA   |

| R <sub>DS(on)</sub> | Driver on-resistance, PG output              | $V_{I}(ISENS) = 0 V, V_{I}(DRAINSNS) = 0 V$<br>$I_{O}(PG) = 1 mA$ |      | 50   | 80   | Ω    |

| FAULT C             | DUTPUT                                       |                                                                   |      |      |      |      |

| ЮН                  | High-level output leakage current, FAULT     | $V_{I(EN)} = 0 V, V_{O}(\overline{FAULT}) = 65 V$                 |      |      | 10   | μA   |

| R <sub>DS(on)</sub> | Driver on-resistance, FAULT                  | $V_{I}(ISENS) = 80 V, VO(FLTTIME) = 5 V$<br>IO(FAULT) = 1 mA      |      | 50   | 80   | Ω    |

(1) All voltages are with respect to the –VIN terminal, unless otherwise stated.

(2) Currents are positive into and negative out of the specified terminals.

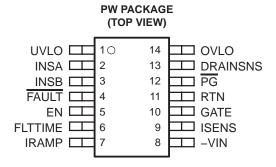

#### **TERMINAL FUNCTIONS**

| TERMIN   | AL  |     | DECODIDEION                                                           |

|----------|-----|-----|-----------------------------------------------------------------------|

| NAME     | NO. | I/O | DESCRIPTION                                                           |

| DRAINSNS | 13  | Ι   | Sense input for monitoring the load voltage status                    |

| EN       | 5   | Т   | Enable input to turn on/off power to the load                         |

| FAULT    | 4   | 0   | Open-drain, active-low indication of a load fault condition           |

| FLTTIME  | 6   | I/O | Connection for user-programming of the fault timeout period           |

| GATE     | 10  | 0   | Gate drive for external N-channel FET                                 |

| INSA     | 2   | Ι   | Insertion detection input pin A                                       |

| INSB     | 3   | Ι   | Insertion detection input pin B                                       |

| IRAMP    | 7   | I/O | Programming input for setting the inrush current slew rate            |

| ISENS    | 9   | Т   | Current sense input                                                   |

| OVLO     | 14  | Ι   | Voltage sense input for supply overvoltage lockout (OVLO) protection  |

| PG       | 12  | 0   | Open-drain, active-low indication of load power-good condition        |

| RTN      | 11  | Ι   | Positive supply input                                                 |

| UVLO     | 1   | Ι   | Voltage sense input for supply undervoltage lockout (UVLO) protection |

| -VIN     | 8   | Ι   | Negative supply input and reference pin                               |

### **PIN ASSIGNMENTS**

**DRAINSNS**: Sense input for monitoring the load voltage status. The DRAINSNS pin determines the load status by sensing the voltage level on the external pass FET drain. DRAINSNS must be pulled low with repect to –VIN (less than 1.35 V typically) to declare a power good condition. This corresponds to a low V<sub>DS</sub> across the FET, indicating that the load voltage has successfully ramped up to the DC input level. DRAINSNS must be connected to the FET drain through a small-signal blocking diode as shown in the typical application diagram. An internal pull-up maintains a high logic level at the pin until overridden by a fully-enhanced external FET.

**EN**: Enable input to turn on/off power to the load. The EN pin is referenced to the –VIN potential of the circuit. When this input is pulled high (above the nominal 1.4-V threshold), and all other input qualifications are met (supply above device undervoltage lockout (UVLO), UVLO pin high and OVLO pin low, INSx pins pulled low) the device enables the GATE output, and begins the ramp of current to the load. When this input is low, the linear current amplifier (LCA) is disabled, and a large pull-down device is applied to the FET gate, disabling power to the load.

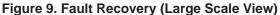

**FAULT**: Open-drain, active-low indication of a load fault condition. When the device EN is deasserted, or when enabled and the load current is less than the programmed limit, this output is high impedance. If the device remains in current regulation mode at the expiration of the fault timer, the fault is latched, the load is turned off, and the FAULT pin is pulled low (to –VIN). The TPS2393A retries the load at approximately a 1% duty cycle.

**FLTTIME**: Connection for user-programming of the fault timeout period. An external capacitor connected from FLTTIME to –VIN establishes the timeout period to declare a fault condition. This timeout protects against indefinite current sourcing into a faulted load, and also provides a filter against nuisance trips from momentary current spikes or surges. The TPS2393A defines a fault condition as voltage at the ISENS pin at or greater than the 40-mV fault threshold. When a fault condition exists, the timer is active. The device manages fault timing by charging the external capacitor to the 4-V fault threshold, then discharging it at approximately 1% the charge rate to establish the duty cycle for retrying the load. Whenever the internal fault latch is set (timer expired), the pass FET is rapidly turned off, and the FAULT output is asserted.

**GATE**: Gate drive for external N–channel FET. When enabled, and the input supply is above the UVLO threshold, the gate drive is enabled and the device begins charging an external capacitor connected to the IRAMP pin. This pin voltage is used to develop the reference voltage at the non-inverting input of the internal LCA. The inverting input is connected to the current sense node, ISENS. The LCA acts to slew the pass FET gate to force the ISENS voltage to track the reference. The reference is internally clamped at 40 mV, so the maximum current that can be sourced to the load is determined by the sense resistor value as IMAX  $\leq$  40 mV/R<sub>SENSE</sub>. Once the load voltage has ramped up to the input dc potential, and current demand drops off, the LCA drives the GATE output to about 14 V to fully enhance the pass FET, completing the low-impedance supply return path for the load.

**INSA**: Insertion detection input pin A. The INSA and INSB inputs work together to provide an insertion detection function for TPS2393A applications. In order to turn on the FET gate drive (the GATE output), both INSA and INSB must be pulled below the detection threshold, approximatey 1.4 V. Implementations using this feature provide a mechanism for resistively pulling these pins to –VIN potential (device ground), through the backplane wiring. When used with slot connector pin staging this feature can keep the plug-in powered off during contact bounce periods of the power pins. An on-chip pull-up is provided at each INSx pin; no additional pull-up is needed to hold the pins high during the insertion and extraction processes. The insertion inputs are debounced with a nominal 6.2-ms filter.

**INSB**: Insertion detection input pin B. See INSA description.

## PIN ASSIGNMENTS

**IRAMP**: Programming input for setting the inrush current slew rate. An external capacitor connected between this pin and –VIN establishes the load current slew rate whenever power to the load is enabled. The device charges the external capacitor to establish the reference input to the LCA. The closed-loop control of the LCA and pass FET acts to maintain the current sense voltage at ISENS at the reference potential. Since the sense voltage is developed as the drop across a resistor, the load current slew rate is set by the voltage ramp rate at the IRAMP pin. When the output is disabled for any reason (e.g., EN deassertion, voltage or current fault, etc.), the capacitor is discharged and held low to initialize it for the next turn-on event.

**ISENS**: Current sense input. An external low-value resistor connected between this pin and –VIN is used to feed back current magnitude information to the TPS2393A. There are two internal device thresholds associated with the voltage at the ISENS pin. During ramp-up of the load's input capacitance, or during other periods of excessive demand, the HSPM acts to limit this voltage to 40 mV. Whenever the LCA is in current regulation mode, the capacitor at FLTTIME is charged to activate the timer. If, when the LCA is driving to its supply rail, a fast-acting fault such as a short-circuit, causes the ISENS voltage to exceed 100 mV (the overload threshold), the GATE pin is pulled low rapidly, bypassing the fault timer. Overload faults are not immediately latched. Once the current drops below the 100-mV threshold due to the GATE pull-down, control is quickly returned to the LCA to turn the FET back on in current limit mode and test the persistance of the fault.

**OVLO**: Voltage sense input for supply overvoltage lockout (OVLO) protection. Overvoltage protection can be achieved by applying a divided down sample of the input supply voltage to this pin. In order to turn on gate drive to the external FET, the OVLO pin must be below the 1.4-V typical threshold, while all other input qualifications are met. If the OVLO pin is raised above this threshold, as with increasing supply voltage, the GATE output is pulled low, interrupting the supply to the load. An internal 10- $\mu$ A pull-up is switched to this pin when the threshold is exceeded, providing a mechanism for setting the amount of OVLO hysteresis along with the trip threshold.

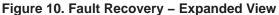

**PG**: Open-drain, active-low indication of load power good condition. The TPS2393A device defines power good as the voltage at the DRAINSNS pin below the power good threshold, and the voltage at the IRAMP pin being above 5 V. This assures that full programmed sourcing current is available to the load prior to declaring power good, even with very slow current ramp rates. The additional protection prevents potential discharging of the module bulk capacitance during load turn-on.

**RTN**: Positive supply input for the TPS2393A. For negative voltage systems, the supply pin connects directly to the return node of the input power bus. Internal regulators step down the input voltage to generate the various supply levels used by the TPS2393A.

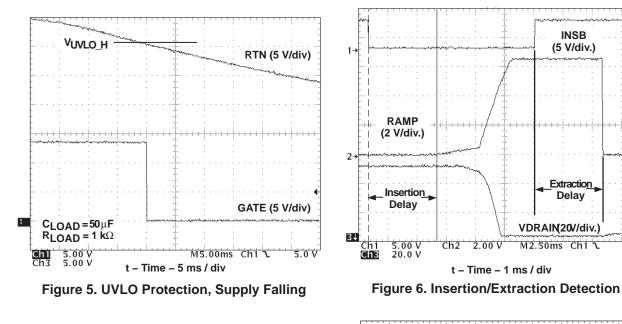

**UVLO**: Voltage sense input for supply uvervoltage lockout (UVLO) protection. Undervoltage protection can be achieved by applying a divided down sample of the input supply voltage to this pin. In order to turn on the gate drive to the external FET, the UVLO pin must be above the 1.4-V typical threshold, while all other input qualifications are met. If the UVLO pin drops below this threshold, as with decreasing supply voltage, the GATE output is pulled low, interrupting the supply to the load. An internal 10- $\mu$ A pull–up is switched to this pin when the threshold is exceeded, providing a mechanism for setting the amount of UVLO hysteresis along with the trip threshold.

For proper operation, a minimum 1500-pF capacitor, connected between the UVLO and -VIN pins, is required.

-VIN: Negative supply input and reference pin for the TPS2393A. This pin connects directly to the input supply negative rail. The input and output pins and all internal circuitry are referenced to this pin, so it is essentially the GND or VSS pin of the device.

SLUS610 - JULY 2004

### **TYPICAL CHARACTERISTICS**

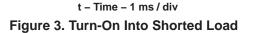

t – Time – 5 ms / div Figure 4. UVLO Protection, Supply Rising

M5.00ms Ch2 J 1.40 V

Chi 5.00 V Ch3 5.00 V

## **TYPICAL CHARACTERISTICS**

INSB

(5 V/div.)

Extraction

Delay

2.5

VDRAIN(20V/div.)

M2.50ms Ch1 \

SLUS610 - JULY 2004

Figure 11. PG Output Timing, Voltage Qualified

Figure 12. PG Output Timing, Current Qualified

### **TYPICAL CHARACTERISTICS**

SLUS610 - JULY 2004

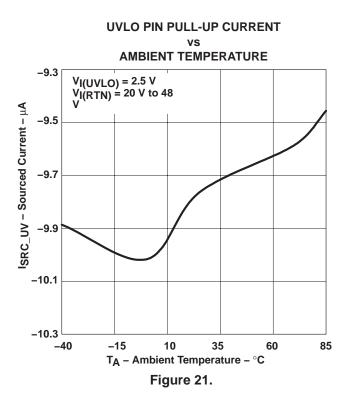

#### **DETAILED DESCRIPTION**

When a plug-in module or printed circuit card is inserted into a live chassis slot, discharged supply bulk capacitance on the board can draw huge transient currents from the system supplies. Without some form of inrush limiting, these currents can reach peak magnitudes ranging over 100 A, particularly in high-voltage systems. Such large transients can damage connector pins, PCB etch, and plug-in and supply components. In addition, current spikes can cause voltage droops on the power distribution bus, causing other boards in the system to reset.

The TPS2393A is a hot swap power manager that limits current peaks to preset levels, as well as controls the slew rate (di/dt) at which charging current ramps to the programmed limit. This device uses an external N-channel pass FET and sense element to provide closed-loop control of current sourced to the load. Input undervoltage lockout (UVLO) and overvoltage lockout (OVLO) functions control automatic turn-on when the input supply voltage is within the specified operational window, otherwise inhibiting card operation by turning off the pass FET. In addition, load power can be controlled with a system logic command via the EN input, allowing electrical isolation of faulty cards from the power bus. Two active-low inputs can be connected to provide card insertion detection. An internal overload comparator provides circuit breaker protection against short-circuits occurring during steady-state (post-turn-on) operation of the card. Load power status is continuously monitored and reported via the PG (powergood) and FAULT outputs.

## **DETAILED DESCRIPTION**

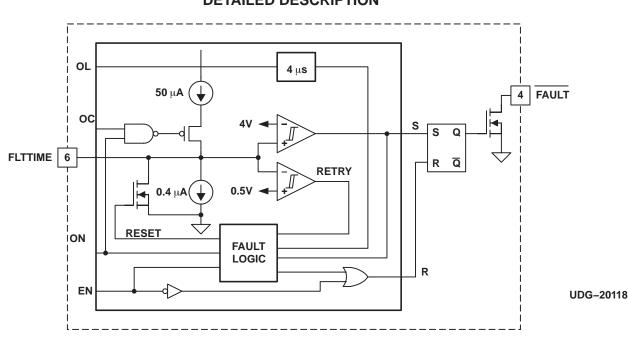

The TPS2393A operates directly from the input supply (nominal –48 V<sub>DC</sub>) rail. The –VIN pin connects to the negative voltage rail, and the RTN pin connects to the supply return. Internal regulators convert input power to the supply levels required by the device circuitry. An input UVLO circuit holds the GATE output low until the supply voltage reaches a nominal 16-V level, regardless of the status of all other control inputs. A block of comparators monitors input supply voltage and other output enable conditions. As shown in Figure 24, the status of these five comparators is AND'd together in order to enable turning on power to the load. Two precision comparators monitor the voltage levels at the UVLO and OVLO pins. Typically, these pins are driven with a divided-down sample of the supply voltage to establish the UVLO and OVLO trip thresholds for the circuit. The UVLO input must be above the internal 1.4-V reference, and the OVLO pin must remain below the reference voltage to enable the load. Both of these inputs are provided with a small, 10- $\mu$ A pull-up source, which is switched to the input pin whenever the associated comparator is tripped. These current sources provide a mechanism for user-programming of the amount of hysteresis for the UVLO and OVLO thresholds.

The same comparator circuit is also available at the EN pin, providing a third precision input. A switched pull-up is also available at this pin for hysteresis programming. Alternatively, this input can be used as a logic enable command, with a nominal 1.4-V logic threshold.

The INSA and INSB pins provide an optional insertion detection function to the hot swap circuit. Both these pins must be pulled low, below 1.0 -V to enable a load start-up. Internal pull-ups at these inputs maintain a HI logic level (about 6.5 V) at the device pins when floating. This eliminates the need for additional external components to maintain the HI logic level during insertion and extraction events. An external mechanism for pulling these inputs low, typically though backplane connections to the low-side rail, starts a timer to hold off power up during contact bounce. Loss of either input assertion resets the timer. Once the inserted condition is latched with expiration of the 6-ms timer, the timer is then used to filter the inputs against transient spikes due to supply noise and glitches in the power distribution.

Once the device is enabled (internal EN\_A signal asserted), the GATE output pull-down is turned off, and the linear control amplifier (LCA) is enabled. A current source in the ramp generator block begins charging an external capacitor connected between the IRAMP and –VIN pins. The resultant voltage ramp at the IRAMP pin is scaled by a factor of 1/100, and applied to the non-inverting input of the LCA (the VLIM signal). Load current magnitude information at the ISENS pin is applied to the inverting input. This sense voltage is developed by connecting the current sense resistor between ISENS and –VIN. As the external FET begins to conduct, the LCA slews its gate to force the ISENS voltage to track the internal reference (VLIM). Consequently, the load current slew rate tracks the linear voltage ramp at the IRAMP pin, producing a linear di/dt of current to the load.

Figure 22. Block Diagram

Under normal load and input supply conditions, this controlled current charges the module's input bulk capacitance up to the input dc voltage level. At this point, the load demand drops off, and the voltage at ISENS decreases. The LCA now drives the GATE output to its supply rail. The 14-V typical output level ensures sufficient overdrive to fully enhance the external FET, while not exceeding the typical 20-V  $V_{GS}$  rating of common N-channel power MOSFETs.

## DETAILED DESCRIPTION

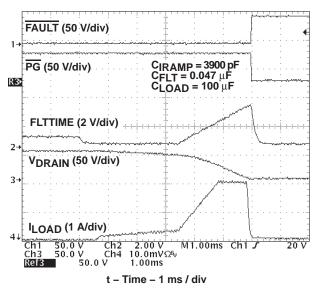

Current fault response timing and retry duty cycle are accomplished by the fault timer block in conjunction with an external capacitor connected between the FLTTIME and –VIN pins. Whenever the hot swap controller is in current control mode, such as during inrush limiting at insertion, or in response to excessive demand during operation of the plug-in, the LCA asserts the OVERCURRENT signal shown in Figure 24. This signal starts the charging of the FLTTIME capacitor. If this capacitor charges to the pin's 4-V trip threshold, the fault is latched. A latched fault disables the LCA drive, and turns on a large pull-down device at the GATE output to rapidly turn off the external FET. The fault condition is indicated by turning on the open-drain FAULT output driver. A latched fault also causes discharge of the external capacitor at the IRAMP pin, in order to reset the hot swap circuit for the next output enable event. Slow discharge of the timing capacitor at about 1/100th the charging rate initiates fault retry operation at a 1% duty cycle. This enables periodic testing for persistance or removal of the fault condition.

An internal overload comparator (OLC in Figure 24) also monitors the ISENS voltage against a nominal 100-mV threshold. This comparator provides circuit breaker protection against sudden current fault conditions, such as a load short-circuit. The OVERLOAD output of this comparator also drives the fault timer. In this case, the timer circuit applies only a 4-µs deglitch filter to help reduce nuisance trips. However, if the overload condition exceeds the filter length, the FET is momentarily snapped off, after which it is quickly turned back on in current ramp or current limit mode. At this point, fault timing commences as above.

The  $\overline{PG}$  pin is an open-drain, active-low indication of a load power good status. Load voltage sensing is provided at the DRAINSNS pin. To assert  $\overline{PG}$ , the device must not be in latched current fault status, the DRAINSNS pin must be pulled below the 1.35-V nominal threshold, and the voltage at the IRAMP pin must be greater than approximately 5 V. This last criteria ensures that maximum allowed sourcing current is available to the load before declaring power good. Once all the conditions are met, the  $\overline{PG}$  status is latched on-chip. This prevents instances of momentary current-limit operation (e.g., due to load surges or voltage spikes on the input supply) from propagating through to the  $\overline{PG}$  output. However, if input conditions are not met, or if a persistent load fault does result in fault timeout, the  $\overline{PG}$  latch will be cleared.

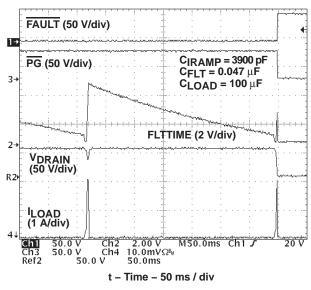

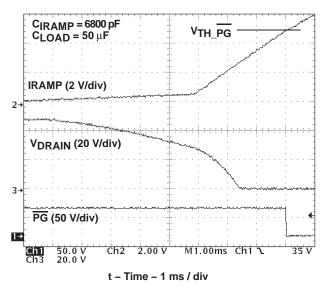

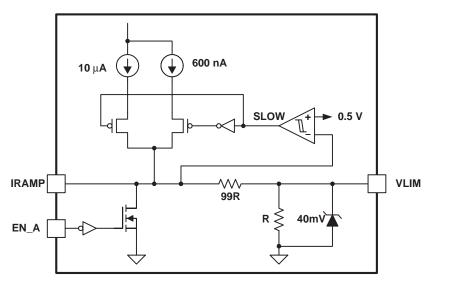

Additional details of the ramp generator operation are shown in Figure 25. To enable the generator, the large NMOS device shown in this circuit is turned off. This allows a small current source to charge the external capacitor connected at the IRAMP pin. The voltage ramp on the capacitor actually has two discrete, linear slopes. As shown in Figure 25, current is supplied from either of two sources. An internal comparator monitors the IRAMP voltage level, and selects the appropriate charging rate. Initially at turn-on, when the pin voltage is 0 V, the 600-nA source is selected, to provide a slow turn-on (or reduced-rate) sourcing period. This slow turn-on ensures that the LCA is pulled out of saturation, and is slewing to the voltage at its non-inverting input before normal rate load charging is allowed. This scheme helps reduce or eliminate current steps at the external FET on-threshold. Once the voltage at the IRAMP pin reaches approximately 0.5 V, the SLOW signal is deasserted, and the 10- $\mu$ A source is selected for the remainder of the ramp period.

The IRAMP pin voltage is divided down by a factor of 100, and applied to the non-inverting input of the LCA (see Figure 24). Although the IRAMP capacitor is charged to about 6.5 V, the VLIM reference is clamped at 40 mV. Therefore, current sourced to the load during turn-on is limited to a value given by IMAX  $\leq$  40 mV/R<sub>SENSE</sub>, where R<sub>SENSE</sub> is the value of the external sense resistor. Therefore, both load current maximum slew rate and peak magnitude are easily set with just two external components.

#### **DETAILED DESCRIPTION**

Figure 23. Ramp Generator Block Details

Note that any condition which causes turn-off of the external FET (EN\_A signal goes low) also causes a rapid discharge of the IRAMP capacitor. In this manner, the soft-start function is automatically reset by the TPS2393A, and ready for the next load enable event.

UDG-20117

Fault timer operation is further detailed in Figure 26. As described earlier, the LCA OVERCURRENT output drives the OC input signal shown in Figure 26. Overcurrent fault timing is actually inhibited during the reduced rate (slow turn-on) portion of the IRAMP voltage waveform. However, once the device transitions to the normal rate current ramp ( $V_{O(IRAMP)} \ge 0.5 V$ ), the FLTTIME capacitor is charge by the 50-µA current source, generating a second voltage ramp at the FLTTIME pin. This voltage is monitored by the two comparators shown in the fault timer block. If this voltage reaches the nominal 4-V comparator threshold, the fault is latched, the GATE pin pulled low rapidly, and the FAULT output asserted. Once a fault is latched, capacitor charging ceases (ON signal deasserted) and the timing capacitor is discharged.

In response to a latched fault condition, the TPS2393A enters a fault retry mode, wherein it periodically retries the load to test for continued existence of the fault. In this mode, the FLTTIME capacitor is discharged slowly by a about a 0.4-µA constant-current sink. When the voltage at the FLTTIME pin decays below 0.5 V, the ON signal once again enables the LCA and ramp generator circuits, and a normal turn-on current ramp ensues. Again, during the load charging, the OC signal causes charging of the FLTTIME capacitor until the next delay period elapses. The sequential charging and discharging of the FLTTIME capacitor results in a typical 1% retry duty cycle. If the current-limit fault subsides (GATE pin drives to high-level output), the timing cap is rapidly discharged (reset signal asserted), duty-cycle operation stops, and the fault latch is reset.

Note that because of the timing inhibit during the initial slow ramp period, the duty cycle in practice is slightly greater than the nominal 1% value. However, sourced current during this period peaks at only about one-eighth the maximum limit. The duty cycle of the normal ramp and constant-current periods will be about 1%.

SLUS610 - JULY 2004

**DETAILED DESCRIPTION**

Figure 24. Fault Timer Block Operation

The fault logic within the timer block automatically manages capacitor charge and discharge rates (RESET signal), and the operational status of other device-internal circuits (ON signal). The FAULT output remains asserted continuously during retry mode; it is only released if the fault condition clears.

The TPS2393A also features a fast-acting overload comparator which clamps large current transients from catastrophic faults occurring once the pass FET is fully enhanced, such as short circuits. This function provides a back-up protection to the LCA by producing a hard gate discharge action when the LCA is saturated and the pass FET is fully enhanced. If sense voltage excursions above 100 mV are detected, this comparator rapidly pulls down the GATE output, overriding the response of the LCA, and bypassing the fault timer, to terminate the short-circuit condition. Only a  $4-\mu$ s deglitch filter is applied to the OVERLOAD signal to help reduce the occurrence of nuisance trips. However, overload faults are not immediately latched in the device. Instead, once the spike has been brought down below the 100-mV threshold, the pull-down is released, returning control to the LCA. The FET is turned on again in either current ramp or current limit mode. Now, with load current once again under closed-loop control, fault timing is initiated. This permits the persistence of the fault to be assessed prior to fully interrupting the load.

Other noise events within the system can also produce large current spikes. For example, the sudden switchover in a diode-OR circuit to a supply of greater voltage potential may generate transients. Also, the temporary dropout and sudden reapplication of input power can cause a surge of current to plug-in cards. Generally, these are brief transients, and not associated with a load fault. However, the sudden inrush of current to charge the module bulk capacitance to the new supply level appears as a load fault to the hot swap controller. The TPS2393A transient response addresses this issue by providing rapid circuit-breaker protection against true load faults, along with minimal interruption of power flow during other supply noise events.

In order for downstream loads (bricks, etc.) to operate through such power bus disturbances, it is important to properly size the filtering capacitance to supply the needed energy during the OFF-time of the pass FET. Sufficient capacitance should be provided to supply the converters, at full anticipated load, for the 50 to 200  $\mu$ s period during which the FET gate is below its ON threshold. The length of the actual OFF-time is dependent on several factors, including the FET input capacitance, FET threshold voltage, and the size of the ramp capacitor.

## **APPLICATION INFORMATION**

#### Setting the Sense Resistor Value

Due to the current–limiting action of the internal LCA, the maximum allowable load current for an implementation is easily programmed by selecting the appropriate sense resistor value. The LCA acts to limit the sense voltage  $V_{I(ISENS)}$  to its internal reference. Once the voltage at the IRAMP pin exceeds approximately 4 V, this limit is the clamp voltage,  $V_{REF}$  K. Therefore, a maximum sense resistor value can be determined from equation (1).

$$R_{SENSE} \le \frac{33 \text{ mV}}{\text{IMAX}}$$

(1)

where:

- R<sub>SENSE</sub> is the resistor value

- IMAX is the desired current limit

When setting the sense resistor value, it is important to consider two factors, the minimum current that may be imposed by the TPS2393A, and the maximum load under normal operation of the module. For the first factor, the specification minimum clamp value is used, as seen in equation (1). This method accounts for the tolerance in the sourced current limit below the typical level expected (40 mV/R<sub>SENSE</sub>). (The clamp measurement includes LCA input offset voltage; therefore, this offset does not have to be factored into the current limit again.) Second, if the load current varies over a range of values under normal operating conditions, then the maximum load level must be allowed for by the value of R<sub>SENSE</sub>. One example of this is when the load is a switching converter, or brick, which draws higher input current, for a given power output, when the distribution bus is at the low end of its operating range, with decreasing draw at higher supply voltages. To avoid current-limit operation under normal loading, some margin should be designed in between this maximum anticipated load and the minimum current limit level, or IMAX > I<sub>LOAD(max</sub>), for equation (1).

For example, using a 20-m $\Omega$  sense resistor for a nominal 1-A load application provides a minimum of 650 mA of overhead for load variance/margin. Typical bulk capacitor charging current during turn-on is 2 A (40 mV/20 m $\Omega$ ).

#### Setting the Inrush Slew Rate

The TPS2393A enables user-programming of the maximum current slew rate during load start-up events. A capacitor tied to the IRAMP pin (C1 in the typical application diagram) controls the di/dt rate. Once the sense resistor value has been established, a value for ramp capacitor C<sub>IRAMP</sub>, in microfarads, can be determined from equation (2).

(2)

$$C_{IRAMP} = \frac{11}{100 \times R_{SENSE} \times \left(\frac{di}{dt}\right)_{MAX}}$$

where:

- R<sub>SENSE</sub> is the sense resistor value in Ω

- (di/dt)<sub>MAX</sub> is the desired maximum slew rate in A/s

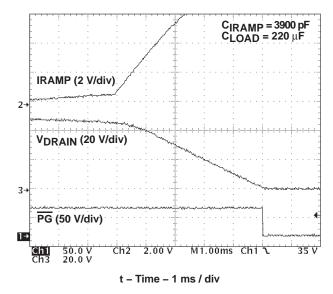

For example, if the desired slew rate for the typical application shown is 1500 mA/mS, the calculated value for  $C_{IRAMP}$  is about 3700 pF. Selecting the next larger standard value of 3900 pF (as shown in the diagram) provides some margin for capacitor and sense resistor tolerances.

As described in the Detailed Description section of this datasheet, the TPS2393A initiates ramp capacitor charging, and consequently, load current di/dt at a reduced rate. This reduced rate applies until the voltage on the IRAMP pin is about 0.5 V. The maximum di/dt rate, as set by equation (2), is effective once the device has switched to the  $10-\mu$ A charging source.

## **APPLICATION INFORMATION**

#### Setting the Fault Timing Capacitor

The fault timeout period is established by the value of the capacitor connected to the FLTTIME pin,  $C_{FLT}$ . The timeout period permits riding out spurious current glitches and surges that may occur during operation of the system, and prevents indefinite sourcing into faulted loads swapped into a live system. However, to ensure smooth voltage ramping under all conditions of load capacitance and input supply potential, the minimum timeout should be set to accommodate these system variables. To do this, a rough estimate of the maximum voltage ramp time for a completely discharged plug-in card provides a good basis for setting the minimum timer delay.

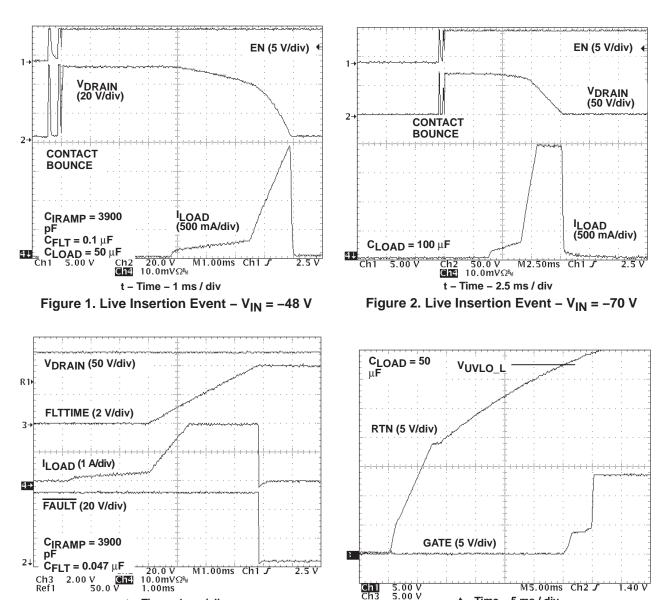

Due to the three-phase nature of the load current at turn-on, the load voltage ramp has potentially three distinct phases as seen by comparing Figure 1 and Figure 2. This profile depends on the relative values of load capacitance, input dc potential, maximum current limit and other factors. The first two phases are characterized by the two different slopes of the current ramp; the third phase, if required to complete load charging, is the constant-current charging at IMAX. Considering the two current ramp phases to be one period at an average di/dt simplifies calculation of the required timing capacitor.

For the TPS2393A, the typical duration of the soft-start ramp period, t<sub>SS</sub>, is given by equation (3).

$$t_{\rm SS} = 1183 \times C_{\rm IRAMP} \tag{3}$$

where:

- t<sub>SS</sub> is the soft-start period in milliseconds, and

- C<sub>IRAMP</sub> is given in μF

During this current ramp period, the load voltage magnitude which is attained is estimated by equation (4).

$$V_{LSS} = \frac{i_{AVG}}{2 \times C_{L} \times C_{IRAMP} \times 100 \times R_{SENSE}} \times (t_{SS})^{2}$$

(4)

where:

- V<sub>LSS</sub> is the load voltage reached during soft-start

- i<sub>AVG</sub> is 3.38 μA for the TPS2393A

- C<sub>L</sub> is the amount of the load capacitance

- t<sub>SS</sub> is the soft-start period, in seconds

The quantity  $i_{AVG}$  in equation (4) is a weighted average of the two charge currents applied to  $C_{IRAMP}$  during turn-on, considering the typical output values.

## **APPLICATION INFORMATION**

If the result of equation (4) is larger than the maximum input supply value, then the load can be expected to charge completely during the inrush slewing portion of the insertion event. However, if this voltage is less than the maximum supply input,  $V_{IN(max)}$ , the HSPM transitions to the constant-current charging of the load. The remaining amount of time required at IMAX is determined from equation (5).

$$t_{CC} = \frac{C_{L} \times \left(V_{IN(max)} - V_{LSS}\right)}{\left(\frac{V_{REF\_K(min)}}{R_{SENSE}}\right)}$$

(5)

where:

- t<sub>CC</sub> is the constant-current voltage ramp time, in seconds

- V<sub>REF K(min)</sub> is the minimum clamp voltage, 33 mV.

With this information, the minimum recommended value timing capacitor  $C_{FLT}$  can be determined. The delay time needed will be either a time  $t_{SS2}$  or the sum of  $t_{SS2}$  and  $t_{CC}$ , according to the estimated time and profiles of load charging. The quantity  $t_{SS2}$  is the duration of the normal rate current ramp period, and is given by equation (6).

$$t_{SS2} = 0.35 \times C_{RAMP}$$

(6)

where:

C<sub>RAMP</sub> is given in microfarads, and t<sub>SS2</sub> is in seconds

Since fault timing is generated by the constant-current charging of  $C_{FLT}$ , the capacitor value is determined by equation (7) or (8).

$$C_{FLT(min)} = \frac{55 \times t_{SS2}}{3.75}$$

(7)

$$C_{FLT(min)} = \frac{55 \times (t_{SS2} + t_{CC})}{3.75}$$

(8)

where:

- C<sub>FLT(min)</sub> is the recommended capacitor value, in microfarads

- t<sub>SS2</sub> is the result of equation (6), in seconds

- t<sub>CC</sub> is the result of equation (5), in seconds

For the typical application example, with the 100- $\mu$ F filter capacitor in front of the dc-to-dc converter, equations (3) and (4) estimate the load voltage ramping to -46 V during the soft-start period. If the module should operate down to -72-V input supply, approximately another 1.58 ms of constant-current charging may be required. Therefore, equations (6) and (8) (because of the constant-current sourcing) are used to determine C<sub>FLT(min)</sub>. The result of 0.043  $\mu$ F suggests the 0.047- $\mu$ F standard value.

## **APPLICATION INFORMATION**

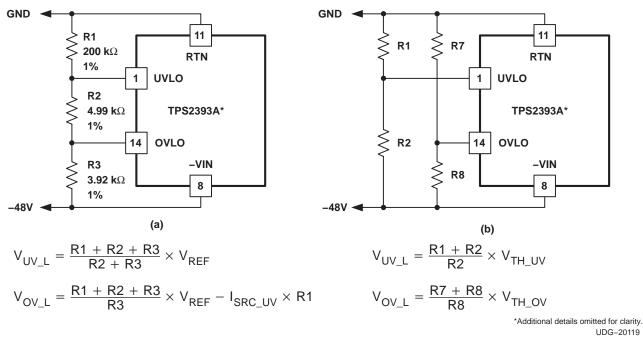

## Setting the Undervoltage and Overvoltage Thresholds

The UVLO and OVLO pins can be used to set the undervoltage ( $V_{UV}$ ) and overvoltage ( $V_{OV}$ ) thresholds of the hot swap circuit. When the input supply is below  $V_{UV}$  or above  $V_{OV}$ , the GATE pin is held low, disconnecting power from the load, and deasserting the  $\overline{PG}$  output. When input voltage is within the UV/OV window, the GATE drive is enabled, assuming all other input conditions are valid for turn-on.

Threshold hysteresis is provided via two internal sources which are switched to either pin whenever the corresponding input level exceeds the internal 1.4-V reference. The additional bias shifts the pin voltage in proportion to the external resistance connected to it. This small voltage shift at the device pin is gained up by the external divider to input supply levels.

## Figure 25. Programming the Undervoltage and Overvoltage Thresholds

The UV and OV thresholds can be individually programmed with a three-resistor divider connected to it as shown in the typical application diagram, and again in Figure 27a. When the desired trip voltages and undervoltage hysteresis have been established for the protected board, the resistor values needed can be determined from the following equations. Generally, the process is simplest by first selecting the top leg of the divider (R1 in the diagram) needed to obtain the threshold hysteresis. This value is calculated from equation (9).

$$R1 = \frac{V_{HYS\_UV}}{10 \,\mu A} \tag{9}$$

where:

V<sub>HYS UV</sub> is the undervoltage hysteresis value

#### **APPLICATION INFORMATION**

For example, assume the typical application design targets have been set to undervoltage turn-on at 33 V (input supply rising), turn-off at 31 V (input voltage falling), and overvoltage shutdown at 72 V. Then equation (9) yields  $R1 = 200 \text{ k}\Omega$  for the 2-V hysteresis. Once the value of R1 is selected, it is used to calculate resistors R2 and R3.

$$R2 = \frac{1.4 \times R1}{(V_{UV_{L}} - 1.4)} \times \left[ 1 - \frac{V_{UV_{L}}}{(V_{OV_{L}} + 10^{-5} \times R1)} \right]$$

(10)

$$R3 = \frac{1.4 \times 10^{-5} \times 10^{-5}}{\left(V_{UV_{L}} - 1.4\right) \times \left(V_{OV_{L}} + 10^{-5} \times R1\right)}$$

(11)

where:

- V<sub>UV L</sub> is the UVLO threshold when the input supply is low; i.e., less than V<sub>UV</sub>

- V<sub>OV L</sub> is the OVLO threshold when the input supply is low; .i.e., less than V<sub>OV</sub>

Again referring to the example schematic, equations (10) and (11) produce R2 =  $4.909 \text{ k}\Omega$  ( $4.99 \text{ k}\Omega$  selected) and R3 =  $3.951 \text{ k}\Omega$  ( $3.92 \text{ k}\Omega$  selected), as shown. For the selected resistor values, the expected nominal supply thresholds are as shown on the typical application diagram. The hysteresis on the overvoltage threshold, as seen at the supply inputs, is given by the quantity ( $10 \mu A$ ) \* (R1 + R2). For the majority of applications, this value will be very nearly the same as the UV hysteresis, since typically R1 >> R2.

If more independent control is needed for the OVLO hysteresis, there are several options. One option is to use separate dividers for both the UVLO and OVLO pins, as shown in Figure 27b. In this case, once R1 and R7 have been selected for the required hysteresis per equation (9), the bottom resistors in the dividers (R2 and R8 in Figure 27b) can be found from equation (12).

$$R_{XVLO} = \frac{V_{REF}}{\left(V_{XV_L} - V_{REF}\right)} \times R_{TOP}$$

(12)

where:

- R<sub>XVLO</sub> is R2 or R8

- R<sub>TOP</sub> is R1 or R7 as appropriate for the threshold being set

- V<sub>XV\_L</sub> is the under (V<sub>UV\_L</sub>) or overvoltage (V<sub>OV\_L</sub>) threshold at the supply input

- V<sub>REF</sub> is either V<sub>TH\_UV</sub> or V<sub>TH\_OV</sub> from the specification table, as required for the resistor being calculated

#### Capacitor on UVLO Pin

As shown in the typical application diagram, a minimum 1500 pF capacitor is required on the UVLO pin of the TPS2393A. For some systems, it may be desirable to slow down the response of the controller to undervoltage conditions. For example, if frequent voltage dips are anticipated due to other power events in the system, it may be beneficial to delay somewhat the response of the detection circuit. For these situations, the size of the capacitor can be increased accordingly, over the value shown.

## **APPLICATION INFORMATION**

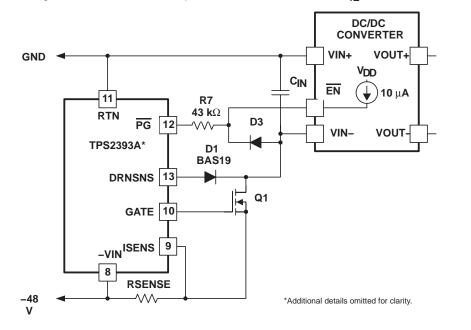

### Using the PG Output

The  $\overline{PG}$  output is an indication of the load power status.  $\overline{PG}$  is asserted after a load turn-on, once the load voltage has ramped up to the input dc level, as indicated by a small V<sub>DS</sub> drop across the pass FET. The load voltage is sensed by the DRAINSNS pin, which is connected to the pass FET drain through a small-signal blocking diode. Also, the TPS2393A first confirms that the full programmed sourcing current (typically 40 mV/R<sub>SENSE</sub>) is available to the load electronics prior to declaring power good. The  $\overline{PG}$  status is latched once the power conditions are met, so that momentary current limiting operation due to input supply transients is not reflected in this output status. This pin can be used to enable downstream converters, provide a visual indication of load power good, or be level-translated or optocoupled to provide status reporting back to the host controller.

When using  $\overline{PG}$  to drive the enable input of a converter, care should be taken not to exceed the manufacturer's maximum voltage ratings for the pin. When asserted, the output driver pulls the  $\overline{PG}$  pin to the –VIN pin potential. Because this status in latched, subsequent current limit operation of the circuit could result in pulling the enable input below the brick's VIN– potential during the fault timeout period. If the brick does not provide an internal clamp on this pin, a diode can be connected as shown in Figure 28 to externally limit the swing below VIN–. In either case, a resistor (R7 in Figure 28) should be used to limit the current pulled from this pin, protecting both the converter and the  $\overline{PG}$  output. R7 should be large enough to limit the  $\overline{PG}$  input current to less than 10 mA, while still allowing the brick enable to be pulled below its maximum V<sub>II</sub> threshold.

Figure 26. TPS2393A Active-Low Converter Enable

UDG-20177

## **APPLICATION INFORMATION**

If the selected converter cannot tolerate any voltage excursions below VIN– potential, an alternative is to drive the enable through an optocoupler. An implementation is shown in Figure 29.

Figure 27. PG Driving An Optocoupler

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  | . ,           |              |                    |      |                |                 | (6)                           | .,                 |              |                         |         |

| TPS2393APW       | ACTIVE        | TSSOP        | PW                 | 14   | 90             | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TPS2393A                | Samples |

| TPS2393APWR      | ACTIVE        | TSSOP        | PW                 | 14   | 2000           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TPS2393A                | Samples |

| TPS2393APWRG4    | ACTIVE        | TSSOP        | PW                 | 14   | 2000           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TPS2393A                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

www.ti.com

## PACKAGE OPTION ADDENDUM

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

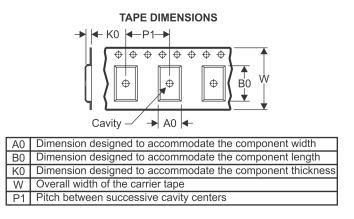

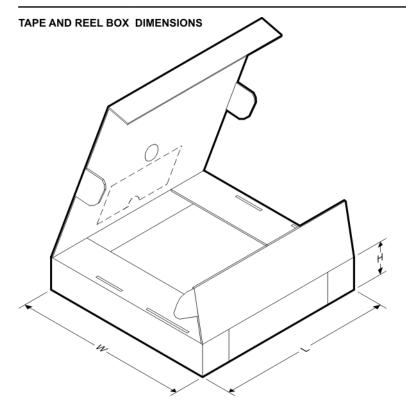

### TAPE AND REEL INFORMATION

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions | are | nominal |

|-----------------|-----|---------|

|-----------------|-----|---------|

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2393APWR | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

5-Jan-2022

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2393APWR | TSSOP        | PW              | 14   | 2000 | 853.0       | 449.0      | 35.0        |

www.ti.com

5-Jan-2022

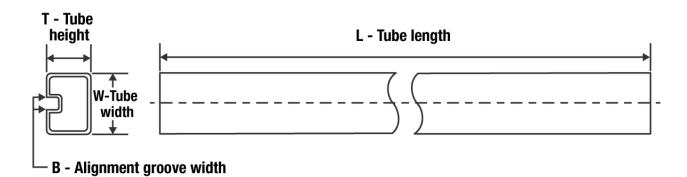

## TUBE

#### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS2393APW | PW           | TSSOP        | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

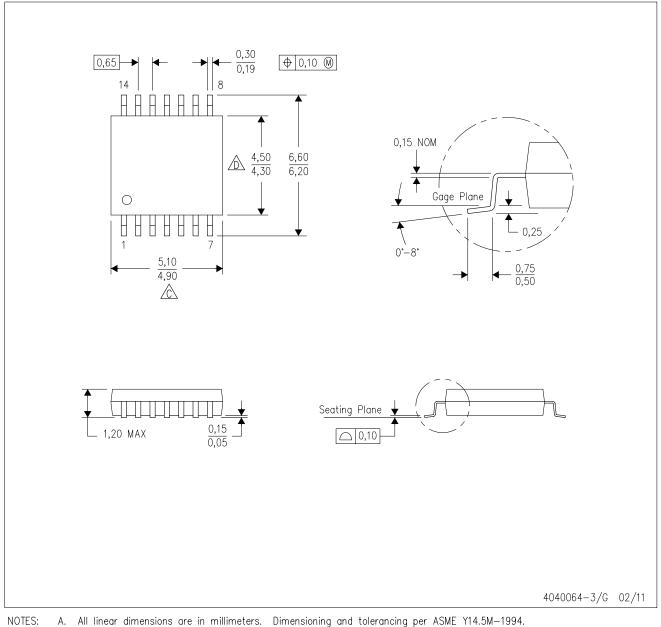

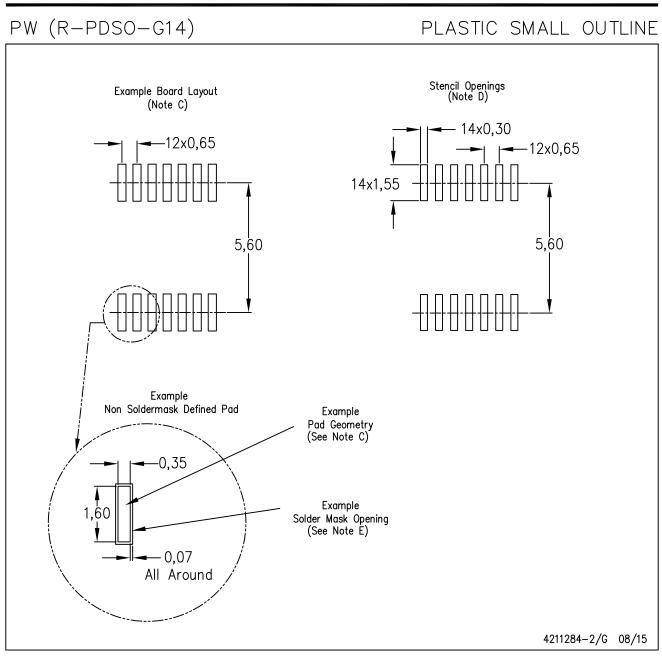

PW (R-PDSO-G14)

PLASTIC SMALL OUTLINE

A. An integration of the information o

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

E. Falls within JEDEC MO-153

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated