# 2A Dual Channel Synchronous Step-Down Switcher with Integrated FET

Check for Samples: TPS54294

#### **FEATURES**

- D-CAP2™ Control Mode

- Fast Transient Response

- No External Parts Required For Loop Compensation

- Compatible with Ceramic Output Capacitors

- Wide Input Voltage Range: 4.5 V to 18 V

- Output Voltage Range: 0.76V to 7.0V

- Highly Efficient Integrated FETs Optimized for Low Duty Cycle Applications

- 150 mΩ (High Side) and 100 mΩ (Low Side)

- High Initial Reference Accuracy

- Low-Side r<sub>DS(on)</sub> Loss-Less Current Sensing

- Fixed Soft Start : 1.0ms

- Non-Sinking Pre-Biased Soft Start

- Powergood

- 700 kHz Switching Frequency

- Cycle-by-Cycle Over-Current Limit Control

- OCL/OVP/UVP/UVLO/TSD Protections

- Adaptive Gate Drivers with Integrated Boost PMOS Switch

- OCP Constant Due To Thermally Compensated r<sub>DS(on)</sub> with 4000ppm/°C

- 16-Pin HTSSOP, 16-Pin VQFN

- Auto-Skip Eco-mode<sup>™</sup> for High Efficiency at Light Load

#### **APPLICATIONS**

- Point-of-Load Regulation in Low Power Systems for Wide Range of Applications

- Digital TV Power Supply

- Networking Home Terminal

- Digital Set Top Box (STB)

- DVD Player/Recorder

- Gaming Consoles and Other

#### DESCRIPTION

The TPS54294 is a dual, adaptive on-time D-CAP2™ mode synchronous buck converter. The TPS54294 enables system designers to complete the suite of various end equipment's power bus regulators with a cost effective, low component count, and low standby current solution. The main control loops of the TPS54294 use the D-CAP2™ mode control which provides a very fast transient response with no external compensation components. The adaptive ontime control supports seamless transition between PWM mode at higher load conditions and Ecomode<sup>™</sup> operation at light loads. Eco-mode<sup>™</sup> allows the TPS54294 to maintain high efficiency during lighter load conditions. The TPS54294 is able to adapt to both low equivalent series resistance (ESR) output capacitors such as POSCAP or SP-CAP, and ultra-low ESR, ceramic capacitors. The device provides convenient and efficient operation with input voltages from 4.5V to 18V.

The TPS54294 is available in a 4.4mm × 5.0mm 16-pin TSSOP (PWP) package, and 4mm x 4mm 16-pin VQFN (RSA) package specified for an ambient temperature range from -40°C to 85°C.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

D-CAP2, Eco-mode, Eco-Mode, SWIFT are trademarks of Texas Instruments.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE | ORDERING PART NUMBER | PINS | OUTPUT SUPPLY |  |

|----------------|---------|----------------------|------|---------------|--|

|                | DWD     | TPS54294PWPR         | 40   | Tape-and-Reel |  |

| 40°C to 05°C   | PWP     | TPS54294PWP          | 16   | Tube          |  |

| –40°C to 85°C  | DCA     | TPS54294RSAR         | 16   | Tone and Deal |  |

|                | RSA     | TPS54294RSAT         | 16   | Tape-and-Reel |  |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                  |                          |                               | VALUE       | UNIT |  |  |

|------------------|--------------------------|-------------------------------|-------------|------|--|--|

|                  |                          | VIN1, VIN2, EN1, EN2          | -0.3 to 20  |      |  |  |

|                  |                          | VBST1, VBST2                  | -0.3 to 26  |      |  |  |

|                  |                          | VBST1, VBST2 (10ns transient) | -0.3 to 28  |      |  |  |

|                  | Input voltage range      | VBST1-SW1 , VBST2-SW2         | -0.3 to 6.5 | V    |  |  |

|                  |                          | VFB1, VFB2                    | -0.3 to 6.5 |      |  |  |

|                  |                          | SW1, SW2                      | -2 to 20    | ı    |  |  |

|                  |                          | SW1, SW2 (10ns transient)     | -3 to 22    |      |  |  |

|                  | Output welters were      | VREG5, PG1, PG2               | -0.3 to 6.5 | .,   |  |  |

|                  | Output voltage range     | PGND1, PGND2                  | -0.3 to 0.3 | V    |  |  |

|                  |                          | Human Body Model (HBM)        | 2           | kV   |  |  |

|                  | Electrostatic discharge  | Charged Device Model (CDM)    | 500         | V    |  |  |

| T <sub>A</sub>   | Operating ambient temper | erature range                 | -40 to 85   | °C   |  |  |

| T <sub>STG</sub> | Storage temperature ran  | ge                            | -55 to 150  | °C   |  |  |

| TJ               | Junction temperature ran | ge                            | -40 to 150  | °C   |  |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                  | THERMAL METRIC <sup>(1)</sup>                | TPS54         | LINUTO        |       |

|------------------|----------------------------------------------|---------------|---------------|-------|

|                  | THERMAL METRIC                               | PWP (16) PINS | RSA (16) PINS | UNITS |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 47.5          | 34.9          |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 27.1          | 40.0          |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 20.8          | 11.8          | 90044 |

| $\Psi_{JT}$      | Junction-to-top characterization parameter   | 1.0           | 0.7           | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter | 20.6          | 11.8          |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.7           | 3.3           |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> All voltages are with respect to IC GND terminal.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                              |                               | VALU | IES      |      |

|------------------------------|-------------------------------|------|----------|------|

|                              |                               | MIN  | MAX      | UNIT |

| Supply input voltage range   | VIN1, VIN2                    | 4.5  | 18       | V    |

|                              | VBST1, VBST2                  | -0.1 | 24       |      |

|                              | VBST1, VBST2 (10ns transient) | -0.1 | 27       |      |

|                              | VBST1-SW1, VBST2-SW2          | -0.1 | 5.7      |      |

| Input voltage range          | VFB1, VFB2                    | -0.1 | -0.1 5.7 |      |

|                              | EN1, EN2                      | -0.1 | 18       |      |

|                              | SW1, SW2                      | -1.0 | 18       |      |

|                              | SW1, SW2 (10ns transient)     | -3   | 21       |      |

|                              | VREG5, PG1 , PG2              | -0.1 | 5.7      |      |

| Output voltage range         | PGND1, PGND2                  | -0.1 | 0.1      | V    |

|                              | VO1, VO2                      | 0.76 | 7.0      |      |

| Operating free-air temperatu | re                            | -40  | 85       | °C   |

| Operating Junction Tempera   | ture                          | -40  | 150      | °C   |

### **ELECTRICAL CHARACTERISTICS**(1)

over recommended free-air temperature range, VIN = 12 V (unless otherwise noted)

|                      | PARAMETER                      | CONDITIONS                                     | MIN   | TYP  | MAX  | UNIT   |

|----------------------|--------------------------------|------------------------------------------------|-------|------|------|--------|

| SUPPLY C             | URRENT                         |                                                | ,     |      | ,    |        |

| I <sub>IN</sub>      | VIN supply current             | EN1 = EN2 = 5 V,<br>VFB1 = VFB2 = 0.8 V        |       | 1300 | 2500 | μA     |

| I <sub>VINSDN</sub>  | VIN shutdown current           | EN1 = EN2 = 0 V                                |       | 80   | 200  | μΑ     |

| FEEDBACK             | ( VOLTAGE                      |                                                |       |      |      |        |

| V <sub>VFBTHLx</sub> | VFBx threshold voltage         | CH1 = 3.3 V, CH2 = 1.5 V                       | 758   | 765  | 773  | mV     |

| TC <sub>VFBx</sub>   | Temperature coefficient        | On the basis of 25°C <sup>(2)</sup>            | -115  |      | 115  | ppm/°C |

| I <sub>VFBx</sub>    | VFB Input Current              | VFBx = 0.8 V                                   | -0.35 | 0.2  | 0.35 | μΑ     |

| VREG5 OU             | TPUT                           |                                                |       |      |      |        |

| V <sub>VREG5</sub>   | VREG5 output voltage           | 6 V < VIN1 < 18 V,<br>I <sub>VREG</sub> = 5 mA |       | 5.5  |      | V      |

| I <sub>VREG5</sub>   | Output current                 | VIN1 = 6 V, VREG5 = 4 V <sup>(2)</sup>         |       | 75   |      | mA     |

| MOSFETs              |                                | •                                              |       |      | •    |        |

| r <sub>DS(on)H</sub> | High side switch resistance    | VBSTx-SWx = 5.5 V (2)                          |       | 150  |      | mΩ     |

| r <sub>DS(on)L</sub> | Low side switch resistance (2) |                                                |       | 100  |      | mΩ     |

| ON-TIME T            | IMER CONTROL                   |                                                |       |      |      |        |

| T <sub>ON1</sub>     | SW1 On Time                    | SW1 = 12 V, VO1 = 1.2 V                        |       | 165  |      | ns     |

| T <sub>ON2</sub>     | SW2 On Time                    | SW2 = 12 V, VO2 = 1.2 V                        |       | 165  |      | ns     |

| T <sub>OFF1</sub>    | SW1 Min off time               | VFB1 = 0.7 V <sup>(2)</sup>                    |       | 220  |      | ns     |

| T <sub>OFF2</sub>    | SW2 Min off time               | VFB2 = 0.7 V <sup>(2)</sup>                    |       | 220  |      | ns     |

| SOFT STAF            | RT                             |                                                |       |      |      |        |

| T <sub>SS</sub>      | Soft-start time                | Internal soft-start time                       |       | 1.0  |      | ms     |

<sup>(1)</sup> x means either 1 or 2, that is, VFBx means VFB1 or VFB2.

<sup>(2)</sup> Specified by design. Not production tested.

## **ELECTRICAL CHARACTERISTICS (continued)**

over recommended free-air temperature range, VIN = 12 V (unless otherwise noted)

|                       | PARAMETER                                   | CONDITIONS                     | MIN  | TYP  | MAX  | UNIT |

|-----------------------|---------------------------------------------|--------------------------------|------|------|------|------|

| POWER GO              | OD                                          |                                | "    |      | 1    |      |

| \/                    | DCv throobold                               | PG from lower VOx (going high) |      | 84%  |      |      |

| $V_{PGTH}$            | PGx threshold                               | PG from higher VOx (going low) |      | 116% |      |      |

| R <sub>PG</sub>       | PGx pull-down resistance                    | VPGx = 0.5 V                   | 50   | 75   | 110  | Ω    |

| <b>-</b>              | DC: dalar time                              | Delay for PGx going high       |      | 1.5  |      | ms   |

| T <sub>PGDLY</sub>    | PGx delay time                              | Delay for PGx going low        |      | 2    |      | μs   |

| T <sub>PGCOMPSS</sub> | PGx comparator start-up delay               | PGx comparator wake-up delay   |      | 1.5  |      | ms   |

| UVLO                  |                                             |                                | •    |      |      |      |

| \/                    | VDECE IIVI O three hold                     | VREG5 rising                   |      | 3.83 |      | V    |

| $V_{UVREG5}$          | VREG5 UVLO threshold                        | Hysteresis                     |      | 0.6  |      | V    |

| LOGIC THRI            | ESHOLDs                                     |                                |      |      | •    |      |

| V <sub>ENH</sub>      | ENx H-level threshold voltage               |                                | 2.0  |      |      | V    |

| V <sub>ENL</sub>      | ENx L-level threshold voltage               |                                |      |      | 0.4  | V    |

| R <sub>ENx_IN</sub>   | ENx input resistance                        | ENx = 12 V                     | 225  | 450  | 900  | kΩ   |

| CURRENT L             | IMITs                                       |                                |      |      |      |      |

| I <sub>OCL</sub>      | Current limit                               | $L_{OUT} = 2.2  \mu H^{(3)}$   | 2.7  | 3.9  | 4.5  | Α    |

| OUTPUT UN             | DERVOLTAGE AND OVERVOLTAGE                  | PROTECTION (UVP, OVP)          |      |      |      |      |

| V <sub>OVP</sub>      | Output OVP trip threshold                   | measured on VFBx               | 115% | 120% | 125% |      |

| T <sub>OVPDEL</sub>   | Output OVP prop delay                       |                                |      | 3    | 10   | μs   |

| V <sub>UVP</sub>      | Output UVP trip threshold                   | measured on VFBx               | 63%  | 68%  | 73%  |      |

| T <sub>UVPDEL</sub>   | Output UVP delay time                       |                                |      | 1.5  |      | ms   |

| T <sub>UVPEN</sub>    | Output UVP enable delay                     |                                |      | 1.5  |      | ms   |

| THERMAL S             | HUTDOWN                                     |                                |      |      |      |      |

| <b>-</b>              | The arrest of the state of the state of the | Shutdown temperature (3)       |      | 155  |      |      |

| $T_{SD}$              | Thermal shutdown threshold                  | Hysteresis (3)                 |      | 25   |      | °C   |

<sup>(3)</sup> Specified by design. Not production tested.

Submit Documentation Feedback

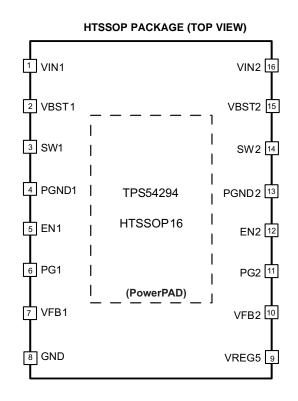

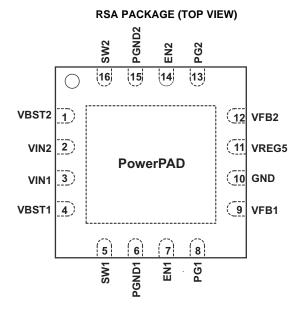

#### **DEVICE INFORMATION**

#### PIN FUNCTIONS(1)

|                        | PIN       |             | I/O | DESCRIPTION                                                                                                                                                            |

|------------------------|-----------|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NUN       | <b>MBER</b> |     |                                                                                                                                                                        |

|                        | PWP       | RSA         |     |                                                                                                                                                                        |

| VIN1, VIN2             | 1, 16     | 3, 2        | I   | Power inputs and connects to both high side NFET drains. Supply Input for 5.5V linear regulator.                                                                       |

| VBST1, VBST2           | 2, 15     | 4, 1        | I   | Supply input for high-side NFET gate drive circuit. Connect 0.1µF ceramic capacitor between VBSTx and SWx pins. An internal diode is connected between VREG5 and VBSTx |

| SW1, SW2               | 3, 14     | 5, 16       | I/O | Switch node connections for both the high-side NFETs and low–side NFETs. Input of current comparator.                                                                  |

| PGND1, PGND2           | 4, 13     | 6, 15       | I/O | Ground returns for low-side MOSFETs. Input of current comparator.                                                                                                      |

| EN1, EN2               | 5, 12     | 7, 14       | I   | Enable. Pull High to enable according converter.                                                                                                                       |

| PG1, PG2               | 6, 11     | 8, 13       | 0   | Open drain power good output. Low means the output voltage of the corresponding output is out of regulation.                                                           |

| VFB1, VFB2             | 7, 10     | 9, 12       | ı   | D-CAP2 feedback inputs. Connect to output voltage with resistor divider.                                                                                               |

| GND                    | 8         | 10          | I/O | Signal GND. Connect sensitive SSx and VFBx returens to GND at a single point.                                                                                          |

| VREG5                  | 9         | 11          | 0   | Output of 5.5V linear regulator. Bypass to GND with a high-quality ceramic capacitor of at least 1.0 $\mu$ F. VREG5 is active when VIN1 is added .                     |

| Exposed Thermal<br>Pad | Back side | Back side   | I/O | Thermal pad of the package. Must be soldered to achieve appropriate dissipation. Must be connected to GND.                                                             |

(1) x means either 1 or 2, e.g. VFBx means VFB1 or VFB2.

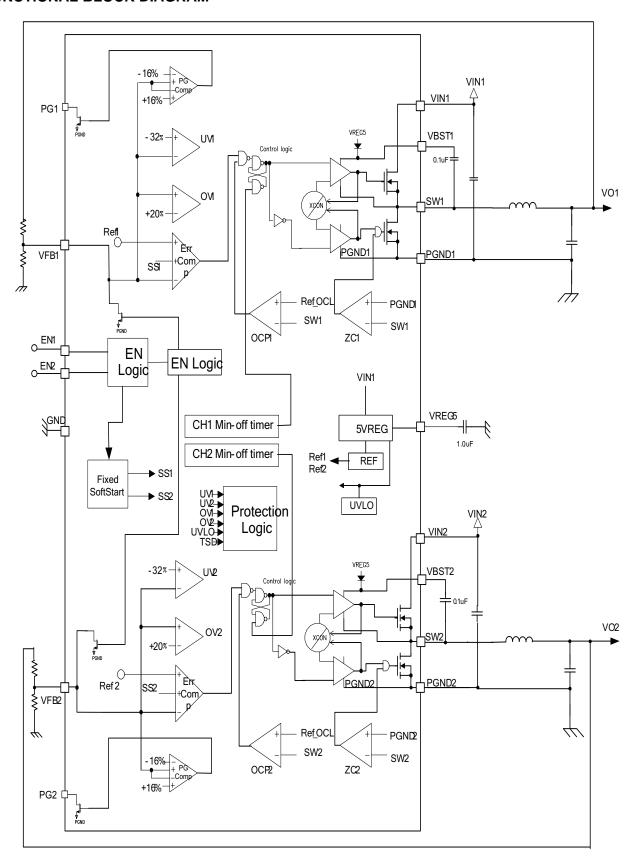

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **OVERVIEW**

The TPS54294 is a 2A/2A dual synchronous step-down (buck) converter with two integrated N-channel MOSFETs for each channel. It operates using D-CAP2™ control mode. The fast transient response of D-CAP2™ control reduces the required output capacitance to meet a specific level of performance. Proprietary internal circuitry allows the use of low ESR output capacitors including ceramic and special polymer types.

#### **DETAILED DESCRIPTION**

#### **PWM Operation**

The main control loop of the TPS54294 is an adaptive on-time pulse width modulation (PWM) controller that supports a proprietary D-CAP2™ control mode. D-CAP2™ control combines constant on-time control with an internal compensation circuit for pseudo-fixed frequency and low external component count configuration with both low ESR and ceramic output capacitors. It is stable even with virtually no ripple at the output.

At the beginning of each cycle, the high-side MOSFET is turned on. This MOSFET is turned off when the internal timer expires. This timer is set by the converter's input voltage, VINx, and the output voltage, VOx, to maintain a pseudo-fixed frequency over the input voltage range hence it is called adaptive on-time control. The timer is reset and the high-side MOSFET is turned on again when the feedback voltage falls below the nominal output voltage. An internal ramp is added to the reference voltage to simulate output voltage ripple, eliminating the need for ESR induced output ripple from D-CAP<sup>TM</sup> control.

#### **PWM Frequency and Adaptive On-Time Control**

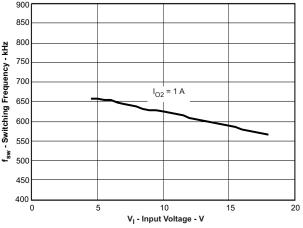

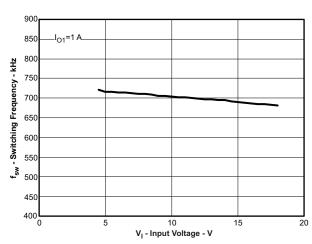

TPS54294 uses an adaptive on-time control scheme and does not have a dedicated on board oscillator. The TPS54294 runs with a pseudo-fixed frequency of 700 kHz by using the input voltage and output voltage to set the on-time timer. The on-time is inversely proportional to the input voltage and proportional to the output voltage, therefore, when the duty ratio is VOx/VINx, the frequency is constant.

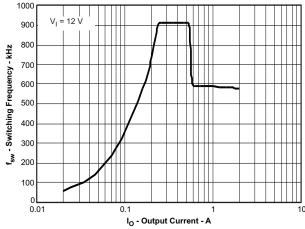

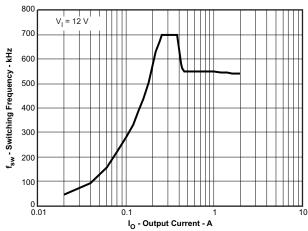

#### Auto-Skip Eco-Mode™ Control

The TPS54294 is designed with Auto-Skip Eco-mode<sup>TM</sup> to increase light load efficiency. As the output current decreases from heavy load condition, the inductor current also reduces and eventually comes to the point where its ripple valley touches the zero level, which is the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET is turned off when zero inductor current is detected. As the load current further decreases the converter runs into discontinuous conduction mode. The on-time is kept almost half as it was in the continuous conduction mode because it takes longer to discharge the output capacitor with smaller load current to the nominal output voltage. The transition point to the light load operation  $I_{Ox(LL)}$  current can be estimated with Equation 1with 700-kHz used as  $f_{SW}$ .

$$I_{Ox(LL)} = \frac{1}{2 \times L1x \times f_{SW}} \times \frac{\left(V_{INx} - V_{Ox}\right) \times V_{Ox}}{V_{INx}}$$

(1)

#### Soft Start and Pre-Biased Soft Start

The TPS54294 has an internal, 1.0ms, soft-start for each channel. When the ENx pin becomes high, an internal DAC begins ramping up the reference voltage to the PWM comparator. Smooth control of the output voltage is maintained during start up.

The TPS54294 contains a unique circuit to prevent current from being pulled from the output during startup if the output is pre-biased. When the soft-start commands a voltage higher than the pre-bias level (internal soft start becomes greater than internal feedback voltage, VFBx), the controller slowly activates synchronous rectification by starting the first low side FET gate driver pulses with a narrow on-time. It then increments that on-time on a cycle-by-cycle basis until it coincides with the time dictated by (1-D), where D is the duty cycle of the converter. This scheme prevents the initial sinking of the pre-biased output, and ensures that the output voltage (VOx) starts and ramps up smoothly into regulation from pre-biased startup to normal mode operation.

#### **POWERGOOD**

The TPS54294 has power-good outputs that are measured on VFBx. The power-good function is activated after the soft-start has finished. If the output voltage is within 16% of the target voltage, the internal comparator detects the power good state and the power good signal becomes high after 1.5ms delay. During start-up, this internal delay starts after 1.5ms of the UVP Enable delay time to avoid a glitch of the power-good signal. If the feedback voltage goes outside of ±16% of the target value, the power-good signal becomes low after 2µs.

#### **Over-Current Protection**

he output over-current protection (OCP) is implemented using a cycle-by-cycle valley detection control circuit. The switch current is monitored by measuring the low-side FET switch voltage between the SWx and PGNDx pins. This voltage is proportional to the switch current and the on-resistance of the FET. To improve the measurement accuracy, the voltage sensing is temperature compensated.

During the on-time of the high-side FET switch, the switch current increases at a linear rate determined by VINx, VOx, the on-time and the output inductor value. During the on-time of the low-side FET switch, this current decreases linearly. The average value of the switch current is the load current I<sub>OUTx</sub>. If the sensed voltage on the low-side FET is above the voltage proportional to the current limit, the converter keeps the low-side switch on until the measured voltage falls below the voltage corresponding to the current limit and a new switching cycle begins. In subsequent switching cycles, the on-time is set to the value determined for CCM and the current is monitored in the same manner.

Following are some important considerations for this type of over-current protection. The load current is one half of the peak-to-peak inductor current higher than the over-current threshold. Also when the current is being limited, the output voltage tends to fall as the demanded load current may be higher than the current available from the converter. When the over current condition is removed, the output voltage returns to the regulated value. This protection is non-latching.

#### **Over/Under Voltage Protection**

TPS54294 monitors the resistor divided feedback voltage to detect over and under voltage. If the feedback voltage is higher than 120% of the reference voltage, the OVP comparator output goes high and the circuit latches both the high-side MOSFET driver and the low-side MOSFET driver off. When the feedback voltage is lower than 68% of the reference voltage, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 1.5ms, TPS54294 latches OFF both the high-side MOSFET and the low-side MOSFET drivers. This function is enabled approximately 1.7 times the softstart time after power-on. The OVP and UVP latch off is reset when EN is toggled.

#### **UVLO Protection**

Under-voltage lock out protection (UVLO) monitors the voltage of the  $V_{REG5}$  pin. When the  $V_{REG5}$  voltage is lower than the UVLO threshold, the TPS54294 shuts down. As soon as the voltage increases above the UVLO threshold, the converter starts again.

#### **Thermal Shutdown**

TPS54294 monitors its temperature. If the temperature exceeds the threshold value (typically 155°C), the device shuts down. When the temperature falls below the threshold, the IC starts again.

When VIN1 starts up and VREG5 output voltage is below its nominal value, the thermal shutdown threshold is lower than 155°C. As long as VIN1 rises, T<sub>J</sub> must be kept below 110°C.

Product Folder Links: TPS54294

Copyright © 2011-2013, Texas Instruments Incorporated

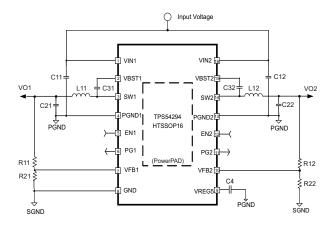

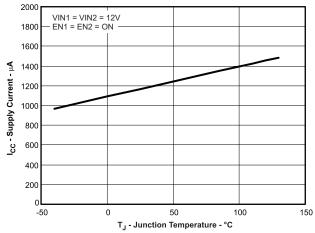

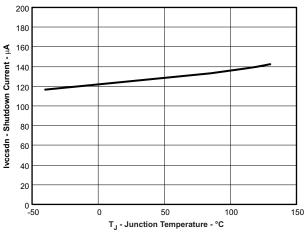

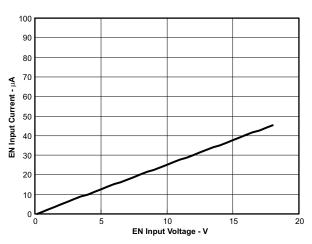

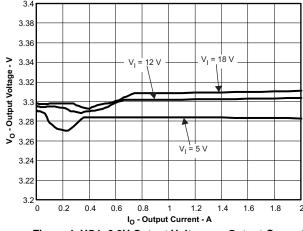

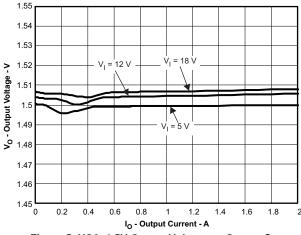

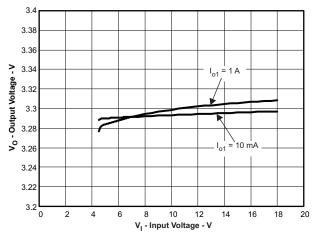

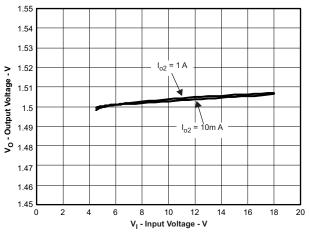

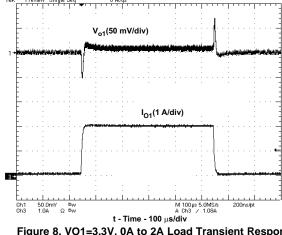

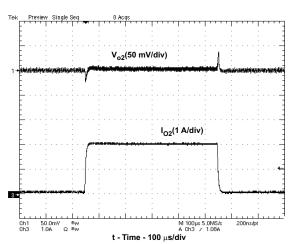

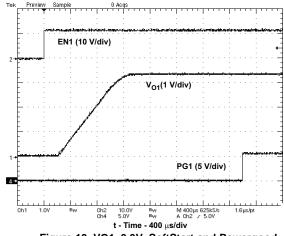

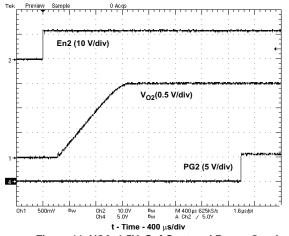

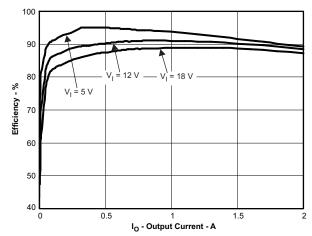

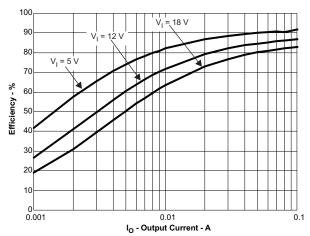

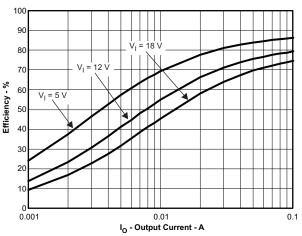

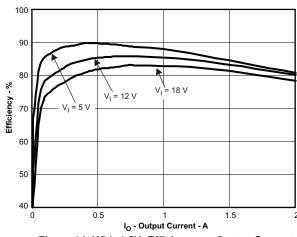

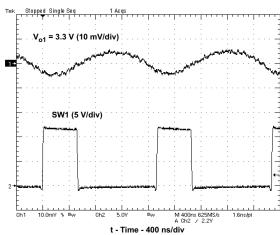

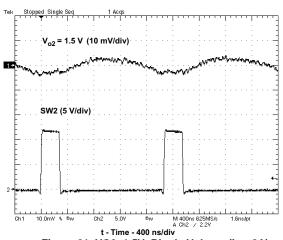

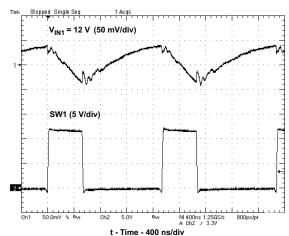

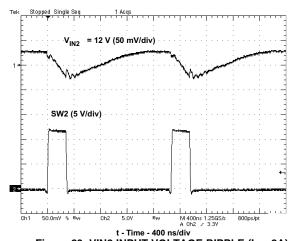

One output is enabled unless otherwise noted. VI = VIN1 or VIN2. VIN = 12 V,  $T_A$  = 25°C (unless otherwise noted).

Figure 1. Input Current vs Junction Temperature

Figure 2. Input Shutdown Current vs Junction Temperature

Figure 3. EN Current vs EN Voltage (VEN=12V)

Figure 4. VO1=3.3V Output Voltage vs Output Current

Figure 5. VO2=1.5V Output Voltage vs Output Current

Figure 6. VO1=3.3V Output Voltage vs Input Voltage

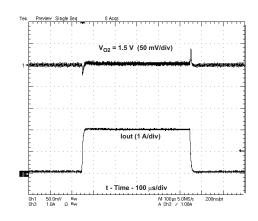

One output is enabled unless otherwise noted. VI = VIN1 or VIN2. VIN = 12 V,  $T_A = 25$ °C (unless otherwise noted).

Figure 7. VO2=1.5V Output Voltage vs Input Voltage

Figure 8. VO1=3.3V, 0A to 2A Load Transient Response

Figure 9. VO2=1.5V, 0A to 2A Load Transient Response

Figure 10. VO1=3.3V, SoftStart and Powergood

Figure 11. VO2=1.5V, SoftStart and Power Good

Figure 12. VO1=3.3V, Efficiency vs Output Current

Submit Documentation Feedback

One output is enabled unless otherwise noted. VI = VIN1 or VIN2. VIN = 12 V,  $T_A$  = 25°C (unless otherwise noted).

Figure 13. VO1=3.3V, Efficiency vs Output Current

Figure 15. VO2=1.5V, Efficiency vs Output Current

Figure 17. VO2=1.5V, SW-frequency vs Input Voltage

Figure 14. VO1=1.5V, Efficiency vs Output Current

Figure 16. VO1=3.3V, SW-frequency vs Input Voltage

Figure 18. VO1=3.3V, SW-frequency vs Output Current

One output is enabled unless otherwise noted. VI = VIN1 or VIN2. VIN = 12 V,  $T_A$  = 25°C (unless otherwise noted).

Figure 19. VO2=1.5V, SW-frequency vs Output Current

Figure 20. VO1=3.3V, VO1 Ripple Voltage (I<sub>O1</sub>=2A)

Figure 21. VO2=1.5V, Ripple Voltage (I<sub>O2</sub>=2A)

Figure 22. VIN1 Input Voltage Ripple (I<sub>O1</sub>=2A)

Figure 23. VIN2 INPUT VOLTAGE RIPPLE (I<sub>O2</sub>=2A)

Product Folder Links: TPS54294

Submit Documentation Feedback

#### **DESIGN GUIDE**

#### **Step By Step Design Procedure**

To begin the design process, you must know a few application parameters:

- Input voltage range

- Output voltage

- Output current

In all formulas x is used to indicate that they are valid for both converters. For the calculations the estimated switching frequency of 700 kHz is used.

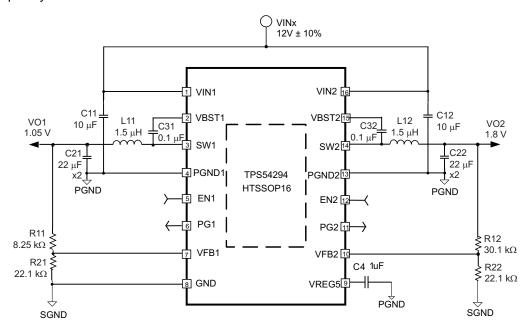

Figure 24. Schematic Diagram for the Design Example

### **Output Voltage Resistors Selection**

The output voltage is set with a resistor divider from the output node to the VFBx pin. It is recommended to use 1% tolerance or better divider resistors. Start by using Equation 2 to calculate  $V_{Ox}$ .

To improve the efficiency at very light loads consider using larger value resistors, but too high resistance values will be more susceptible to noise and voltage errors due to the VFBx input current will be more noticeable.

$$V_{Ox} = 0.765 \text{ V} \times \left(1 + \frac{R1x}{R2x}\right)$$

(2)

#### **Output Filter Selection**

The output filter used with the TPS54294 is an LC circuit. This LC filter has double pole at:

$$F_{\rm P} = \frac{1}{2\pi \sqrt{L_{\rm OUT} \times C_{\rm OUT}}} \tag{3}$$

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal gain of the TPS545294. The low frequency phase is 180 degrees. At the output filter pole frequency, the gain rolls off at a −40 dB per decade rate and the phase drops rapidly. D-CAP2™ introduces a high frequency zero that reduces the gain roll off to −20 dB per decade and increases the phase to 90 degrees one decade above the zero frequency. The inductor and capacitor selected for the output filter must be selected so that the double pole of Equation 3 is located below the high frequency zero but close enough that the phase boost provided by the high frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the values recommended in Table 1.

Table 1. Recommended Component Values

| OUTPUT VOLTAGE (V) | R1x (kΩ) | R2x (kΩ) | Cffx (pF) | L1x (µH) | C2x (µF) |

|--------------------|----------|----------|-----------|----------|----------|

| 1                  | 6.81     | 22.1     |           | 1.0-1.5  | 22 - 68  |

| 1.05               | 8.25     | 22.1     |           | 1.0-1.5  | 22 - 68  |

| 1.2                | 12.7     | 22.1     |           | 1.0-1.5  | 22 - 68  |

| 1.5                | 21.5     | 22.1     |           | 1.5      | 22 - 68  |

| 1.8                | 30.1     | 22.1     | 5 - 22    | 1.5      | 22 - 68  |

| 2.5                | 49.9     | 22.1     | 5 - 22    | 2.2      | 22 - 68  |

| 3.3                | 73.2     | 22.1     | 5 - 22    | 2.2      | 22 - 68  |

| 5                  | 124      | 22.1     | 5 - 22    | 3.3      | 22 - 68  |

For higher output voltages at or above 1.8 V, additional phase boost can be achieved by adding a feed forward capacitor (Cff) in parallel with R1.

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 4, Equation 5 and Equation 6. The inductor saturation current rating must be greater than the calculated peak current and the RMS or heating current rating must be greater than the calculated RMS current.

For the calculations, use 700 kHz as the switching frequency, f<sub>SW</sub>. Make sure the chosen inductor is rated for the peak current of Equation 5 and the RMS current of Equation 6.

$$\Delta I_{L1x} = \frac{V_{Ox}}{V_{INx(MAX)}} \times \frac{V_{INx(MAX)} - V_{Ox}}{L1x \times f_{SW}}$$

(4)

$$I_{Lpeakx} = I_{Ox} + \frac{\Delta I_L}{2} \tag{5}$$

$$I_{LOx(RMS)} = \sqrt{I_{Ox}^2 + \frac{1}{12}\Delta I_L^2}$$

(6)

For the above design example, the calculated peak current is 2.46 A and the calculated RMS current is 2.02 A for VO1. The inductor used is a TDK CLF7045-1R5N with a rated current of 7.3A based on the inductance change and of 4.9A based on the temperature rise.

The capacitor value and ESR determines the amount of output voltage ripple. The TPS54294 is intended for use with ceramic or other low ESR capacitors. The recommended value range is from  $22\mu\text{F}$  to  $68\mu\text{F}$ . Use Equation 7 to determine the required RMS current rating for the output capacitor(s).

$$I_{COx(RMS)} = \frac{V_{Ox} \times (V_{INx} - V_{Ox})}{\sqrt{12} \times V_{INx} \times L_{Ox} \times f_{SW}}$$

(7)

For this design two TDK C3216X5R0J226M 22 $\mu$ F output capacitors are used. The typical ESR is 2 m $\Omega$  each. The calculated RMS current is 0.19A and each output capacitor is rated for 4A.

#### **Input Capacitor Selection**

The TPS54294 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. A ceramic capacitor of or above 10µF is recommended for the decoupling capacitor. Additionally, 0.1 µF ceramic capacitors from pin 1 and Pin 16 to ground are recommended to improve the stability and reduce the SWx node overshoots. The capacitors voltage rating needs to be greater than the maximum input voltage.

#### **Bootstrap Capacitor Selection**

A 0.1 µF ceramic capacitors must be connected between the VBSTx and SWx pins for proper operation. It is recommended to use ceramic capacitors with a dielectric of X5R or better.

### **VREG5 Capacitor Selection**

A 1  $\mu$ F ceramic capacitor must be connected between the VREG5 and GND pins for proper operation. It is recommended to use a ceramic capacitor with a dielectric of X5R or better.

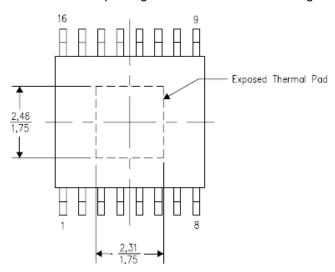

#### **Thermal Information**

This 16-pin PWP package incorporates an exposed thermal pad. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB is used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the exposed thermal pad and how to use the advantage of its heat dissipating abilities, refer to the Technical Brief, *PowerPAD™ Thermally Enhanced Package*, Texas Instruments Literature No. SLMA002 and Application Brief, *PowerPAD™ Made Easy*, Texas Instruments Literature No. SLMA004.

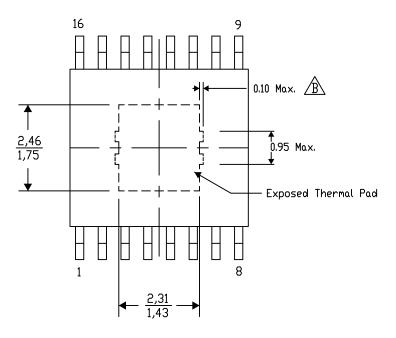

The exposed thermal pad dimensions for this package are shown in the following illustration.

Figure 25. Thermal Pad Dimensions

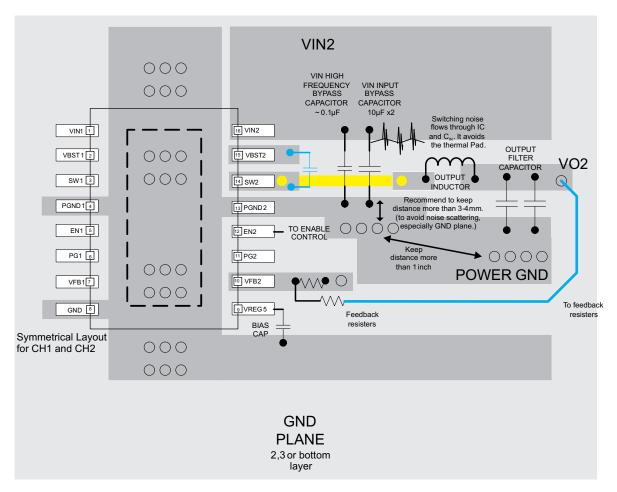

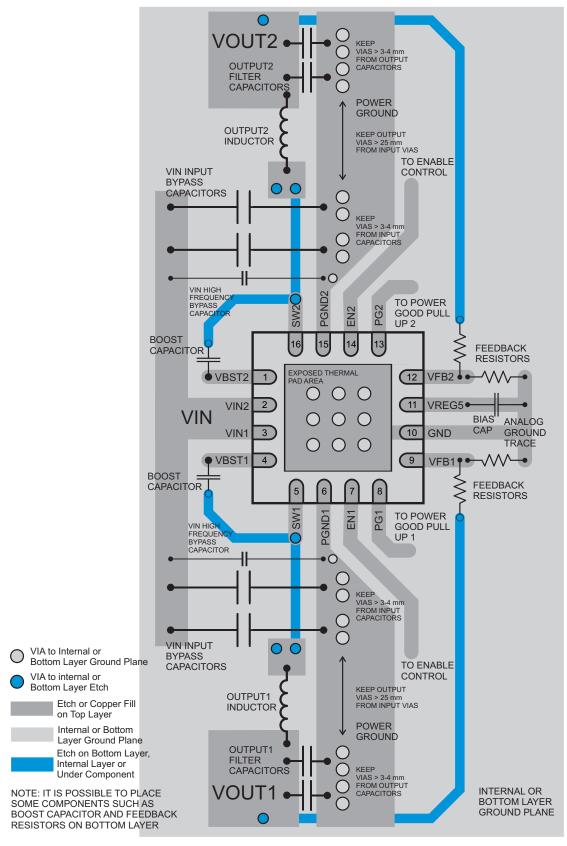

#### **Layout Considerations**

- 1. Keep the input current loop as small as possible. And avoid the input switching current through the thermal pad.

- 2. Keep the SW node as physically small and short as possible to minimize parasitic capacitance and inductance and to minimize radiated emissions.

- 3. Keep analog and non-switching components away from switching components.

- 4. Make a single point connection from the signal ground to power ground.

- 5. Do not allow switching currents to flow under the device.

- 6. Keep the pattern lines for VINx and PGNDx broad.

- 7. Exposed pad of device must be soldered to PGND.

- 8. VREG5 capacitor should be placed near the device, and connected to GND.

- 9. Output capacitors should be connected with a broad pattern to the PGND.

- 10. Voltage feedback loops should be as short as possible, and preferably with ground shields.

- 11. Kelvin connections should be brought from the output to the feedback pin of the device.

- 12. Providing sufficient vias is preferable for VIN, SW and PGND connections.

- 13. PCB pattern for VIN, SW, and PGND should be as broad as possible.

- 14. VIN Capacitor should be placed as near as possible to the device.

#### O Via to GND Plane

- Blue parts can be placed on the bottom side

- Connect the SWx pins through another layer with the inductor (yellow line)

Figure 26. TPS54294 Layout

Figure 27. TPS54294 RSA Package Layout

Submit Documentation Feedback

### **REVISION HISTORY**

NOTE: Page numbers of current version may differ from previous versions.

| Changes from Original (October 2011) to Revision A                                     | Page |

|----------------------------------------------------------------------------------------|------|

| Added input voltage range for VFB1, VFB2 to Absolute Maximum Ratings                   | 2    |

| Added input voltage range for VFB1, VFB2 to Recommended Operating Conditions           | 3    |

| Added indication for not production tested parameters.                                 | 3    |

| Added indication for not production tested parameters.                                 | 4    |

| Added Over/Under Voltage Protection Description                                        | 8    |

| Changes from Revision A (November 2011) to Revision B                                  | Page |

| Deleted V <sub>REG5</sub> MIN and MAX values                                           | 3    |

| Deleted Line and Load regulation specs from VREG5 specification                        | 3    |

| Added "Specified by design. Not production tested" annotation to MOSFETs specification | 3    |

| Deleted MIN and MAX values from V <sub>UVREG5</sub> specification                      | 4    |

| Changes from Revision B (December 2011) to Revision C                                  | Page |

| Removed ( SWIFT™) from the data sheet title                                            | 1    |

| Added 16-pin VQFN package to Features and Description                                  | 1    |

| Added RSA pinout image, pin names and functions to Device Info Section                 | 5    |

| • Changed TPS54295, 2 places to TPS54294 in Over/Under Voltage protection section      | 8    |

| Added RSA-package board layout,                                                        | 18   |

| Changes from Revision C (April 2013) to Revision D                                     | Page |

| Deleted T <sub>A</sub> = 25°C from the ELECTRICAL CHARACTERISTICS Conditions column    | 3    |

| <ul> <li>Changed VIN supply current Max value From: 2000 μA To: 2500 μA</li> </ul>     | 3    |

| Changed VIN shutdown current Max value From: 150 μA To: 200 μA                         | 3    |

18-Jun-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | _       | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        |                  | (3)                 |              | (4/5)          |         |

| TPS54294PWP      | ACTIVE | HTSSOP       | PWP     | 16   | 90   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PS54294        | Samples |

| TPS54294PWPR     | ACTIVE | HTSSOP       | PWP     | 16   | 2000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | PS54294        | Samples |

| TPS54294RSAR     | ACTIVE | QFN          | RSA     | 16   | 3000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>54294   | Samples |

| TPS54294RSAT     | ACTIVE | QFN          | RSA     | 16   | 250  | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>54294   | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

### **PACKAGE OPTION ADDENDUM**

18-Jun-2013

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com 13-Feb-2016

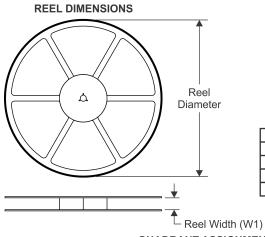

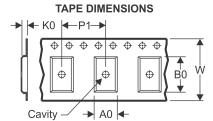

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

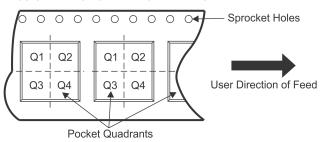

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS54294PWPR               | HTSSOP          | PWP                | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS54294PWPR               | HTSSOP          | PWP                | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS54294RSAR               | QFN             | RSA                | 16 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| TPS54294RSAT               | QFN             | RSA                | 16 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com 13-Feb-2016

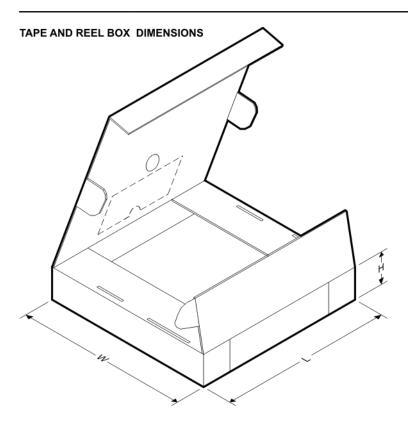

#### \*All dimensions are nominal

| 7 III dilitorio di o Tiorima. |              |                 |      |      |             |            |             |

|-------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS54294PWPR                  | HTSSOP       | PWP             | 16   | 2000 | 367.0       | 367.0      | 35.0        |

| TPS54294PWPR                  | HTSSOP       | PWP             | 16   | 2000 | 367.0       | 367.0      | 38.0        |

| TPS54294RSAR                  | QFN          | RSA             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS54294RSAT                  | QFN          | RSA             | 16   | 250  | 210.0       | 185.0      | 35.0        |

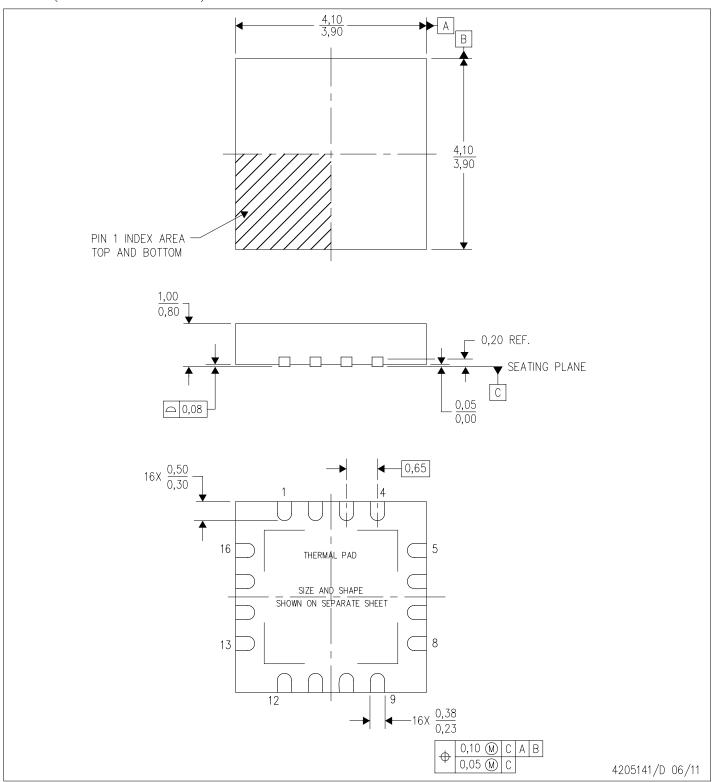

# RSA (S-PVQFN-N16)

### PLASTIC QUAD FLATPACK NO-LEAD

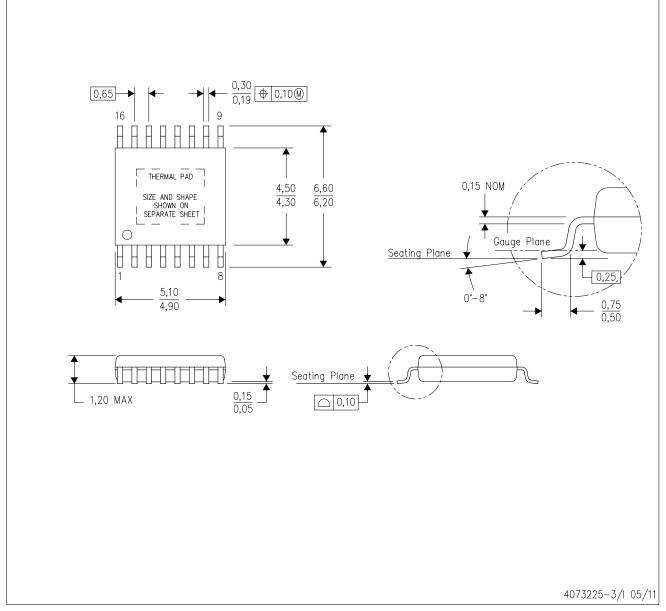

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No—leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

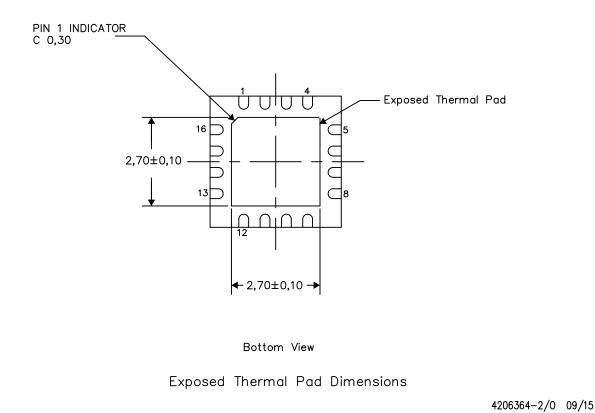

# RSA (S-PVQFN-N16)

PLASTIC QUAD FLATPACK NO-LEAD

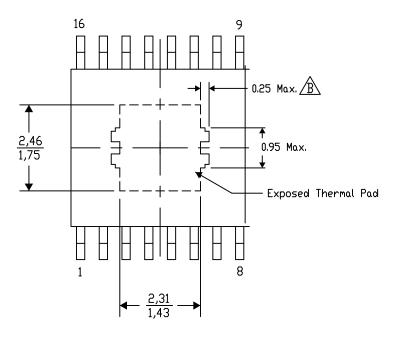

### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTES:

A. All linear dimensions are in millimeters

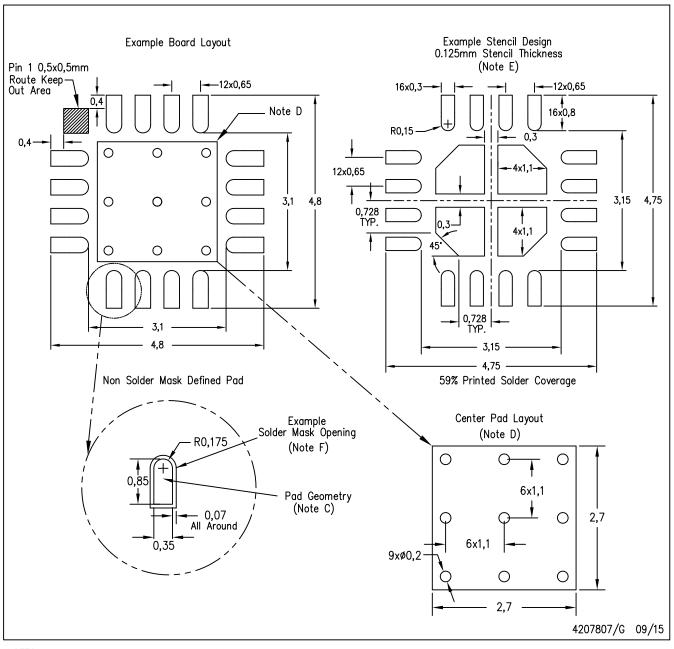

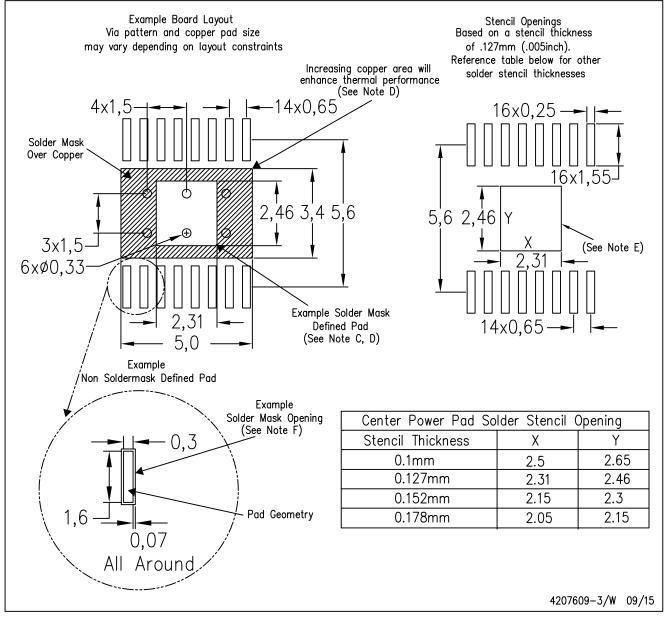

# RSA (S-PVQFN-N16)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for solder mask tolerances.

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PWP (R-PDSO-G16)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G16) PowerPAD™ SMALL PLASTIC OUTLINE

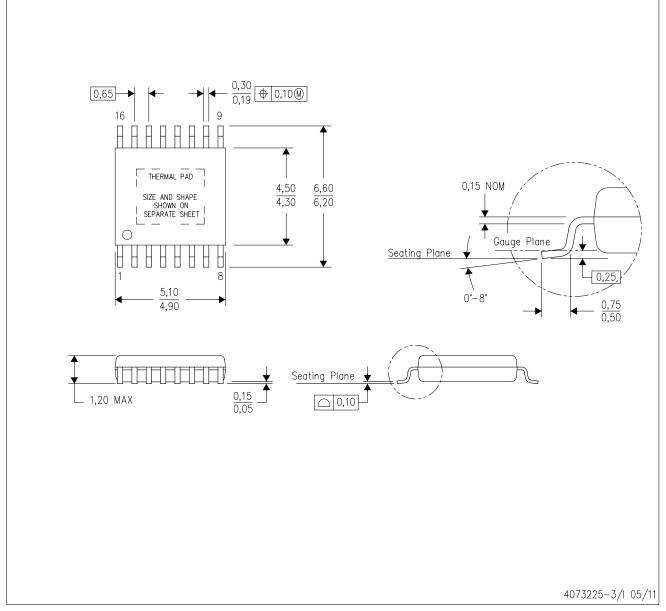

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-6/AO 01/16

NOTE: A. All linear dimensions are in millimeters

🛕 Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

# PWP (R-PDSO-G16)

## PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PWP (R-PDSO-G16)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G16) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-45/AO 01/16

NOTE: A. All linear dimensions are in millimeters

🛕 Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's non-compliance with the terms and provisions of this Notice.