#### TPS65051-Q1

SLVSBJ1B-SEPTEMBER 2012-REVISED JANUARY 2017

# **TPS65051-Q1 6-Channel Power Management IC With 2** Step-Down Converters and 4 Low-Input-Voltage LDOs

#### Features 1

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: –40°C to +125°C Ambient Operating Temperature Range

- **Device HBM ESD Classification Level H2**

- Device CDM ESD Classification Level C3B \_

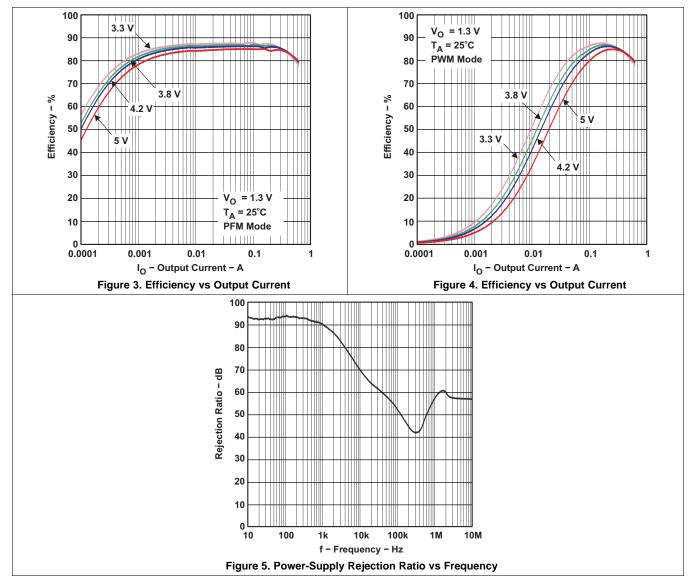

- Up To 95% Efficiency

- Output Current for DC-DC Converter: DCDC1 = 1 A; DCDC2 = 0.6 A

- Externally Adjustable Output Voltage for DC-DC Converter

- V<sub>I</sub> Range for DC-DC Converters From 2.5 V to 6 V

- 2.25-MHz Fixed-Frequency Operation

- Power-Save Mode at Light Load Current

- 180° Out-of-Phase Operation

- Output-Voltage Accuracy in PWM Mode ±1%

- Low-Ripple PFM Mode

- Total Typical 32-µA Quiescent Current for Both **DC-DC Converters**

- 100% Duty Cycle for Lowest Dropout

- Two General-Purpose 400-mA, High-PSRR LDOs

- Two General-Purpose 200-mA, High-PSRR LDOs

- V<sub>1</sub> Range for LDOs from 1.5 V to 6.5 V

- Digital Voltage Selection for the LDOs

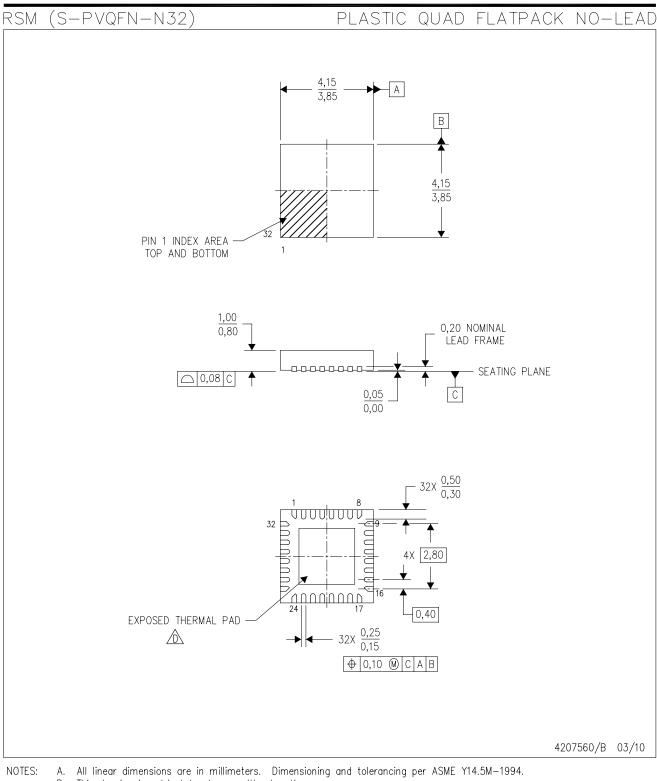

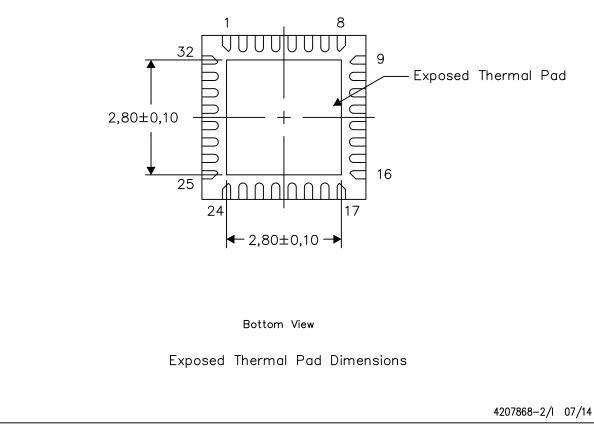

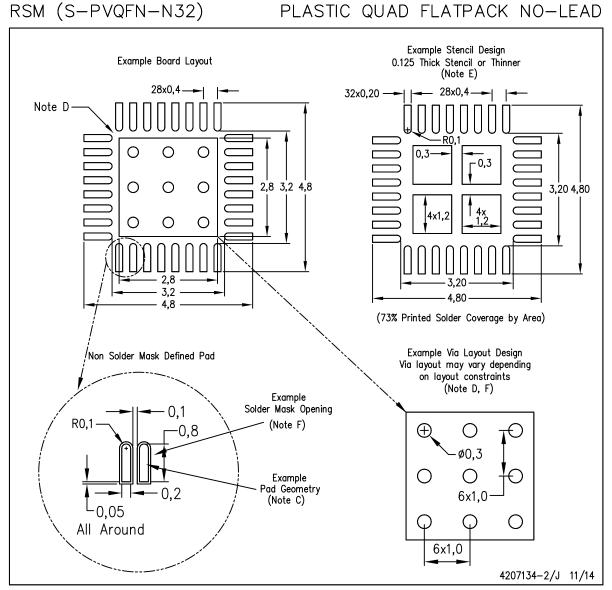

- Available in a 4-mm × 4-mm 32-Pin VQFN Package

# 2 Applications

Automotive Infotainment Automotive Cluster Automotive Digital Radio

# 3 Description

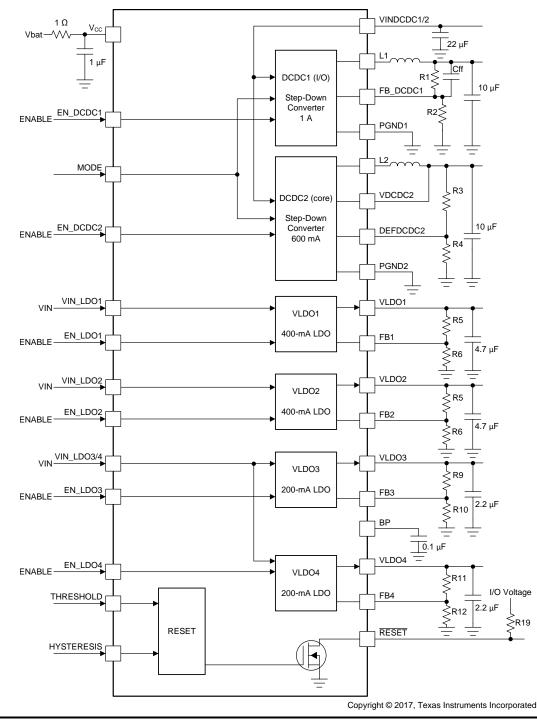

The TPS65051-Q1 device is an integrated powermanagement IC for applications powered by one Li-Ion or Li-Polymer cell, which requires multiple power rails. The TPS65051-Q1 device provides two efficient, 2.25-MHz step-down converters targeted at providing the core voltage and I/O voltage in a processor-based system. Both step-down converters enter a low-power mode at light load for maximum efficiency across the widest possible range of load currents.

For low-noise applications, the user can force the devices into fixed-frequency PWM mode by pulling the MODE pin high. Operating in the shutdown mode reduces the current consumption to less than 1  $\mu$ A. The devices allow the use of small inductors and capacitors to achieve a small solution size. The TPS65051-Q1 device provides an output current of up to 1 A (DCDC1) and 0.6 A (DCDC2). The TPS65051-Q1 device also integrates two 400-mA LDO and two 200-mA LDO voltage regulators, which one can turn on or off using separate enable pins on each LDO. Each LDO operates with an input voltage range between 1.5 V and 6.5 V, allowing the supply to be from one of the step-down converters or directly from the main battery.

The LDO voltage of the TPS65051-Q1 device is adjustable using external resistor dividers.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS65051-Q1 | VQFN (32) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

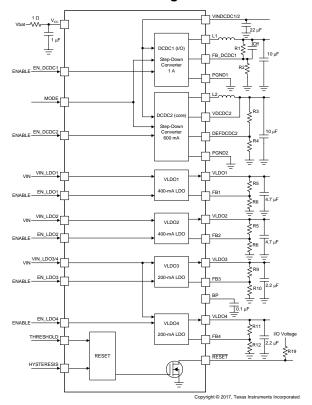

#### **Block Diagram**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# Table of Contents

| Fea  | tures 1                            |    | 7 |

|------|------------------------------------|----|---|

| Арр  | lications1                         |    | 7 |

| Des  | cription1                          | 8  | A |

|      | ision History 2                    |    | 8 |

| Pin  | Configuration and Functions        |    | 8 |

| Spe  | cifications                        | 9  | F |

| 6.1  | Absolute Maximum Ratings 4         | 10 | I |

| 6.2  | ESD Ratings 4                      |    | 1 |

| 6.3  | Recommended Operating Conditions 5 |    |   |

| 6.4  | Thermal Information 5              | 11 | 1 |

| 6.5  | Electrical Characteristics 6       |    | 1 |

| 6.6  | Switching Characteristics 8        |    |   |

| 6.7  | Typical Characteristics 8          |    | 1 |

| Deta | ailed Description 10               |    | 1 |

| 7.1  | Overview 10                        |    | 1 |

| 7.2  | Functional Block Diagram 10        | 12 |   |

|      |                                    |    | 1 |

|   | 7.3  | Feature Description                             | 11 |

|---|------|-------------------------------------------------|----|

|   | 7.4  | Device Functional Modes                         | 14 |

| ; | App  | lication and Implementation                     | 15 |

|   | 8.1  | Application Information                         | 15 |

|   | 8.2  | Typical Application                             | 15 |

| ) | Pow  | er Supply Recommendations                       | 23 |

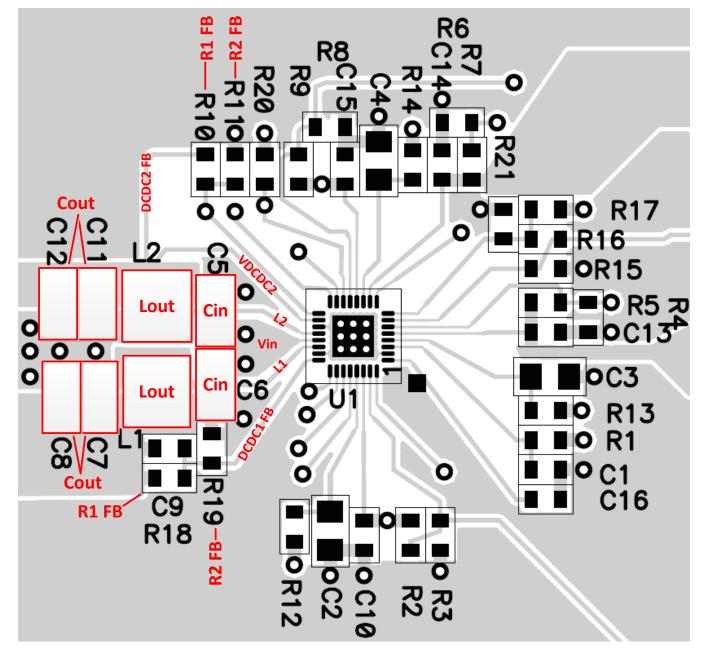

| 0 | Lay  | out                                             | 23 |

|   | 10.1 | Layout Guidelines                               | 23 |

|   |      | Layout Example                                  |    |

| 1 | Dev  | ice and Documentation Support                   | 25 |

|   | 11.1 | Receiving Notification of Documentation Updates | 25 |

|   | 11.2 | Community Resource                              | 25 |

|   | 11.3 | Trademarks                                      | 25 |

|   | 11.4 | Electrostatic Discharge Caution                 | 25 |

|   | 11.5 | Glossary                                        | 25 |

| 2 | Mec  | hanical, Packaging, and Orderable               |    |

|   | Info | rmation                                         | 25 |

|   |      |                                                 |    |

# 4 Revision History

1 2

3

4

5

6

7

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision A (November 2012) to Revision B

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device |    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section, Layout section,                                                                                                             | 1  |

| • | Deleted all references to TPS65050-Q1, TPS65052-Q1, TPS65054-Q1, and TPS65056-Q1 part numbers                                                                                                                                | 1  |

| • | Deleted the Ordering Information table                                                                                                                                                                                       | 3  |

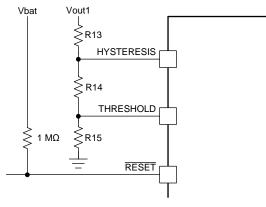

| • | Changed the resistor labels of R3, R4, and R5 to R13, R14, and R15 in the RESET section                                                                                                                                      | 20 |

| • | Added the Receiving Notification of Documentation Updates section                                                                                                                                                            | 25 |

| • | Changed the electrostatic discharge statement                                                                                                                                                                                | 25 |

|   |                                                                                                                                                                                                                              |    |

www.ti.com

#### Page

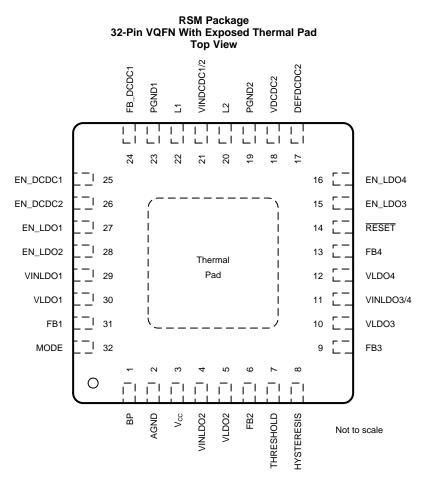

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN                                                                                                                 |                                                                                             | 1/0                                                                            | DESCRIPTION                                                                                                                                             |  |  |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.                                                                                                            |                                                                                             | I/O                                                                            | DESCRIPTION                                                                                                                                             |  |  |

| AGND                                                                                                                | 2                                                                                           | I                                                                              | Analog GND, connect to PGND and thermal pad                                                                                                             |  |  |

| BP                                                                                                                  | 1                                                                                           | I                                                                              | Input for bypass capacitor for internal reference                                                                                                       |  |  |

| DEFDCDC2                                                                                                            | 17                                                                                          | I                                                                              | Feedback pin for converter 2. Connect DEFDCDC2 to the center of the external resistor divider.                                                          |  |  |

| EN_DCDC1                                                                                                            | 25                                                                                          | I                                                                              | Enable input for converter 1, active-high                                                                                                               |  |  |

| EN_DCDC2                                                                                                            | 26                                                                                          | I                                                                              | Enable input for converter 2, active-high                                                                                                               |  |  |

| EN_LDO1 27 I Enable input for LDO1. Logic high enables the LDO, logic low disables the LDO.                         |                                                                                             |                                                                                |                                                                                                                                                         |  |  |

| EN_LDO2                                                                                                             | EN_LDO2 28 I Enable input for LDO2. Logic high enables the LDO, logic low disables the LDO. |                                                                                |                                                                                                                                                         |  |  |

| EN_LDO3         15         I         Enable input for LDO3. Logic high enables the LDO, logic low disables the LDO. |                                                                                             | Enable input for LDO3. Logic high enables the LDO, logic low disables the LDO. |                                                                                                                                                         |  |  |

| EN_LDO4                                                                                                             | 16                                                                                          | I                                                                              | Enable input for LDO4. Logic high enables the LDO, logic low disables the LDO.                                                                          |  |  |

| FB1                                                                                                                 | 31                                                                                          | I                                                                              | Feedback input for the external voltage divider                                                                                                         |  |  |

| FB2                                                                                                                 | 6                                                                                           | I                                                                              | Feedback input for the external voltage divider                                                                                                         |  |  |

| FB3                                                                                                                 | 9                                                                                           | I                                                                              | Feedback input for the external voltage divider                                                                                                         |  |  |

| FB4                                                                                                                 | 13                                                                                          | I                                                                              | Feedback input for the external voltage divider                                                                                                         |  |  |

| FB_DCDC1                                                                                                            | 24                                                                                          | I                                                                              | Input to adjust output voltage of converter 1 between 0.6 V and V <sub>I</sub> . Connect an external resistor divider between VOUT1, this pin, and GND. |  |  |

| HYSTERESIS                                                                                                          | HYSTERESIS 8 I                                                                              |                                                                                | Input for hysteresis on reset threshold                                                                                                                 |  |  |

| L1                                                                                                                  | 22                                                                                          | 0                                                                              | Switch pin of converter 1. Connected to inductor                                                                                                        |  |  |

| L2                                                                                                                  | 20                                                                                          | 0                                                                              | Switch pin of converter 2. Connected to inductor                                                                                                        |  |  |

TPS65051-Q1 SLVSBJ1B – SEPTEMBER 2012 – REVISED JANUARY 2017

www.ti.com

STRUMENTS

EXAS

### Pin Functions (continued)

| PIN<br>NAME NO. |    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                           |  |  |

|-----------------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 |    | 1/0 |                                                                                                                                                                                                                                                                                       |  |  |

| MODE            | 32 | I   | Select between power-safe mode and forced-PWM mode for DCDC1 and DCDC2. In power-safe mode, the device uses PFM at light loads, PWM for higher loads. Setting this pin to high level selects forced-PWM mode. If this pin has low level, then the device operates in power-safe mode. |  |  |

| PGND1           | 23 | I   | GND for converter 1                                                                                                                                                                                                                                                                   |  |  |

| PGND2           | 19 | I   | GND for converter 2                                                                                                                                                                                                                                                                   |  |  |

| RESET           | 14 | 0   | Open-drain active-low reset output, 100-ms reset-delay time                                                                                                                                                                                                                           |  |  |

| THRESHOLD 7 I   |    | I   | Reset input                                                                                                                                                                                                                                                                           |  |  |

| V <sub>cc</sub> | 3  | I   | Power supply for digital and analog circuitry of DCDC1, DCDC2 and LDOs. Connect this pin to the same voltage supply as VINDCDC1/2.                                                                                                                                                    |  |  |

| VDCDC2          | 18 | I   | Feedback voltage-sense input, connect directly to the output of converter 2.                                                                                                                                                                                                          |  |  |

| VINDCDC1/2 21   |    | I   | Input voltage for VDCDC1 and VDCDC2 step-down converters. Connect this pin to the same voltage supply as $V_{\text{CC}}.$                                                                                                                                                             |  |  |

| VINLDO1         | 29 | I   | Input voltage for LDO1                                                                                                                                                                                                                                                                |  |  |

| VINLDO2         | 4  | I   | Input voltage for LDO2                                                                                                                                                                                                                                                                |  |  |

| VINLDO3/4       | 11 | I   | Input voltage for LDO3 and LDO4                                                                                                                                                                                                                                                       |  |  |

| VLDO1           | 30 | 0   | Output voltage of LDO1                                                                                                                                                                                                                                                                |  |  |

| VLDO2           | 5  | 0   | Output voltage of LDO2                                                                                                                                                                                                                                                                |  |  |

| VLDO3           | 10 | 0   | Output voltage of LDO3                                                                                                                                                                                                                                                                |  |  |

| VLDO4           | 12 | 0   | Output voltage of LDO4                                                                                                                                                                                                                                                                |  |  |

| Thermal pad     |    | —   | Connect to GND                                                                                                                                                                                                                                                                        |  |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                                    | MIN  | MAX                   | UNIT |

|------------------|------------------------------------------------------------------------------------|------|-----------------------|------|

| VI               | Input voltage on all pins except AGND, PGND, and EN_LDO1 pins with respect to AGND | -0.3 | 7                     | V    |

|                  | Input voltage range on EN_LDO1 pins with respect to AGND                           | -0.3 | V <sub>CC</sub> + 0.5 |      |

|                  | Current at VINDCDC1/2, L1, PGND1, L2, PGND2                                        |      | 1800                  | mA   |

| I <sub>I</sub>   | Current at all other pins                                                          |      | 1000                  | mA   |

| Vo               | Output voltage for LDO1, LDO2, LDO3, and LDO4                                      | -0.3 | 4                     | V    |

|                  | Continuous total power dissipation                                                 |      | e Thermal<br>mation   |      |

| T <sub>A</sub>   | Operating free-air temperature                                                     | -40  | 125                   | °C   |

| T <sub>stg</sub> | Storage temperature                                                                | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |               |                                                         | VALUE | UNIT | 1 |

|--------------------|---------------|---------------------------------------------------------|-------|------|---|

| V                  | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | 2000  | V    |   |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per AEC Q100-011            | 750   | V    |   |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                                             | MIN | NOM | MAX        | UNIT |

|----------------|-----------------------------------------------------------------------------|-----|-----|------------|------|

| VI             | Input voltage for step-down converters, VINDCDC1/2                          | 2.5 |     | 6          | V    |

| V              | Output voltage for step-down converter, VDCDC1                              | 0.6 |     | VINDCDC1/2 | V    |

| Vo             | Output voltage for step-down converter, VDCDC2                              | 0.6 |     | VINDCDC1/2 | V    |

| VI             | Input voltage for LDOs, VINLDO1, VINLDO2, VINLDO3/4                         | 1.5 |     | 6.5        | V    |

| V              | Output voltage for LDO1 and LDO2                                            | 1   |     | 3.6        | V    |

| Vo             | Output voltage for LDO3 and LDO4                                            | 1   |     | 3.6        | V    |

|                | Output current at L1 (DCDC1)                                                |     |     | 1000       | mA   |

|                | Output current at L2 (DCDC2)                                                |     |     | 600        | mA   |

| lo             | Output current at VLDO1, VLDO2                                              |     |     | 400        | mA   |

|                | Output current at VLDO3, VLDO4                                              |     |     | 200        | mA   |

|                | Inductor at L1, L2 <sup>(1)</sup>                                           | 1.5 | 2.2 |            | μH   |

| ~              | Output capacitor at VDCDC1, VDCDC2 <sup>(1)</sup>                           | 10  | 22  |            | μF   |

| с <sub>о</sub> | Output capacitor at VLDO1, VLDO2, VLDO3, VLDO4 <sup>(1)</sup>               | 2.2 |     |            | μF   |

|                | Input capacitor at VCC <sup>(1)</sup>                                       | 1   |     |            | μF   |

| CI             | Input capacitor at VINLDO1, VINLDO2 <sup>(1)</sup>                          | 2.2 |     |            | μF   |

|                | Input capacitor at VINLDO3/4 <sup>(1)</sup>                                 | 2.2 |     |            | μF   |

| T <sub>A</sub> | Operating ambient temperature                                               | -40 |     | 125        | °C   |

|                | Resistor from battery voltage to $V_{CC}$ used for filtering <sup>(2)</sup> |     | 1   | 10         | Ω    |

See the *Application Information* section of this data sheet for more details.

Up to 2 mA can flow into V<sub>CC</sub>; when both converters are running in PWM, this resistor causes the UVLO threshold to shift accordingly.

#### 6.4 Thermal Information

|                       |                                              | TPS65051-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSM (VQFN)  | UNIT |

|                       |                                              | 32 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 37.2        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 30.1        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.8         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.4         | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 7.6         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.3         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1) report.

SLVSBJ1B-SEPTEMBER 2012-REVISED JANUARY 2017

www.ti.com

### 6.5 Electrical Characteristics

$V_{CC}$  = VINDCDC1/2 = 3.6 V, EN =  $V_{CC}$ , MODE = GND, L = 2.2  $\mu$ H, C<sub>0</sub> = 10  $\mu$ F, T<sub>A</sub> = -40°C to 125°C, typical values are at T<sub>A</sub> = 25°C (unless otherwise noted).

| (                   | PARAMETER                                                                                                      | TEST                                                                                                                      | CONDITIONS                                                                                  | MIN        | TYP                   | MAX             | UNIT   |

|---------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|-----------------------|-----------------|--------|

| SUPPLY              | CURRENT                                                                                                        |                                                                                                                           |                                                                                             |            |                       |                 |        |

| VI                  | Input voltage range at VINDCDC1/2                                                                              |                                                                                                                           |                                                                                             | 2.5        |                       | 6               | V      |

|                     |                                                                                                                | $EN_DCDC1 = V_I OR EN_D$                                                                                                  | = GND) device not switching,<br>CDC2 = V <sub>I</sub> ;<br>N_LDO3 = EN_LDO = GND            |            | 20                    | 30              | μΑ     |

| Ι <sub>Q</sub>      | Operating quiescent current<br>Total current into V <sub>CC</sub> , VINDCDC1/2,<br>VINLDO1, VINLDO2, VINLDO3/4 | Two converters, $I_O = 0$ mA<br>PFM mode enabled (Mode<br>EN_DCDC1 = V <sub>1</sub> AND EN_<br>EN_LDO1 = EN_LDO2 = E      |                                                                                             |            | 32                    | 40              | μΑ     |

|                     |                                                                                                                | One converter, $I_0 = 0$ mA.<br>PFM mode enabled (Mode<br>EN_DCDC1 = V <sub>1</sub> OR EN_D<br>EN_LDO1 = EN_LDO2 = E      |                                                                                             |            | 180                   | 250             | μΑ     |

|                     | Operating quiescent current into $V_{CC}$                                                                      | One converter, $I_0 = 0$ mA.<br>Switching with no load (Mo<br>EN_DCDC1 = V <sub>1</sub> OR EN_D<br>= EN_LDO3 = EN_LDO = 0 | $CDC2 = V_1$ ; $EN_LDO1 = EN_LDO2$                                                          |            | 0.85                  |                 | mA     |

| Ι <sub>Q</sub>      |                                                                                                                | Two converters, $I_0 = 0$ mA<br>Switching with no load (Mo<br>EN_DCDC1 = V <sub>1</sub> AND EN_<br>EN_LDO2 = EN_LDO3 = E  | $DCDC2 = V_i; EN_LDO1 =$                                                                    |            | 1.25                  |                 | mA     |

| I <sub>(SD)</sub>   | Shutdown current                                                                                               | EN_DCDC1 = EN_DCDC2 = GND EN_LDO1 = EN_LDO2 =<br>EN_LDO3 = EN_LDO4 = GND                                                  |                                                                                             |            | 9                     | 12              | μΑ     |

| V <sub>(UVLO)</sub> | Undervoltage lockout threshold for DC-<br>DC converters and LDOs                                               | Voltage at V <sub>CC</sub>                                                                                                |                                                                                             |            | 1.8                   | 2               | V      |

| EN_DCDC             | C1, EN_DCDC2, DEFDCDC2, DEFLDO1, I                                                                             | DEFLDO2, DEFLDO3, DEFL                                                                                                    | DO4, EN_LDO1, EN_LDO2, EN_LDO                                                               | 03, EN_LDO | <b>D</b> 4            |                 |        |

| V <sub>IH</sub>     | High-level input voltage                                                                                       |                                                                                                                           | CDC2, DEFDCDC2, DEFLDO1,<br>FLDO4, EN_LDO1, EN_LDO2,                                        | 1.2        |                       | V <sub>cc</sub> | V      |

| V <sub>IL</sub>     | Low-level input voltage                                                                                        |                                                                                                                           | MODE, EN_DCDC1, EN_DCDC2, DEFLDO1, DEFLDO2,<br>DEFLDO3, DEFLDO4, EN_LDO1, EN_LDO2, EN_LDO3, |            |                       | 0.4             | V      |

| I <sub>IB</sub>     | Input bias current                                                                                             | DEFDCDC2,                                                                                                                 | DEFLDO1, DEFLDO2, DEFLDO3, DEFLDO4, EN_LDO1, EN_LDO1, EN_LDO1, EN_LDO2,                     |            | 0.01                  | 1               | μΑ     |

|                     |                                                                                                                | V_FB_LDOx = 1 V, FB_LD<br>FB_LDO4                                                                                         | 01, FB_LDO2, FB_LDO3,                                                                       |            |                       | 100             | nA     |

| POWER S             | SWITCH                                                                                                         | -                                                                                                                         |                                                                                             |            |                       |                 |        |

|                     |                                                                                                                | DCDC1                                                                                                                     | VINDCDC1/2 = 3.6 V                                                                          |            | 280                   | 630             |        |

| r                   | P-channel MOSFET on-resistance                                                                                 | Debei                                                                                                                     | VINDCDC1/2 = 2.5 V                                                                          |            | 400                   |                 | mΩ     |

| r <sub>DS(on)</sub> |                                                                                                                | DCDC2                                                                                                                     | VINDCDC1/2 = 3.6 V                                                                          |            | 280                   | 630             | 11152  |

|                     |                                                                                                                | 00002                                                                                                                     | VINDCDC1/2 = 2.5 V                                                                          |            | 400                   |                 |        |

| l <sub>lkg</sub>    | P-channel leakage current                                                                                      | VDCDCx = V <sub>(DS)</sub> = 6 V                                                                                          |                                                                                             |            |                       | 1               | μA     |

|                     |                                                                                                                | DCDC1                                                                                                                     | VINDCDC1/2 = 3.6 V                                                                          |            | 220                   | 450             |        |

| [DC().)             | N-channel MOSFET on-resistance                                                                                 |                                                                                                                           | VINDCDC1/2 = 2.5 V                                                                          |            | 320                   |                 | mΟ     |

| r <sub>DS(on)</sub> |                                                                                                                | DCDC2                                                                                                                     | VINDCDC1/2 = 3.6 V                                                                          |            | <u>320</u><br>220 450 |                 |        |

|                     |                                                                                                                |                                                                                                                           | VINDCDC1/2 = 2.5 V                                                                          |            | 320                   |                 |        |

| l <sub>lkg</sub>    | N-channel leakage current                                                                                      | VDCDCx = V <sub>(DS)</sub> = 6 V                                                                                          |                                                                                             |            | 7                     | 10              | μA     |

| I <sub>(LIMF)</sub> | Forward current limit PMOS (high side) and NMOS (low side)                                                     | DCDC1, 2.5 V $\leq$ VINDCDC                                                                                               |                                                                                             | 1.19       | 1.4                   | 1.65            | А      |

|                     |                                                                                                                | DCDC2, 2.5 V ≤ VINDCDC                                                                                                    |                                                                                             | 0.85       | 1                     | 1.15            | ~      |

|                     | Thermal shutdown                                                                                               | Increasing junction tempera                                                                                               |                                                                                             |            | 150                   |                 | ℃<br>℃ |

|                     | Thermal shutdown hysteresis                                                                                    | Decreasing junction temper                                                                                                | aluie                                                                                       |            | 20                    |                 | ΰU     |

| OUTPUT<br>Vo        | Output-voltage range for DCDC1,                                                                                |                                                                                                                           |                                                                                             | 0.6        | VIND                  | CDC1/2          | V      |

| V <sub>ref</sub>    | DCDC2<br>Reference voltage                                                                                     |                                                                                                                           |                                                                                             |            | 600                   |                 | mV     |

| ref                 | Noterence voltage                                                                                              |                                                                                                                           |                                                                                             |            | 000                   |                 | 111 V  |

6 Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

$V_{CC}$  = VINDCDC1/2 = 3.6 V, EN =  $V_{CC}$ , MODE = GND, L = 2.2  $\mu$ H, C<sub>0</sub> = 10  $\mu$ F, T<sub>A</sub> = -40°C to 125°C, typical values are at T<sub>A</sub> = 25°C (unless otherwise noted).

|                    | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                                                                                                                       | MIN  | TYP | MAX  | UNIT                        |

|--------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-----------------------------|

| V                  | DC output-voltage accuracy, DCDC1,                             | VINDCDC1/2 = 2.5 V to 6 V, 0 mA < $I_0$ = < $I_0$ (maximum)<br>MODE = GND, PFM operation                                                                                                                                                              | -2%  | 0   | 2%   |                             |

| Vo                 | DCDC2 <sup>(1)</sup>                                           | VINDCDC1/2 = 2.5 V to 6 V, 0 mA < $I_0$ = < $I_0$ (maximum)<br>MODE = V <sub>1</sub> , PWM operation                                                                                                                                                  | -1%  | 0   | 1%   |                             |

| $\Delta V_O$       | Power-save-mode ripple voltage <sup>(2)</sup>                  | $I_0 = 1$ mA, MODE = GND, $V_0 = 1.3$ V, bandwith = 20 MHz                                                                                                                                                                                            |      | 25  |      | $\mathrm{mV}_{\mathrm{PP}}$ |

| V <sub>OL</sub>    | RESET, PB_OUT output low voltage                               | I <sub>OL</sub> = 1 mA, Vhysteresis < 1 V, Vthreshold < 1 V                                                                                                                                                                                           |      |     | 0.2  | V                           |

| I <sub>OL</sub>    | RESET, PB_OUT sink current                                     |                                                                                                                                                                                                                                                       |      | 1   |      | mA                          |

|                    | RESET, PB_OUT output leakage<br>current                        | After PB_IN has been pulled high once; Vthreshold > 1 V and Vhysteresis > 1 V, $V_{OH}$ = 6 V                                                                                                                                                         |      | 10  |      | nA                          |

| V <sub>th</sub>    | Vthreshold, Vhysteresis threshold                              |                                                                                                                                                                                                                                                       | 0.98 | 1   | 1.02 | V                           |

| VLDO1,             | VLDO2, VLDO3 AND VLDO4 LOW-DROPC                               | OUT REGULATORS                                                                                                                                                                                                                                        |      |     |      |                             |

| VI                 | Input-voltage range for LDO1, LDO2, LDO3, LDO4                 |                                                                                                                                                                                                                                                       | 1.5  |     | 6.5  | V                           |

| V <sub>(FB)</sub>  | Feedback voltage for FB_LDO1,<br>FB_LDO2, FB_LDO3, and FB_LDO4 |                                                                                                                                                                                                                                                       |      | 1   |      | V                           |

|                    | Maximum output current for LDO1, LDO2                          |                                                                                                                                                                                                                                                       | 400  |     |      | mA                          |

| lo                 | Maximum output current for LDO3, LDO4                          |                                                                                                                                                                                                                                                       | 200  |     |      | mA                          |

|                    | LDO1 short-circuit current limit                               | VLDO1 = GND                                                                                                                                                                                                                                           |      |     | 750  |                             |

| I <sub>(SC)</sub>  | LDO2 short-circuit current limit                               | VLDO2 = GND                                                                                                                                                                                                                                           |      |     | 850  | mA                          |

| (SC)               | LDO3 and LDO4 short-circuit current limit                      | VLDO3 = GND, VLDO4 = GND                                                                                                                                                                                                                              |      |     | 420  |                             |

|                    | Dropout voltage at LDO1                                        | I <sub>O</sub> = 400 mA, VINLDO = 3.4 V                                                                                                                                                                                                               |      |     | 400  |                             |

|                    | Dropout voltage at LDO2                                        | I <sub>O</sub> = 400 mA, VINLDO = 1.8 V                                                                                                                                                                                                               |      |     | 280  | mV                          |

|                    | Dropout voltage at LDO3, LDO4                                  | I <sub>O</sub> = 200 mA, VINLDO = 1.8 V                                                                                                                                                                                                               |      |     | 280  |                             |

| l <sub>ikg</sub>   | Leakage current from VinLDOx to VLDOx                          | LDO enabled, VINLDO = 6.5 V, $V_O = 1 V$ at $T_A = 140^{\circ}C$                                                                                                                                                                                      |      | 3   |      | μΑ                          |

| Vo                 | Output voltage accuracy for LDO1, LDO2, LDO3, LDO4             | I <sub>O</sub> = 10 mA                                                                                                                                                                                                                                | -2%  |     | 1%   |                             |

|                    | Line regulation for LDO1, LDO2, LDO3, LDO4                     | $ \begin{array}{l} \mbox{VINLDO1,2} = \mbox{VLDO1,2} + 0.5 \mbox{ V (minimum 2.5 \mbox{V}) to 6.5 \mbox{V}, \\ \mbox{VINLDO3,4} = \mbox{VLDO3,4} + 0.5 \mbox{ V (minimum 2.5 \mbox{V}) to 6.5 \mbox{V}, \\ \mbox{I}_{O} = 10 \mbox{ mA} \end{array} $ | -1%  |     | 1%   |                             |

|                    | Load regulation for LDO1, LDO2, LDO3, LDO4                     | $I_{O} = 0$ mA to 400 mA for LDO1, LDO2<br>$I_{O} = 0$ mA to 200 mA for LDO3, LDO4                                                                                                                                                                    | -1%  |     | 1%   |                             |

| PSRR               | Power-supply rejection ratio                                   | f = 10 kHz; I <sub>O</sub> = 50 mA; V <sub>I</sub> = V <sub>O</sub> + 1 V                                                                                                                                                                             |      | 70  |      | dB                          |

| R <sub>(DIS)</sub> | Internal discharge resistor at VLDO1, VLDO2, VLDO3, VLDO4      | Active when LDO is disabled                                                                                                                                                                                                                           |      | 350 |      | Ω                           |

|                    | Thermal shutdown                                               | Increasing junction temperature                                                                                                                                                                                                                       |      | 140 |      | °C                          |

|                    | Thermal shutdown hysteresis                                    | Decreasing junction temperature                                                                                                                                                                                                                       |      | 20  |      | °C                          |

Output voltage specification does not include tolerance of external voltage-programming resistors. In power-save mode, device typically enters operation at  $I_{PSM} = V_I / 32 \Omega$ . (1)

(2)

EXAS

STRUMENTS

www.ti.com

SLVSBJ1B-SEPTEMBER 2012-REVISED JANUARY 2017

# 6.6 Switching Characteristics

$V_{CC}$  = VINDCDC1/2 = 3.6 V, EN =  $V_{CC}$ , MODE = GND, L = 2.2  $\mu$ H, C<sub>O</sub> = 10  $\mu$ F, T<sub>A</sub> = -40°C to 125°C, typical values are at T<sub>A</sub> = 25°C (unless otherwise noted).

|                    | PARAMETER                                  | TEST CONDITIONS                            | MIN   | TYP  | MAX   | UNIT |

|--------------------|--------------------------------------------|--------------------------------------------|-------|------|-------|------|

| OSCILL             | ATOR                                       |                                            |       |      |       |      |

| f <sub>SW</sub>    | Oscillator frequency                       |                                            | 2.025 | 2.25 | 2.475 | MHz  |

| OUTPUT             | r                                          |                                            |       |      |       |      |

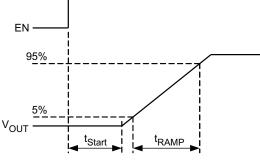

| t <sub>Start</sub> | Start-up time                              | Time from active EN to start switching     |       | 170  |       | μs   |

| t <sub>Ramp</sub>  | VOUT ramp-up time                          | Time to ramp from 5% to 95% of $V_{\rm O}$ |       | 750  |       | μS   |

|                    | RESET delay time                           | Input voltage at threshold pin rising      | 80    | 100  | 120   | ms   |

|                    | PB-ONOFF debounce time                     |                                            | 26    | 32   | 38    | ms   |

| VLDO1,             | VLDO2, VLDO3 AND VLDO4 LOW-E               | PROPOUT REGULATORS                         |       |      |       |      |

|                    | Regulation time for LDO1, LDO2, LDO3, LDO4 | Load change from 10% to 90%                |       | 10   |       | μS   |

|                    | 0                                          | Load change from 10% to 90%                |       | 10   |       |      |

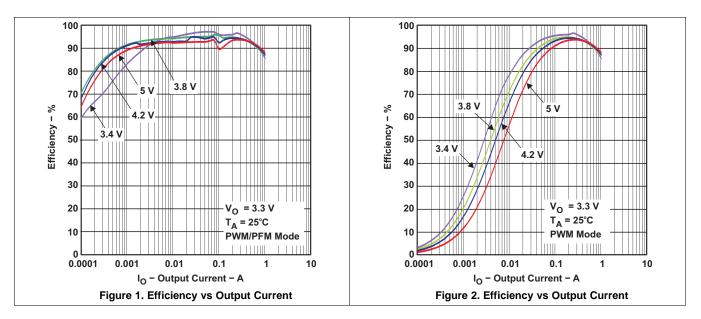

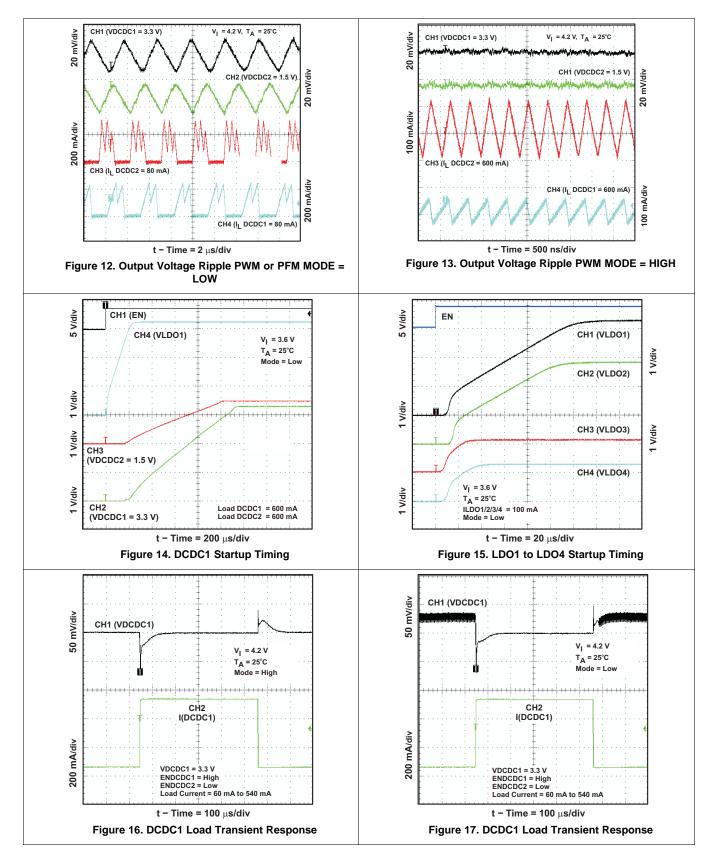

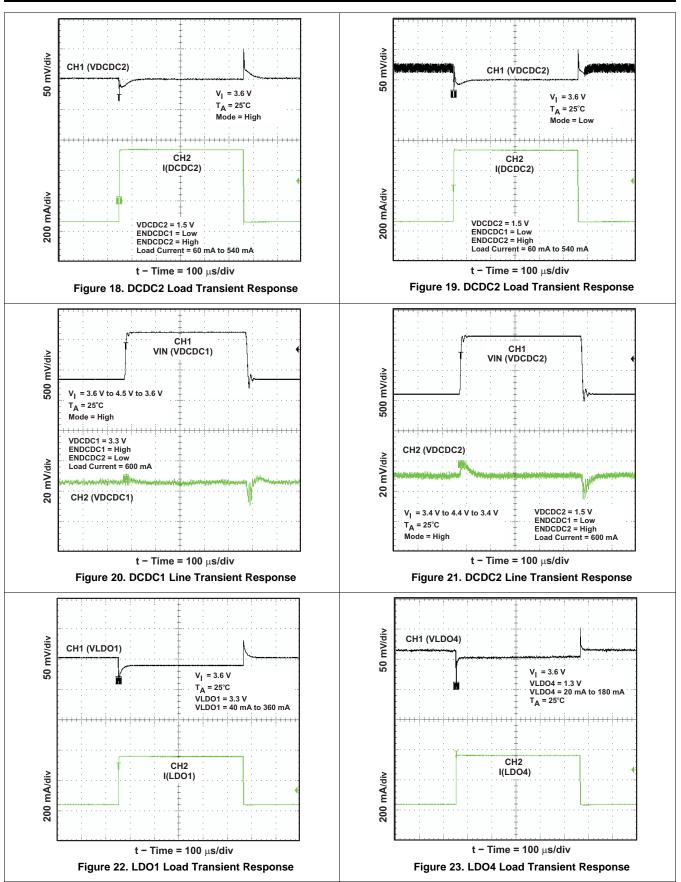

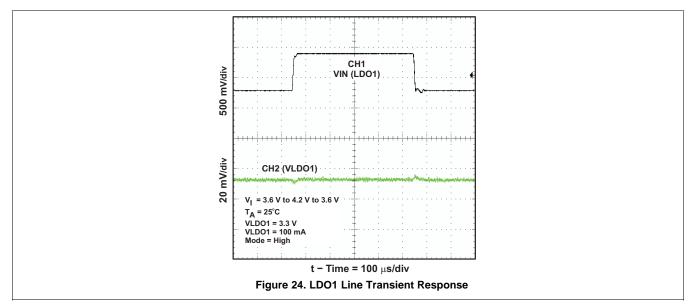

# 6.7 Typical Characteristics

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The TPS65051-Q1 device has 2 DC-DC buck converters and 4 LDOs. Each DC-DC and LDO has enable pins, allowing external sequence control of the PMU rails. The device also has a RESET feature that is generated from a THRESHOLD comparator. This RESET signal can be used to reset or warn of power shutdown to the embedded mircocontroller or processor. The TPS65051-Q1 device makes power-system integration easy for a variety of embedded processors or FPGAs.

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Operation

The TPS65051-Q1 device has two synchronous step-down converters. The converters operate with 2.25-MHz (typical) fixed-frequency pulse-width modulation (PWM) at moderate to heavy load currents. At light load currents, the converters automatically enter power-save mode and operate with PFM (pulse-frequency modulation).

During PWM operation, the converters use a unique fast-response voltage-mode controller scheme with input voltage feed-forward to achieve good line and load regulation, allowing the use of small ceramic input and output capacitors. At the beginning of each clock cycle initiated by the clock signal, the P-channel MOSFET switch turns on, the inductor current ramps up until the current comparator trips, and the control logic turns off the switch. The current-limit comparator turns off the switch if the current exceeds the limit of the P-channel switch. After the adaptive dead time, which prevents shoot-through current, the N-channel MOSFET rectifier turns on, and the inductor current ramps down. The clock signal turning off the N-channel rectifier and turning on the on the P-channel switch initiates the next cycle.

The two DC-DC converters operate synchronized to each other, with converter 1 as the master. A 180° phase shift between converter 1 and converter 2 decreases the input rms current, allowing the use of smaller input capacitors.

#### 7.3.2 DCDC1 Converter

An external resistor divider connected to FB\_DCDC1 pin sets the converter 1 output voltage. See the *Converter* 1 (*DCDC1*) section for more details. The maximum output current is 1 A.

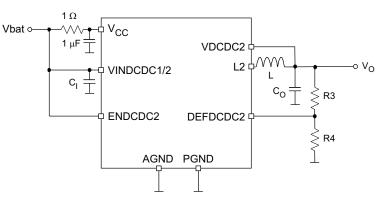

#### 7.3.3 DCDC2 Converter

Connect the VDCDC2 pin directly to the DCDC2 converter output voltage. The DEFDCDC2 pin selects the DCDC2 converter output voltage. See the *Converter 2 (DCDC2)* section for more details. The maximum output current is 600 mA.

An external resistor divider sets the output voltage. Connect the DEFDCDC2 pin to the external resistor divider.

#### 7.3.4 Dynamic Voltage Positioning

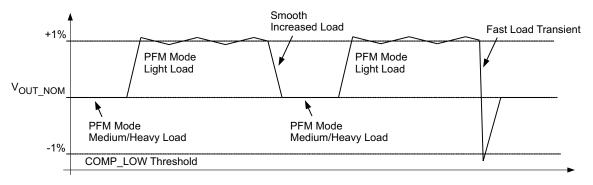

This feature reduces the voltage under- and overshoots at load steps from light to heavy load and vice versa. It is activated In the power-save mode of operation, running the converter in PFM mode activates dynamic voltage positioning. Dynamic voltage positioning provides more headroom for both the voltage drop at a load step and the voltage increase at a load throw-off, thereby improving load-transient behavior.

At light loads, in which the converters operate in PFM mode, the typical output-voltage regulation is 1% higher than the nominal value. In the event of a load transient from light load to heavy load, the output voltage drops until it reaches the skip-comparator-low threshold, set to 1% below the nominal value, and enters PWM mode. During a release from heavy load to light load, active regulation turning on the N-channel switch minimizes the voltage overshoot.

Figure 6. Dynamic Voltage Positioning

#### 7.3.5 Soft Start

The two converters have an internal soft-start circuit that limits the inrush current during start-up. During soft start, control of the output-voltage ramp-up is as shown in Figure 7.

Figure 7. Soft Start

#### 7.3.6 100% Duty-Cycle Low-Dropout Operation

The converters offer a low input-to-output voltage difference while still maintaining operation with the use of the 100% duty-cycle mode. In this mode, the P-channel switch is constantly on. This operational mode is useful in battery-powered applications to achieve longest operation time by taking full advantage of the whole battery voltage range, (that is, the minimum input voltage to maintain regulation depends on the load current and output voltage) and can be calculated as:

$$V_{I}(min) = V_{O}(max) + I_{O}(max) \times (r_{DS(on)}(max) + R_{L})$$

where

- I<sub>0</sub> max = maximum output current plus inductor ripple current

- r<sub>DS(on)</sub> max = maximum P-channel switch r<sub>DS(on)</sub>

- R<sub>L</sub> = dc resistance of the inductor

- V<sub>o</sub> (max) = nominal output voltage plus maximum output-voltage tolerance

7.3.7 Undervoltage Lockout

The undervoltage-lockout circuit prevents the device from malfunctioning at low input voltages and from excessive discharge of the battery, and disables all internal circuitry. The undervoltage-lockout threshold, sensed at the  $V_{CC}$  pin, is typically 1.8 V, maximum 2 V.

#### 7.3.8 Mode Selection

The MODE pin allows mode selection between forced PWM mode and power-save mode for both converters. Connecting this pin to GND enables the automatic PWM and power-save mode of operation. The converters operate in fixed-frequency PWM mode at moderate-to-heavy loads and in the PFM mode during light loads, maintaining high efficiency over a wide load-current range.

Pulling the MODE pin high forces both converters to operate constantly in the PWM mode even at light load currents. The advantage is the converters operate with a fixed frequency that allows simple filtering of the switching frequency for noise-sensitive applications. In this mode, the efficiency is lower compared to the power-save mode during light loads. For additional flexibility, it is possible to switch from power-save mode to forced-PWM mode during operation. This allows efficient power management by adjusting the operation of the converters to the specific system requirements.

#### 7.3.9 Enable

To start up each converter independently, the device has a separate enable pin for each DC-DC converter and for each LDO. If EN\_DCDC1, EN\_DCDC2, EN\_LDO1, EN\_LDO2, EN\_LDO3, or EN\_LDO4 is set to high, the corresponding converter starts up with soft start as previously described.

#### Feature Description (continued)

Pulling the enable pin low forces the device into shutdown, with a shutdown quiescent current as defined in the electrical characteristics. In this mode, the P- and N-Channel MOSFETs turn off, and the entire internal control circuitry switches off. If disabled, internal  $350-\Omega$  resistors pull the outputs of the LDOs low, actively discharging the output capacitor. Proper operation requires termination of the enable pins. Do not leave them unconnected.

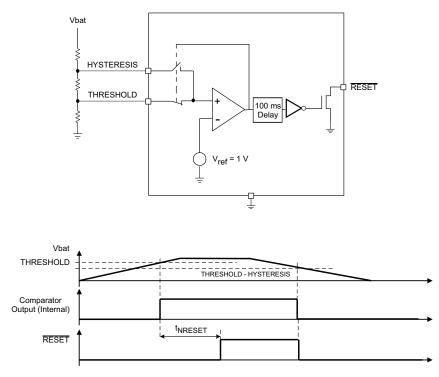

### 7.3.10 **RESET**

The device contains circuitry that can generate a reset pulse for a processor with a 100-ms delay time. The device senses the input voltage for a comparator at the THRESHOLD pin. When the voltage exceeds the threshold, the output goes high with a 100-ms delay time. An external resistor connected to the HYSTERESIS input defines the hysteresis. This circuitry is functional as soon as the supply voltage at  $V_{CC}$  exceeds the undervoltage-lockout threshold. The TPS65051-Q1 device has a shutdown current (all DC-DC converters and LDOs are off) of 9  $\mu$ A.

#### 7.3.11 Short-Circuit Protection

All outputs are short-circuit protected with a maximum output current as defined in the *Electrical Characteristics*.

#### 7.3.12 Thermal Shutdown

As soon as the junction temperature,  $T_J$ , exceeds 150°C (typically) for the DC-DC converters, the device goes into thermal shutdown. In this mode, the P- and N-channel MOSFETs turn off. The device continues its operation when the junction temperature falls below the thermal shutdown hysteresis again. A thermal shutdown for one of the DC-DC converters disables both converters simultaneously.

The thermal shutdown temperature for the LDOs is typically 140°C. Therefore, an LDO used to power an external voltage never heats up the chip high enough to turn off the DC-DC converters. If one LDO exceeds the thermal shutdown temperature, all LDOs turn off simultaneously.

#### **Feature Description (continued)**

#### 7.3.13 Low Dropout Voltage Regulators

The design of the low-dropout voltage regulators allows them to operate well with small ceramic input and output capacitors. They operate with input voltages down to 1.5 V. The LDOs offer a maximum dropout voltage of 400 mV (LDO1) and 280 mV (LDO2, LDO3, and LDO4) at rated output current. Each LDO supports a current-limit feature. The EN\_LDO1, ENLDO2, EN\_LDO3, and EN\_LDO4 pins enable the LDOs. The use of external resistor dividers sets the output voltage of the LDOs.

## 7.4 Device Functional Modes

#### 7.4.1 Power-Save Mode

The TPS65051-Q1 device is either in the ON or the OFF mode. The OFF mode is entered when the voltage on  $V_{CC}$  is below the UVLO threshold of 1.8 V (typically). When the voltage at the  $V_{CC}$  pin is higher than UVLO, the device enters ON mode. In the ON mode, the converters and LDOs are available for use.

Setting the MODE pin to 0 enables the power-save mode. If the load current decreases, the converters enter the power-save mode of operation automatically. During power-save mode, the converters operate with reduced switching frequency in PFM mode, and with a minimum quiescent current to maintain high efficiency. The converters position the output voltage 1% above the nominal output voltage. This voltage-positioning feature minimizes voltage drops caused by a sudden load step.

To optimize the converter efficiency at light load, the TPS65051-Q1 device monitors average current. If in PWM mode, the inductor current remains below a certain threshold, then the device enters power-save mode. Use Equation 2 to calculate the average output current threshold to enter PFM mode. Use Equation 3 to calculate the average output current threshold to leave PFM mode.

$$I_{(PFM_enter)} = \frac{VINDCDC}{32 \Omega}$$

(2)

$$I_{(PSMDCDC_leave)} = \frac{VINDCDC}{24 \Omega}$$

(3)

During power-save mode, a comparator monitors the output voltage. As the output voltage falls below the skipcomparator (skip comp) threshold, the P-channel switch turns on, and the converter effectively delivers a constant current. If the load is below the delivered current, the output voltage rises until it crosses the skip comp threshold again; then all switching activity ceases, reducing the quiescent current to a minimum until the output voltage has dropped below the threshold. If the load current is greater than the delivered current, the output voltage falls until it crosses the skip-comparator-low (skip comp low) threshold set to 1% below nominal  $V_0$ ; then the device exits power-save mode, and the converter returns to the PWM mode.

These control methods reduce the quiescent current to 12  $\mu$ A per converter and the switching frequency to a minimum, achieving the highest converter efficiency. The PFM mode operates with low output-voltage ripple. The ripple depends on the comparator delay and the size of the output capacitor; increasing capacitor value decreases the output ripple voltage.

Disable the power-save mode by driving the MODE pin high. In forced-PWM mode, both converters operate with fixed-frequency PWM mode regardless of the load.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

This device integrates two step-down converters and four LDOs, which can be used to power the voltage rails needed by a processor or any other application. The power management IC (PMIC) can be controlled through the ENABLE and MODE pins or sequenced from the VIN using RC delay circuits. A logic output (RESET) provides the application processor or load a logic signal indicating power good or reset.

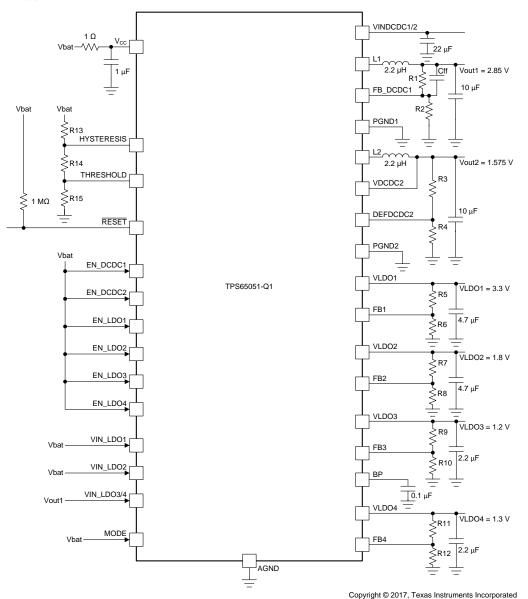

#### 8.2 Typical Application

Figure 9. Typical Application Schematic

### Typical Application (continued)

#### 8.2.1 Design Requirements

Table 1 lists the design requirements for this example.

| PARAMETER                     | VALUE        |  |  |  |  |  |  |

|-------------------------------|--------------|--|--|--|--|--|--|

| DCDC1 and DCDC2 input voltage | 2.5 V to 6 V |  |  |  |  |  |  |

| DCDC1 output voltage          | 2.85 V       |  |  |  |  |  |  |

| DCDC1 output current          | 1 A          |  |  |  |  |  |  |

| DCDC2 output voltage          | 1.575 V      |  |  |  |  |  |  |

| DCDC2 output current          | 600 mA       |  |  |  |  |  |  |

| LDO1 output voltage           | 3.3 V        |  |  |  |  |  |  |

| LDO1 output current           | 400 mA       |  |  |  |  |  |  |

| LDO2 output voltage           | 1.8 V        |  |  |  |  |  |  |

| LDO2 output current           | 400 mA       |  |  |  |  |  |  |

| LDO3 output voltage           | 1.2 V        |  |  |  |  |  |  |

| LDO3 output current           | 200 mA       |  |  |  |  |  |  |

| LDO4 output voltage           | 1.3 V        |  |  |  |  |  |  |

| LDO4 output current           | 200 mA       |  |  |  |  |  |  |

|                               |              |  |  |  |  |  |  |

#### Table 1. Design Parameters

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Output-Voltage Setting

#### 8.2.2.1.1 Converter 1 (DCDC1)

An external resistor network can set the output voltage of converter 1. Calculate the output voltage using Equation 4,

$$V_{O} = V_{ref} \times \left(1 + \frac{R1}{R2}\right)$$

where

```

• the internal reference voltage, V_{ref}, is 0.6 V

```

(4)

TI recommends setting the total resistance of R1 + R2 to less than 1 M $\Omega$ . The resistor network connects to the input of the feedback amplifier, therefore requiring a small feed-forward capacitor in parallel with R1. A typical value of 47 pF is sufficient.

#### 8.2.2.1.2 Converter 2 (DCDC2)

The adjustable output voltage is defined with external resistor network on the DEFDCDC2 pin.

Calculation of the adjustable output voltage is similar to that for the DCDC1 converter. TI recommends setting the total resistance of R3 + R4 to less than 1 M $\Omega$ . Route the DEFDCDC2 line separate from noise sources, such as the inductor or the L2 line. Connect the VDCDC2 line directly to the output capacitor. As VDCDC2 is the sense pin for the output of L2, there is no need for a feedforward capacitor in conjunction with R3.

Use an external resistor divider at DEFDCDC2 as shown in Figure 10.

Figure 10. External Resistor Divider

$V_{(DEFDCDC2)} = 0.6 V$

$$V_{O} = V_{(DEFDCDC2)} \times \frac{R3 + R4}{R4} \qquad R3 = R4 \times \left(\frac{V_{O}}{V_{(DEFDCDC2)}}\right) - R4$$

(5)

See Table 2 for typical resistor values:

**Table 2. Typical Resistor Values**

| OUTPUT VOLTAGE | R3     | R4     | NOMINAL VOLTAGE | Typical CFF |

|----------------|--------|--------|-----------------|-------------|

| 3.3 V          | 680 kΩ | 150 kΩ | 3.32 V          | 47 pF       |

| 3 V            | 510 kΩ | 130 kΩ | 2.95 V          | 47 pF       |

| 2.85 V         | 560 kΩ | 150 kΩ | 2.84 V          | 47 pF       |

| 2.5 V          | 510 kΩ | 160 kΩ | 2.51 V          | 47 pF       |

| 1.8 V          | 300 kΩ | 150 kΩ | 1.8 V           | 47 pF       |

| 1.6 V          | 200 kΩ | 120 kΩ | 1.6 V           | 47 pF       |

| 1.5 V          | 300 kΩ | 200 kΩ | 1.5 V           | 47 pF       |

| 1.2 V          | 330 kΩ | 330 kΩ | 1.2 V           | 47 pF       |

TPS65051-Q1

SLVSBJ1B-SEPTEMBER 2012-REVISED JANUARY 2017

### 8.2.2.2 Output Filter Design (Inductor and Output Capacitor)

#### 8.2.2.2.1 Inductor Selection

The two converters operate with a 2.2- $\mu$ H output inductor. A designer can use larger or smaller inductor values to optimize the performance of the device for specific operation conditions. The selected inductor must be rated for its dc resistance and saturation current. The dc resistance of the inductance directly influences the efficiency of the converters. Therefore, select an inductor with lowest dc resistance for highest efficiency. The minimum inductor value is 1.5  $\mu$ H, but the circuit requires an output capacitor of 22  $\mu$ F minimum in this case. For an output voltage above 2.8 V, TI recommends an inductor value of 3.3  $\mu$ H minimum. Lower values result in an increased output-voltage ripple in PFM mode.

Equation 6 calculates the maximum inductor current under static load conditions. The saturation-current rating of the inductor should be higher than the maximum inductor current as calculated with Equation 6. This recommendation is because during heavy load transient the inductor current rises above the calculated value.

$$\Delta I_{L} = V_{O} \times \frac{1 - \frac{V_{O}}{V_{I}}}{L \times f} \qquad I_{L}(\max) = I_{O}(\max) + \frac{\Delta I_{L}}{2}$$

where

- f = Switching frequency (2.25-MHz typical)

- L = Inductor value

- $\Delta I_{L}$ = Peak-to-peak inductor ripple current

- I<sub>1</sub> max = Maximum inductor current

The highest inductor current occurs at maximum V<sub>I</sub>. Open-core inductors have a soft saturation characteristic, and they can normally handle higher inductor currents versus a comparable shielded inductor.

A more-conservative approach is to select the inductor current rating just for the maximum switch current of the corresponding converter. Give consideration to the difference in the core material from inductor to inductor, which has an impact on the efficiency, especially at high switching frequencies. See Table 3 and the typical applications for possible inductors.

| INDUCTOR TYPE | INDUCTOR VALUE | SUPPLIER  |

|---------------|----------------|-----------|

| LPS3010       | 2.2 μΗ         | Coilcraft |

| LPS3015       | 3.3 μΗ         | Coilcraft |

| LPS4012       | 2.2 μΗ         | Coilcraft |

| VLF4012       | 2.2 μΗ         | TDK       |

**Table 3. Tested Inductors**

#### 8.2.2.2.2 Output-Capacitor Selection

The advanced fast-response voltage-mode control scheme of the two converters allows the use of small ceramic capacitors with a value of  $22-\mu F$  (typical), without having large output-voltage undershoots and overshoots during heavy load transients. TI recommends ceramic capacitors having low ESR values, which result in the lowest output-voltage ripple.

If ceramic output capacitors are used, the capacitor RMS ripple current rating always meets the application requirements. For completeness, the RMS ripple current is calculated as:

$$I_{(RMSCout)} = V_0 \times \frac{1 - \frac{V_0}{V_1}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

(7)

(6)

At nominal load current, the inductive converters operate in PWM mode, and the overall output voltage ripple is the sum of the voltage spike caused by the output-capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

www.ti.com

$$\Delta V_{O} = V_{O} \times \frac{1 - \frac{V_{O}}{V_{I}}}{L \times f} \times \left(\frac{1}{8 \times C_{O} \times f} + ESR\right)$$

(8)

where the highest output voltage ripple occurs at the highest input voltage V<sub>I</sub>.

At light load currents, the converters operate in power-save mode and the output-voltage ripple depends on the output-capacitor value. The internal comparator delay and the external capacitor set the output-voltage ripple. The typical output-voltage ripple is less than 1% of the nominal output voltage.

#### 8.2.2.2.3 Input-Capacitor Selection