# **Digital Dual Synchronous-Buck Power Driver**

Check for Samples: UCD7242

## **FEATURES**

- Fully Integrated Power Switches With Drivers for Dual Synchronous Buck Converters

- Full Compatibility With TI Fusion Digital Power Supply Controllers, Such as the UCD92xx Family

- Wide Input Voltage Range: 4.75 V to 18 V Operational Down to 2.2 V Input With an External Bias Supply

- Up to 10A Output Current per Channel

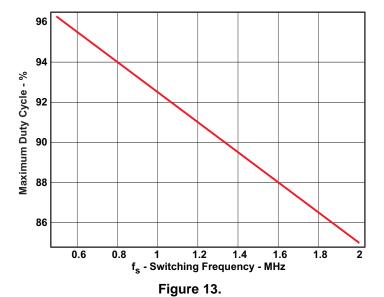

- Operational to 2 MHz Switching Frequency

- High Side Current Limit With Current Limit Flag

- Onboard Regulated 6 V Driver Supply From V<sub>IN</sub>

- Thermal Protection

- Temperature Sense Output Voltage Proportional to Chip Temperature

- UVLO and OVLO Circuits Ensure Proper Drive Voltage

- Rated From –40°C to 125°C Junction Temperature

- RoHS Compliant

- Accurate On-Die Current Sensing (±5%)

## **APPLICATIONS**

- Digitally-Controlled Synchronous-Buck Power Stages

- High Current Dual-Phase VRM/EVRD Regulators for Desktop, Server, Telecom and Notebook Processors

## **DESCRIPTION**

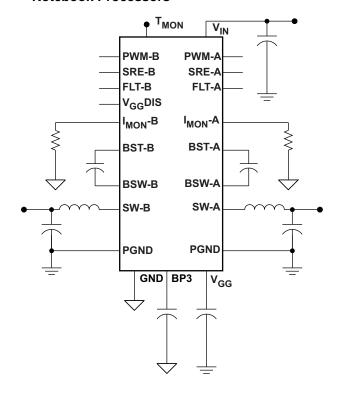

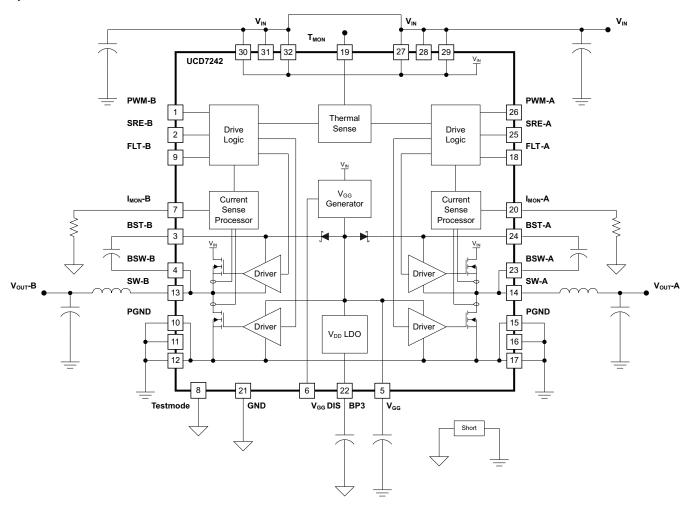

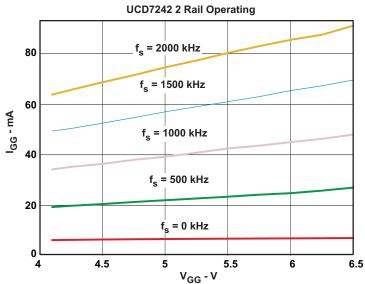

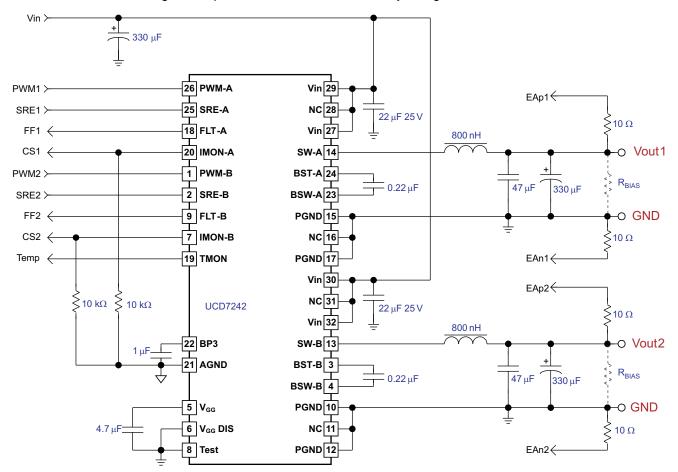

The UCD7242 is a complete power system ready to drive two independent buck power supplies (see Figure 1). High side MOSFETs, low side MOSFETs, drivers, current sensing circuitry and necessary protection functions are all integrated into one monolithic solution to facilitate minimum size and maximum efficiency. Driver circuits provide high charge and discharge current for the high-side NMOS switch and the low-side NMOS synchronous rectifier in a synchronous buck circuit. The MOSFET gates are driven to +6.25 V by an internally regulated  $V_{\rm GG}$  supply. The internal  $V_{\rm GG}$  regulator can be disabled to permit the user to supply an independent gate drive voltage. This flexibility allows a wide power conversion input voltage range of 2.2V to 18V. Internal under voltage lockout (UVLO) logic ensures  $V_{\rm GG}$  is good before allowing chip operation.

The synchronous rectifier enable (SRE) pin controls whether or not the low-side MOSFET is turned on when the PWM signal is low. When SRE is high the part operates in continuous conduction mode for all loads. In this mode the drive logic block uses the PWM signal to control both the high-side and low-side gate drive signals. Dead time is also optimized to prevent cross conduction. When SRE is low, the part operates in discontinuous conduction mode at light loads. In this mode the low-side MOSFET is always held off.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION (CONTINUED)**

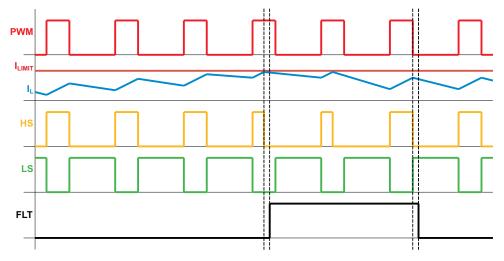

On-board comparators monitor the current through the high side switch to safeguard the power stage from sudden high current loads. Blanking delay is set for the high side comparator to avoid false reports coincident with switching edge noise. In the event of an over-current fault, the high-side FET is turned off and the Fault Flag (FLT) is asserted to alert the controller.

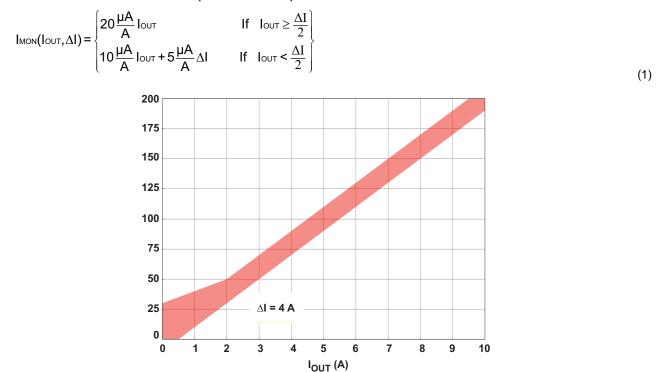

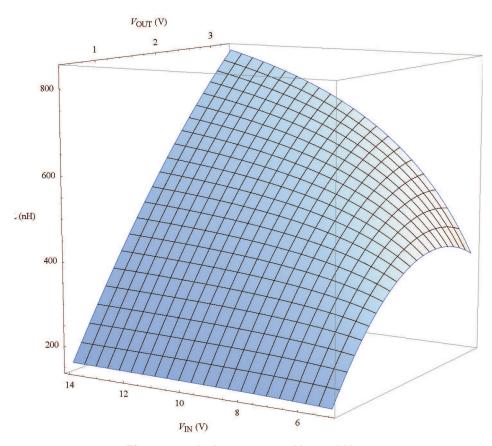

MOSFET current is measured and monitored by a precision integrated current sense element. This method provides an accuracy of  $\pm 5\%$  over most of the load range. The amplified signal is available for use by the controller on the  $I_{MON}$  pin.

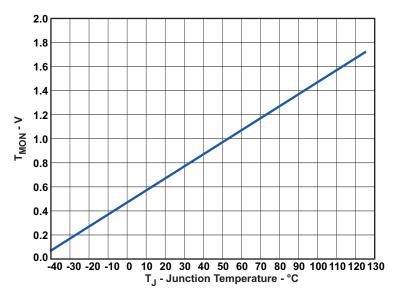

An on-chip temperature sense converts the die temperature to a voltage at the  $T_{MON}$  pin for the controller's use. If the die temperature exceeds 170°C, the temperature sensor initiates a thermal shutdown that halts output switching and sets the FLT flag. Normal operation resumes when the die temperature falls below the thermal hysteresis band.

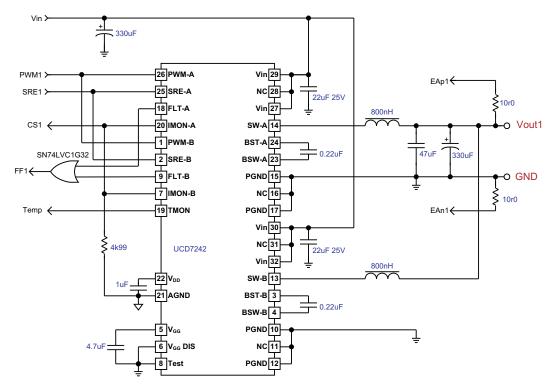

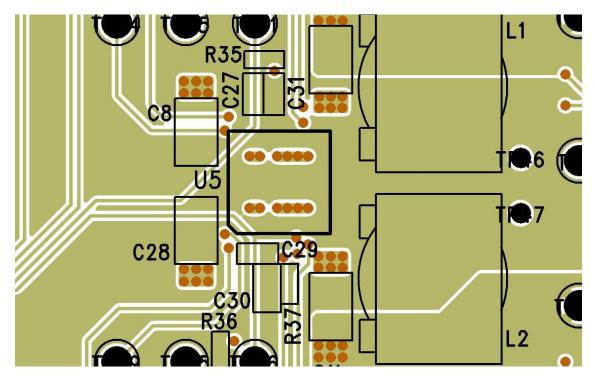

Figure 1. Typical Application Circuit and Block Diagram

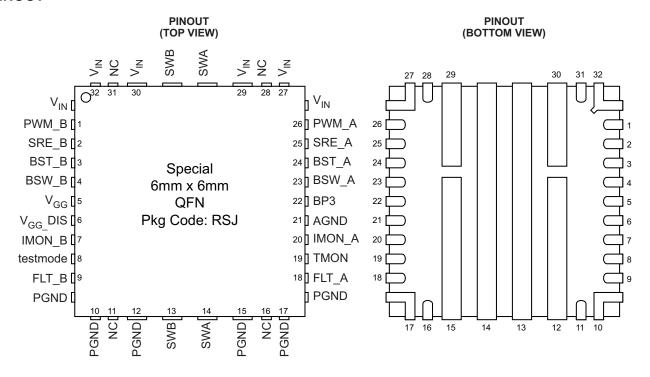

#### **ORDERING INFORMATION**

| OPERATING<br>TEMPERATURE<br>RANGE, T <sub>A</sub> | EMPERATURE PIN COUNT ORI |             | SUPPLY       | PACKAGE | TOP SIDE MARKING |  |

|---------------------------------------------------|--------------------------|-------------|--------------|---------|------------------|--|

| 40°C to 405°C                                     | 22 nin                   | UCD7242RSJR | Reel of 2500 | OFN     | LICD7040         |  |

| –40°C to 125°C                                    | 32-pin                   | UCD7242RSJT | Reel of 250  | QFN     | UCD7242          |  |

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                             | RATING              | VALUE             |                |    |

|---------------------------------------------|---------------------|-------------------|----------------|----|

| VIN                                         | Supply voltage      |                   | -0.3 to 20     | V  |

| DOT                                         | Deetweltere         | DC                | -0.3 to SW + 7 | V  |

| BST                                         | Boot voltage        | AC <sup>(2)</sup> | 34             | V  |

| V <sub>GG</sub> , V <sub>GG</sub> _DIS      | Gate supply volta   | ige .             | 7              | V  |

| BP3                                         | Logic supply volta  | age               | 4              | V  |

| 014/ 5014/                                  | Out the bound to me | DC                | –2 to VIN + 1  | V  |

| SW, BSW                                     | Switch voltage      | AC <sup>(2)</sup> | 34             | V  |

| TMON, IMON, Testmode                        | Analog outputs      | •                 | -0.3 to 3.6    | V  |

| PWM-A, PWM-B, SRE-A,<br>SRE-B, FLT-A, FLT-B | Digital I/O's       |                   | -0.3 to 5.5    | V  |

| T <sub>J</sub>                              | Junction tempera    | ture              | -55 to 150     | °C |

| T <sub>stg</sub>                            | Storage tempera     | ture              | -55 to 150     | °C |

| ESD rating                                  | HBM: Human Bo       | dy model          | 2000           | V  |

|                                             | CDM: Charged d      | evice model       | 500            | V  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. Consult company packaging information for thermal limitations and considerations of packages.

## **DISSIPATION RATINGS (TYPICAL)**

| PACKAGE | AIRFLOW (LFM)          | R <sub>0JA</sub> TI EVM BOARD <sup>(1)</sup> | POWER RATING<br>T <sub>A</sub> = 25°C | POWER RATING<br>T <sub>A</sub> = 85°C |

|---------|------------------------|----------------------------------------------|---------------------------------------|---------------------------------------|

|         | 0 (natural convection) | 19.1°C/W                                     | 5.2 W                                 | 2.1 W                                 |

| RSJ     | 200                    | 15.1°C/W                                     | 6.6 W                                 | 2.6 W                                 |

|         | 400                    | 13.4°C/W                                     | 7.5 W                                 | 3.0 W                                 |

<sup>(1)</sup> Data taken using TI EVM.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|          |                                                             | MIN  | TYP | MAX  | UNIT |

|----------|-------------------------------------------------------------|------|-----|------|------|

| $V_{IN}$ | Power input voltage (internally generated V <sub>GG</sub> ) | 4.75 | 12  | 18   | V    |

| $V_{IN}$ | Power input voltage (externally generated V <sub>GG</sub> ) | 2.2  | 12  | 18   | V    |

| $V_{GG}$ | Externally supplied gate drive voltage                      | 4.75 | 6.2 |      | V    |

| $T_{J}$  | Operating junction temperature range                        | -40  |     | 125  | °C   |

| fs       | Switching frequency                                         | 300  | 750 | 2000 | kHz  |

<sup>(2)</sup> AC levels are limited to within 5 ns.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V; 1 $\mu$ F from BP3 to GND, 0.22 $\mu$ F from BST to BSW, 4.7 $\mu$ F from  $V_{GG}$  to PGND,  $T_A$  =  $T_J$  = -40°C to 125°C (unless otherwise noted)

|                    | ise noted)                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

|--------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                    | METER                                                         | TEST CONDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MIN  | TYP  | MAX  | UNIT |

| SUPPL              | LY SECTION                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

|                    | Supply surrent                                                | Outputs not switching, $V_{IN} = 2.2 \text{ V}$ , PWM(INH) = LOW, SRE(INL) = HIGH, $V_{GG}$ _DIS = HIGH, $V_{GG}$ = 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 6    |      | mA   |

|                    | Supply current                                                | Outputs not switching, V <sub>IN</sub> = 18 V,<br>PWM(INH) = LOW, SRE(INL) = HIGH,<br>V <sub>GG</sub> _DIS = LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 6    |      | mA   |

| GATE               | DRIVE UNDER VOLTAGE LOCKOUT                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

| $V_{GG}$           | UVLO ON                                                       | BP3 Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 4.0  |      | V    |

|                    | UVLO OFF                                                      | BP3 Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 3.8  |      | V    |

|                    | UVLO hysteresis                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 200  |      | mV   |

| V <sub>GG</sub> SI | JPPLY GENERATOR                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

| $V_{GG}$           |                                                               | V <sub>IN</sub> = 7 to 18 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.2  | 6.25 | 6.8  | V    |

|                    | V <sub>GG</sub> drop out                                      | V <sub>IN</sub> = 4.75 to 7 V, I <sub>VGG</sub> < 50 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |      | 600  | mV   |

| BP3 S              | UPPLY VOLTAGE                                                 | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |      |      |

|                    | BP3                                                           | I <sub>DD</sub> = 0 to 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.15 | 3.3  | 3.45 | V    |

| INPUT              | SIGNAL (PWM, SRE)                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |      |      |

| V <sub>IH</sub>    | Positive-going input threshold voltage                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 2.1  | 2.3  | V    |

| V <sub>IL</sub>    | Negative-going input threshold voltage                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1    | 1.2  |      | V    |

|                    | 3-state Condition                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.4  |      | 1.9  | V    |

| t <sub>HLD R</sub> | 3-state hold-off time                                         | V <sub>PWM</sub> = 1.65 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 275  |      | ns   |

|                    |                                                               | V <sub>PWM</sub> = 5.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 133  |      |      |

| $I_{PWM}$          | Input current                                                 | V <sub>PWM</sub> = 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 66   |      | μA   |

| . ****             | ·                                                             | V <sub>PWM</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | -66  |      |      |

|                    |                                                               | V <sub>SRE</sub> = 5.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 1    |      |      |

| I <sub>SRE</sub>   | Input current                                                 | V <sub>SRE</sub> = 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 1    |      | μA   |

| OILL               | ·                                                             | V <sub>SRE</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 1    |      |      |

| V <sub>GG</sub> DI | SABLE (V <sub>GG</sub> _DIS)                                  | SIL -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |      |

| - 00 -             | Input resistance to AGND                                      | V <sub>GG</sub> _DIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50   | 100  | 150  | kΩ   |

|                    | Threshold                                                     | 19919                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.35 |      | 1.6  | V    |

|                    | Hysteresis                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 550  |      | mV   |

| FAUL1              | FLAG (FLT)                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |

|                    | FLT Output High Level                                         | I <sub>OH</sub> = 2 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.7  |      |      | V    |